Signature redacted of Author*.

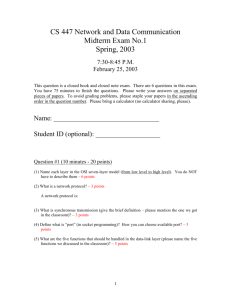

advertisement

A THREE-DIMENSIGNAL

COMIPUTER DISPLAY

by

Edwin P.

Berlin,

Jr.

Submitted in Partial Fulfillment

of the Requirements for the

Degree of Bachelor of Science

at the

IMassachusetts Institute of Technology

May, 1978

Signature

of Author*.

Signature redacted

Department of Electrical Engineering

and Computer Science, May 19, 1978

Signature redacted

Certified by.........tu

e r.a..

ThessSSuperviso~r

Signature redacted

Accepted by..........

S. . . *.......

Chairman, Departmental Committee on Theses

C opyright

Edwin P. Berlin, Jr.

Archives

JUN 8 1978

sp'I

'f t o 5 v

1978

9 9

MITLibraries

77 Massachusetts Avenue

Cambridge, MA 02139

http://Iibraries.mit.edu/ask

DISCLAIMER NOTICE

Due to the condition of the original material, there are unavoidable

flaws in this reproduction. We have made every effort possible to

provide you with the best copy available.

Thank you.

The images contained in this document are of the

best quality available.

2

-

-

A THREE -DIVIENSI ONAL COMPUTER DISPLAY

by

Edwin P. Berlin,

Jr.

Submitted to the Department of Electrical Engineering and

Computer Science on May 19, 1978 in partial fulfillment of

the requirements for the Degree of Bachelor of Science.

ABSTRACT

There are many applications where it would be

desirable to have a device capable of generating a true

three-dimensional display of high resolution, where the

image may be genenated by computer or some suitable

device.

A system is described in this paper for

producing such a display.

The basic method involves

rotating a flat imaging device,

such as an array of

light emitting diodes, about one edge so as to describe

a cylinder.

As the planar array rotates,

it displays

many successive cross-sections of the object to be

displayed in the cylinder.

Persistence of vision

allows an observer to combine these separate slices

into a complete three-dimensional object.

The device will be used with tomogtaphic scanners,

which are a new form of x-ray scanner which produces

complete three-dimensional information.

So far, there

has been no satisfactory method of displaying this

-

-3

information.

This paper deals with the considerations leading

to the design of the digital circuitry neccessary to

perform the functions required by such a display.

The

use of parallelism is important to keep the bandwidth

on any given channel manageable.

A prototype is currently

being built at the L1 .I.T. Innovation Center.

Name and Title of Thesis Supervisor:

David G. Jansson

Assistant Professor, Department of Aeronautics

and Astronautics

-

- 4

ACKNOWLEDGEMENT S

I would like to thank David Jansson and Isidor

Straus for their help and encouragement in this project.

- 5

.....

......

0 0. 0 0006000

.

ABSTRACT., ....

.4

ACKNOWLEDGEMENTS.........

.......

, .

......

.7

.

INTRODUCTION.....

2

THREE-DIMENSIONAL DISPLAY GENERAT ION

.8

SOME DEFINITION S.........

.10

A PRACTICAL DESIGN....,..

PARALLELISM . .

........

...

..

.

~...

BASIC ORGANIZATION.......

..

~

PifEMORY ORGANIZATION....

..........

TIMING...

..........

.

.17

0

.........

THE PROTOTYPE.,......****.

..........

.10

.....

~

...

.18

.26

.......

~

.28

.31

06

UPDATING THE MEMORY......

.41

..........

DATA TRANSFER RATE.......

.49

...

...

..

POWER ESTIMATES. .........

APPENDIX

APPENDIX

I...........

0

..........

w

.

.50

.51

.

CONCLUSION...........

.50

..........

II............

.

........

.59

..........

APPENDIX III.............

REFERENCES..... ...................................

.72

9 090*0 79

- 6

LIST OF FIGURES

FIGURE 1:

Three-Dimensional Display...... ........

FIGURE 2:

Subsets of the Display Space.....

.11

FIGURE 3:

Numbering of the Addres Is Space...

.12

FIGURE 4:

Mechanical Arrangement..

.14

FIGURE 5:

Line Dump Mode with LED Panel....

.19

FIGURE 6:

One Sided LED Panel..... ..

FIGURE 7:

Interlacing.

FIGURE 8:

Block Diagram...........

.......

FIGURE 9:

Memory Organization.....

666.....6.6

FIGURE 10: Timing.*.

.....

.a. .. ......

6.....6......

FIGURE 11: CCD Memory..............

. .

.S

9

.23

.25

O.........

.27

666

.29

.........

6

.32

.........

6

.33

FIGURE 12: Serial-Parallel Register s........

6

.34

.35

FIGURE 13: Panel and Drivers....,..

.........

FIGURE 14: Write Control Logic.....

....

FIGURE 15: Buffer Memory...........

.6.......

.37

FIGURE 16: Buffer Address Logic....

66..666666

.38

FIGURE 17: Serial Data Format......

....

FIGURE 18: Data Block Format.......

66..6.6.

FIGURE 19: Memory Update Timing......

6

.36

6....6

.42

6.....6

6

.42

-

-7

INTRODUCTION

There exists a need for a relatively economical

three-dimensional display device which can be interfaced

with a computer to provide a three-dimensional image

which may be changed with ease.

Such a display can

be used, for example, to present three-dimensional

x-ray information in the medical field as well as for

non-destructive testing.

This display could also be

used for such applicatins as exhibiting air traffic

control information and in the field of computer aided

design.

In all such uses, the need for continual

updating of information is often a requirement.

This,

combined with a need for high resolution dictates a

system with large memory and high data throughput.

In the Fall of 1975 I conceived of a method for

generating such a three-dimensional display.

A small

model was constructed to prove feasibility, and a patent

application has been filed.

at the YI.I.T.

A prototype is being built

Innovation Center, under the supervision

of Professor D. G. Jansson.

The application for which

this prototype was designed, to be used with tomographs,

or three-dimensional x-ray scanners, was decided primarily

by our source of funding.

This paper pertains to

considerations leading to the design of the digital

-

- 8

electronics required by this three-dimensional display.

THREE-DIMENSIONAL DISPLAY GENERATION

The basic idea is shown in FIGURE 1.

If a planar

array of light sources, visible from both sides of the

plane, is rotated about one edge of the array the

resulting locus is the volume of a cylinder.

forms a cylindrical coordinate system.

This

Any point in

the space, (r, z, e), within the cylinder may be illuminated

by lighting the point on the planar array specified

by r for the horizontal coordinate and z for the vertical

coordinate at the instant that the plane has rotated

through an angle e.

Thus the selected point in space

is flashing at a rate determined by the rotational

frequency of the array.

If this frequency is high

enough, persistence of vision makes the illumination

appear constant to an observer.

In a similar fashion,

any set of points may be illuminated simultaneously,

and each point may also present grey scale and color

information.

This system can provide a true three-dimensional

image of relatively high resolution.

An observer may

view the image from any direction, and the number of

light sources is far fewer than the number of points

in the display space.

-

- 9

I

V

00

0

0

0

0

00

00 0

00 00

00 000

0

-

9

I

FIGURE 1

Three-Dimensional Display

0

0

I

10

-

-

SOME DEFINITIONS

To aid further descriptions, refer to FIGURE 2

for names of subsets of the display space.

The region

described by holding e fixed and letting r and z vary

over all positive values within the display space is

It is the planar array at a single instant

a sector.

of time.

Similarly, a cylinder is described when r

is held constant and a plane is the locus when z is

held constant.

The intersection of a plane and a cylinder is

a circle, the intersection of a plane and a sector

is a row, and the intersection of a cylinder and a sector

is a column.

The intersection of a plane, cylinder

and a sector, that is, a single point, is called a

pixel (for picture element).

The set of all pixels

is a field.

There are finite numbers of sectors, cylinders

and planes, and they are numbered as depicted in FIGURE 3.

There are S sectors, C cylinders and P planes.

A PRACTICAL DESIGN

Some problems in designing a display such as

t1s immediately become apparent.

First, the planar

array of light sources will have some air resistance

and it is likely that the force at the edge of the array

-

- 11

(

N

/ I

it

/

1

I

/ i~ /1

1~

b) Cylinder

a) Sector

colurn

circlero

pixel

c) Plane

d) Circle, column,

row, and pixel.

-0

FIGURE 2

Subsets of the Display Space

-

- 12

sector ~

\

\\

(rcYl1

cy 0

0

-'sector0

Ci

cy'I

sector

b) cylinders

a) sectors

planeP_

p1 ane 1

FLANE a

c) planes-

FIGURE '3

Numbering of the Address Space

1

(cyll

C-1

-

- 13

would be enough to bend or break the array.

A solution

is to enclose the array in a transparent cylindrical

or bell-jar shaped cover which rotates along with the

array.

The outside of this cover is smooth and symmetrical;

it presents little drag as it spins.

Inside, the air

is confined to the enclosure and forms a static pressure

gradient;

there is little or no turbulence.

(See

FIGURE 4.)

Let us consider a display of reasonable resolution.

Let S=256, C=32 and P=64.

Let us also allow for a

four-bit grey scale (16 levels of intensity, no color

variation).

= 524288.

The number of pixels is SxCxP = 256x32x64

The number of bits required to specify an

image is over two million.

For the image to be free

from flicker, the rotational speed of the display can

not be much less than 30 RPS (revolutions per second.)

Thus, the data rate for even this modest size display

is roughly 60 million bits per second.

A larger display

would require a proportionally higher bandwith.

There are 2048 light sources on the array.

It

would not be feasible to have 2048 connections from a

stationary memory to the rotating array, each operating

at 30 KHz.

The only electrical connections between fixed

and rotating portions of the display system must be made

r

Transparent

cover

10043

10208

Planar

Array

0

F-

0

f ---

o

Circuitry

1007 B

r-F1

or100B

a

I0

0

LwI0II+

101113V

10003

IOki

SLIPRINGS

G

1

10116'

Light

Beam\00

1006 B

Motor

1I9

101 5E

IS

C OMPUTER

7

FIXED CONTROL

EL ECTR0CS

FIGURE 4

100'

Mechanical Arrangement

-

- 15

through sliprings, which are inherently noisy and not

capable of handling any useful bandwith.

The proposed

method for passing information to the rotating portions

of the display is via an infra-red light beam passing

through the motor shaft and concentric with the axis

of rotation of the array.

(Again, refer to FIGURE 4.)

The fixed electronics can modulate an IR LED (light

emitting diode) at a data rate of at least one to two

rHz.

The data is received by a phototransistor.

We need to display 60 million bits per second

and we have one channel which can carry only two million

bits per second.

If we do not need the ability to

display a completely different image each revolution

and can tolerate several seconds for replacing the

current image with a new one, then we can rotate enough

memory to contain one entire image so that no data need

be transferred to the rotating system while the image

in memory is to be displayed.

When the image is to be

changed, data may be sent serially over the slow (2 MHz)

channel and loaded into the memory.

Current technology

allows us to cnstruct a two million bit memory with

only 32 integrated circuit packages.

All power to

operate the memory, display and associated timing and

control logic is supplied through two sliprings concentric

16

-

-

with the motor shaft.

Now the rotating portion of the display requires

only one more piece of information to generate stable

images:

that is a place to set an origin.

The rotating

electronics must be synchonized to the speed of the

motor and a fixed reference point so that sector 0 is

always in the same physical place and successive sectors

are spaced correctly through one revolution.

This

information is provided by an opto-interrupter (a light

wmitting diode paired with a phototransistor and mounted

so as to produce a pulse when the beam is interrupted)

mounted at the edge of the rotating system.

Once every

revolution, a fixed plate interrupts the beam, causing

the opto-interrupter to generate a pulse when the planar

array is in one specific position.

is generated every revolution.

Exactly one pulse

This signal is all that

is needed by the rotating electronics for synchronization.

What should be used for the planar array of light

sources?

A cathode-ray tube is impractical for several

reasons.

A single electron gun and deflection system

cannot handle the bandwith required by this display.

Also it is difficult and unsafe to rotate a CRT at such

high speeds.

display.

One possible array is a planar plasma

This is a flat structure consisting of two

17

-

-

this plates of glass seperated by a small distance,

filled with a gas such as neon, and sealed.

The inside

surface of one plate is coated with many parallel,

horizontal, transparent conductors.

The inside surface

of the other plate is coated with vertical conductors,

forming a rectangular matrix.

By applying a voltage

to one horizontal and one vertical electrode, the gas

at the intersection can be ionized and light is generated.

Experiments I performed showed that a plasma cell can

be ignited in less than one microsecond and light

intensity is very nearly linear with applied current.

The disadvantage of a plasma panel is the need for a

high voltage supply and high voltage driving circuitry.

A better alternative is to use a dense array of

visible light emitting diodes.

LEDs are very fast,

comparatively inexpensive, and they require low voltages.

They can be pulsed with high current at low duty cycles

and are very bright.

Large arrays of LEDs are available

with linear densities of up to 50 dots per inch.

LED

arrays are only visible from one side of the panel.

PARALLELISM

If out planar array were scanned sequentially,

one pixel at a time, we would have to scan at least

at a rate of 15 million pixels per second.

But when

-

- 18

the array is arranged in a matrix we can produce an

entire row or column in parallel.

This is called line dump mode.

(See FIGURE

5.)

If we display rows

in parallel and scan columns sequentially, we have

about two microseconds to present a single row.

This

is an acceptable time.

It is important to use parallelism as much as

possible in the design of this display to keep the

data rates from getting out of hand.

The memory can

operate as a parallel system by using wide words, perhaps

128 bits wide.

Proper memory organization is also

important.

THE PROTOTYPE

The display will be used with the tomographic

x-ray scanner to provide a three-dimensional image of

any part of a patient's body, showing internal organs

and other variations in density.

Tomography, already

a computerized process, produces digitized images which

are planar cross-sections through a portion (for example,

the head) of the patient being scanned.

If successive

slices are displayed one on top of each other, the entire

region scanned may be displayed. The three-dimensional

image will look very much like an x-ray view because

although near objects in the region are visible, objects

19

-

-

ro 63

Entire

row

displayed

at once.

Th

I

P~

Rows scanned

sequentially

A :---4~&Qj

I

-row

All co

s rsm ven inte

FIGURE 5

Line Dump 'ode with LED Panel

0

20

-

-

farther from the observer are not obstructed; they

are seen through the near image.

may be performed on the image.

Additional processing

The field may be rotated,

translated, scaled, or unwanted regions may be removed.

For this application, good resolution is required.

It would be acceptable to allow up to one minute time

to load a new image into the display memory, since the

image will not be changed often.

We would like to build a display with a resolution

of 256 sectors, 256 planes,, 128 cylinders and a four bit

grey scale.

It seemed wise to start with a smaller

display for our first prototype so that the knowledge

we gain from building the first prototype will help us

better build the second, pre-production prototype.

This

first prototype, then, has 256 sectors, 64 planes, 32

cylinders and a four bit grey scale.

This requires a

two million bit memory (221 bits).

The motor we are using (because it is what we

have) rotates at 60 RPS.

It is a synchronous motor

from a disk drive and very stable.

The planar array is a panel of red LEDs made by

Integrated Microsystems, Inc.

square, 32 dots per inch.

by 64 LEDs.

The panel is two inches

This makes the array 64 LEDs

(Vce Appendix I.)

21

-

-

Since all the display electronics must rotate, it

is important to keep size and weight down to a minimum.

For this rason, 64K bit charge-coupled device (CCD)

shift register memories were chosen.

These devices

store 65536 bits in a standard 16 pin dual inline

package (DIP).

the memory.

32 of these packages are required for

Thep is no denser read/write memory available,

and the next density under 64K is 16K which would require

128 DIPs.

The CCD memory is inherently serial;

not be accessed randomly.

data can

Available CCDs, however tend

to be arranged as a number of short shift register

loops, each loop being addressable.

Thus there is some

flexibility with the order in which data may be shifted

out of memory.

The LED panel is visible from only one side.

If it is rotated about one edge, an observer will only

be able to see one half of the three-dimensional image

at a time.

This problem could be solved, conceivably,

by mounting two 32 by 64 LED panels back-to-back.

If

the same image information is sent simultaneously to

both panels as the pair is rotated, the effect is the

same as that of a transparent panel; one of the two

panels will always be visible.

Such a planar array will

have an appreciable thickness.

A better solution is

to rotate a one-sided 64 by 64 LED panel about a line

the panel forms a diameter of the

through its center;

cqindrical field.

When the right half of the panel

is displaying one side of sector 0 (for example) the

left half of the panel is displaying a side of a sector

opposite sector0 .

After exactly one half a revolution

the left half of the panel will be where the right half

was (sector0 ) but the visible side of the panel will be

facing the other way.

In this way the pixels from

every sector will be visible from any direction.

(FIGURE 6

shows the panel at two instants in time one half revolution,

or 1800 apart.)

The two halves of hte panel now each need to

carry the total display information every revolution.

This has doubled the data rate for the device.

If

we have 256 sectors, then for every sector we need to

retrieve from memory the data for two sectors.

are at sector0 and sector 1 2 8 .)

long shift register.

(Say we

But the memory is one

We do not have available a tap

in the middle of the shift register because the CCDs

are on a single integrated circuit.

interlace.

What we can do is

23

-

-

.................

sector 1 28

sector0

sector

sector1 2 8

a)Start of revolution

FIGURE 6

One Sided LED Panel

b) 1800 later

0

-

- 24

To interlace, we do not update both halves of

the LED panel at the same time.

(See FIGURE 7.)

FIGURE 7a represents one rotation of the right half

of the panel.

(The right half is defined as the right-

hand side when the panel image is visible to an observer.

Note that when the right half of the panel is on the

observer's left, meaning to the left of the axis of

rotation of the display, then that side of the panel

is not visible to that observer.)

FIGURE 7b represents

the simultaneous rotation of the left half of the panel.

(For clarity, only 12 sectors are shown.)

A solid line

represents an image being presented to the panel and

a dotted line indicates when that half of the panel

is not being illuminated.

When the right half is positioned

at sector0 , the left half is positioned at sector 6 ; the

right half is displaying, the left half is dark.

Next, when the right half is positioned at sector1 , the

left half is positioned at sector 7 ; now the right

half panel is dark and the left half is illuminated.

One can see that for this entire revolution, the right

half panel displays all the even numbered sectors and

the left half displays all the odd numbered sectors.

On the next revolution, the sequencing is reversed

and the right half panel displays all the odd numbered

-

- 25

6

Ci

8

)

g4n

a) Right half of panel

FIGURE 7

Interlacing

10

b) Left half of panel

-

- 26

sectors and the left half displays all the even numbered

sectors.

It now takes two revolutions to generate an

entire field, so interlacing has the added benefit

of halving the neccessary data rate.

BASIC ORGANIZATION

Refer to the block diagram of FIGURE 8.

All

functions within the display are synchronized by the

block labeled timing, which is driven by the optointerrupter which generates one pulse evey revolution

of the display.

The timing logic sequences through

each of the 64 horizontal rows of the LED panel, supplying

current to them, one row at a time.

As this happens,

data are shifted out of the shift register memory, and

presented to 64 four-bit digital-to-analog converters

(DACs) connected to the 64 vertical columns in the LED

panel.

Only 32 DACs areenabled at a time, corresponding

to the right or left half of the panel.

The 32 DACs

require 128 bits every time a new row is scanned.

A new image is loaded into the display memory

from the external controlling device asynchronously.

Self-cbcking, seial data are detected by a phototransistor

and are decoded by the write control logic.

Six bits

specify one of 64 planes which is to be updated, and

32768 bits are the new image for the specified plane.

- 27

-

K

LED

6v

7-/'m ;.

MEMORY

{

.I'r

B1r

V9FF 5&

mE-Mcy

t

DjT4

--

-

FIGURE

8

------ - -

_

JJE F

OF

28

-

-

The plane address is held in a plane address register

and the data for the plane is loaded into a buffer

random-access memory (RAM).

Once the buffer is loaded

asynchronously, it is then transferred synchronously

into the CCD shift registers.

A completely new image

requires 64 planes to be transferred to the rotating

electronics.

MIEMORY ORGANIZATION

CCD memories are essentially 64K bit long shift

registers.

The image memory requires 221 bits, or

32 CCD packages.

Thus the widest memory that can be

made is 64K by 32 bits.

But for every sector we need

four bits for each of the 32 columns or 128 bits.

If

we clock the CCDs four times each sector, then we can

read out 128 bits each sector time.

be buffered external to the CCDs.

These bits must

Each of the CCD

packages can correspond to one of the 32 cylinders.

Four sequential bits in each CCD correspond to the

four bits of intensity information required for each

pixel, least significant bit (LSB) first.

Each time

a new set of four bits is read out of each CCD, a new

row is displayed.

After 64 rows have been displayed,

an entire sector has been presented, and we cntinue

with the next sector.

The process repeats after 256

-

- 29

cyl 11

+

4 bits -(LSB first){

cyl 1

zzzzzz:zzz~

_______________________

cyl 3 1

1

sector0 ,plane~~

ector plane

0

-I

-;

4

sector 0 ,plane63

sector1 ,plane-~

current

state -sector127plane

sector 128 planeo6 3

sector 2 5 5 ,plane

FIGURE 9

Memory Organization

63

sectors.

-

- 30

Think

FIGURE 9 shows this memory organization.

of the current state of the CCD memory (that is, which

data are currently being read out) as a pointer.

All

bits along a horizontal row in FIGURE 9 are read out

simultaneously.

When there is no write command given

to the shift registers, the data remain

in the memory.

The CCD is clocked 65536 times per revolution,

and there are 60 revolutions per second.

Thus, the

CCDs must operate at a frequency of 3,932,160 Hz, or

about four DvHz.

The only available CCD shift register-

that operates at four MHz is the Fairchild F464.

(See

Appendix II.)

The F464 is arranged as 16 seperate 4096-bit

long shift registers.

These are seperately addressable

by a four-bit address, but all registers are clocked

simultaneously.

The device can appear like a single

64K bit register by incrementing the address every

4096 clock pulses.

The order in which the data bits

are read out of the memory can be modified by performing

some function on the addresses to the CCDs.

This feature

is used to generate data in the proper sequence for

interlacing.

To interlace, we need to read out of memory all

the pixels for sector 0 ,

and display them on the right

-

- 31

half of the LED panel when it is in the correct position.

Then, we need to read out sector1 2 9 and display it on

(Sector1 2 8 is opposite sector0

.

the left half panel.

One more is sector 1 2 9 .)

2, 131, 4, 133, ...

of the panel.

We then continue with sectors

alternating left and right halves

On the next revolution, we must then

display the odd sectors on the right half panel and

the even sectors on the left.

TIMIING

The complete design of the rotating electronics

are shoen in FIGURES 10 to 16.

at the bottom of FIGURE 10.

The main timing originates

We ned to clock the CCDs

at a frequency of 3,932,160 Hz.

It would be helpful

to have a signal at this frequency which is symmetric,

because of the clock requirements of the CCDs.

The

phase locked loop generates a signal at twice this

frequency, 7,864,320 Hz, which is divided by two digitally,

producing a symmetric square wave.

The phase locked

loop drives a synchronous counter, which generates

all the addresses and timing for the system.

We must

divide the phase locked loop output by two to generate

f, the CCD clock frequency, then by 216 to generate a

square wave with a period once every revolution, then

by two again.

This last bit is used for interlace to

~1

-32-

57

DA 4

I

IOc

KI

(DA

7A

4.r4

iOk

-C

A3

LEFr/RI&Hr

~

715 i

1

+.

~

+r6

E + -1f

~

K-

7- LS8

Qg

-C

~r,

;,VIC

~:&

o

D

M

D

T-4

D

7-31

Q

Tal

r6-A

A,

A B

S

Z

it~-

Qr

r

-

L '? i-

P, IL

7-,

61PI

FIGURE,

r~A1/A'G

I

S PE Er7

OF

KAw

W

y

At

'5

-

- 33

I

LL

C'7

1-

Di4

*q

7'13 'i II

-L

%

Dour

A,

if4

1a

3-DM1

,

CC W

IS - DIA/31

rcp ME-Moay

FIGURE 11

|

ccl' /u1EM~~RY

FIGURE 11

I~EE~7

of

GH Eer

j D/~.It~' 8y'

OF

P~

I DRAW/N BY. aF-?

_It

__I,

11,obrP130"/V3

orv, D t'

V P1, ,

vl1

0/)I, Dims

AlV,

oiWV 8

biv

bilo Di~

DiI,

DW,

D,

Di'N~

blfDM,

D/t' D

bI

7

Div0

DA

D/,'X

DhV

PY, bW~Di 11 - D

,v

I/4~3

IN

-

7 6

D'AI,

/-

[VTI~

Pm

rl,-,,A L

9,q Z C L

L

______

FIGURE 12

5

OF

) X,4 V,/ A

BY

6

7q/138

7

LED

1'AEL 5 L2

K-

--

63

-,

(6)

j33

~

-t~

p

1

J

13E

A)-

L3

LIl~

LI

LX

I.

I0

L0

LI~

I-,

FIGURE 13

--

- - II

z 1 '4/V [3/:

V.

sD o

-{

77

ccc

-

Cf'\

I

p oiiep,'/p

L'D

ly

CcDwe

------------- T-

-

FIGURE 14

siJer

or

~~

AAO

I

7.3

1/ 7

-o

Kit

cl-

5Aft1'A

7

_

Lj'

I

L4-+

00

I

0 7411 138

hS.

A

Az

FIGURE 15

,3uFfER

PIE/i

C~Jg y

Q

+

2316- 6 7

B

13

Er

0F

By:

j DA,4~ WN BY:

QB

(JPq

38

FIll/ZS 7

P,

T7

1

r-C

r

ab

y

94,,

A447

AAj

7AJ

yy

Y/

-,jA, Xy Yj Y, Xv,

Ay A

94, AA,

AAj+f AA,

IA

4S

0A

At,43 4

0og, Y.yyY33 y

,

,9,AY , Y, ,

QAo

tF96 7511-f-7

Tlf

63

82

s

Sl

Ol

gl

191

I

Are

ff

sS

'sy '63 9S46

7

f

J-

0

7

f-C C-

.4

....

..

.......................

7AI 2 8 -,

q, A, AIA 9, , s;'g; e,

A A Al R, b"

T-

A3 A.2

T

7"

al

Oil

Q1

03

Q7

PAS-

qEDD/ R

4

CC,

I

C

i-FIGURE 16s/Er I SIIZ--r 7-

or

RMY

I DR14 V A/ . Y:

/I

39

-

-

indicate which half of the LED panel displays odd or

even sectors.

The total divider chain divides by

218 and should give a frequency of 30 Hz, or exactly

one half period per revolution.

The opto-interrupter

generates one pulse per revolution, which is divided

by two to yield a symmetric square wave at 30 Hz.

These

two 30 Hz signals are used by the phase locked loop

to synchronize the system to the rotational speed of

the motor.

The phase locked loop will keep the same

phase relation between the signal labeled Q16 and the

other input to the loop, which is the opto-interrupter

pulse divided by two.

Thus, the counter will always

contain all zeros (this is the origin; r=z=e=0) when

the rotating panel is at the same place relative to

the fixed plate which interrupts the opto-interrupter

beam.

The logic above the phase locked loop and counter

in FIGURE 10 generates the signals 01, 32, 0T1 and

0T2 required by the CCD memories.

The two exclusive-or

gates generate the signals LEFT/RIGHT and A , used for

interlacing.

We need some more definitions.

The collection

of bits (Q1 6 0***'Q0 ) can be considered a single number

and written in base ten.

Define this number to be Q.

-

- 4o

Similarly, we can define BIT to be (Q1 ,Q0 ), PLANE to

be (Q7 ,...,Q 2 ), sector to be (A3 ,Q1 4 ,...,Q 8 ), and FIELD

to be (Q16).

BIT ranges from 0 to 3 and specifies

one of the four bits required to specify any given

BIT is incremented (modulo 4) every

pixel intensity.

time the CCDs are shifted.

PLANE specifies one of the

64 planes and is incremented every time BIT returns

to zero.

SECTOR specifies one of 256 sectors and is

a number which is incremented every time PLANE cycles

except the most significant bit of SECTOR is complemented

if LEFT/RIGHT is one.

LEFT/RIGHT is one when FIELD and

the LSB of SECTOR are different.

Thbre are two -possible

fields which can be displayed on any given rotation

because of interlace.

FIELD specifies which of those

two fields is the current one.

FIGURE 11 shows the CCD memory and some associated

registers.

Data are shifted out of the memories every

leading edge of f.

The leftmost CCD corresponds to

.

cylinder0 and the rightmost corresponds to cylinder3 1

Data in the shift registers recirculates unless CCDWE is

low, in which case data are written in from inputs

Din

to Din

.

Consider the flow of bits through the

leftmost CCD, cylinder0 .

Suppose BIT=O.

Then the output

of this CCD (the signal labeled D 3 ) will be the least

-

- 41

significant bit of the four neccessary to specify the

intensity of the next pixel in the cylinder.

After the

next edge of f, that least significant bit, BIT 0 will

be shifted into the 74364 eight-bit register following

the CCD and will appear at the output labeled D 2 .

Just

before the fourth leading transition of f, when BIT=3,

D

D,=BIT,

D 2 =BIT 2 , and D =BIT .

On the next

transition of f, T3 goes low and D0 through D 1 2 7 are

loaded into the lower register in FIGURE 12.

of this register,

10,...,L 1 2 7

The outputs

represent the intensity

of the 32 pixels along the current row.

The current

row is addressed by SECTOR and PLANE.

The value of SECTOR corresponds to one of 256

positions the LED array may have.

The value of PLANE

selects one of the 64 horizontal rows in the panel.

(See FIGURE 13.)

The signals Lo,...,L 1 2 7 are sent to

32 DACs which control the intensity of 32 vertical

columns on the right half of the panel, and they are

also sent to another 32 DACs which control the intensity

in the left half of the panel.

The left or right set

of DACs are enabled according to the signal LEFT/RIGHT.

UPDATING THE MEMORY

The circuitry at the top of FIGURE 10 decodes

the serial data received by the phototransistor into

-

Data

I

0

1

1

42

1

1

I

0

1

I

1

I

I

.................

..

....

LJ.J...JJ ..

____...__L...L

SCLOCK

Li

SDATA

1

1

0

0

1

1

1

FIGURE 17

Serial Data Format

.1111110XXXXXXDDDD ......

Preamble

Plane

address

(6 bits)

.DDD..0000,

32768 bits data Postamble

FIGURE 18

Data Block Format

1

1

14'3

-

-

The serial data format

seperate clock and data signals.

is shown in FIGURE 17.

The data is self-clocked, phase

encoded at a data rate of about two million bits per

Any plane in the image may be addressed randomly.

second.

A seperate data transfer sequence must be initiated

whenever a plane is to be updated.

The format of a

single plane update transfer is shown in FIGURE 18.

The

preamble is used to indicate the start of a transfer

sequence.

Following the preamble is a six-bit address

corresponding to one of the 64 planes.

PA.

Call this value

The 32768 bits of image information for the addressed

plane follow the plane address.

Every four bits correspond

to the intensity of a new pixel, LSB first.

pixels form a new row.

Every 32

There are 256 rows in a plane.

A postamble follows the data.

We can give the incoming bit stream a 15-bit

address for purposes of discussion:

(BS 1 ,BSO)

call it BS

,...,BSO'

specifies one of four bits of intensity for

a given pixel.

Call this quantity BBIT.

specifies one of 32 cylinders.

(BS 6 ,...,BS 2

Define this to be BCYL.

(BS 1 4 ,...,BS 7 ), which specifies one of 256 sectors,

should be called BSEC.

The basic mthod of loading

this bit stream into the CCDs is to load it into a

seperate 32768 bit buffer asynchronously, and then

-

- 44

shift bits out of the buffer, one every time the CCD

is clocked, into a serial/parallel conversion register.

Then the register is written into the 32 CCDs at the

proper time.

FIGURE 19 illustrates the timing of this.

Assume for the moment that there is no interlace;

SECTOR=I is followed by SECTOR=I+1

(modulo 256).

The

serial parallel register is shown at the top of FIGURE 12.

This register is 128 bits long and corresponds to one

row.

Note that the outputs of the register are spaced

four bits apart.

When 125 bits have been shifted into

this register the 32 outputs correspond to the 32 least

significant bits of intensity information for a given

row.

On the next shift these outputs correspond to the

next bit, and after 128 bits have been shifted these

outputs correspond to the most significant bit of intensity.

So, these outputs are the data to be written into four

consecutive cells in each of the 32 CCDs.

enable CCDWE during the proper four cycles.

We need to

Since

we are updating plane PA, we want to make CCDWE active

when PIANE=PA.

One row contains 32 pixels, addressed by BCYL.

We must make sure that the 32 pixels of any given row

are loaded into the conversion register by the time

we assert CCDWE.

Referring to FIGURE 19, one can see

- 45

SECTOR

0

PLANE

BIT

BBIT

0

0

1

2

0

1

2

3

3

PA-1

0

1

2

0

1

2

PA

0

1

2

0

1

2

3

3

CCDWE

0

1

BCYL

K

BSEC

1

63

0

This

corresponds

F~

to 256

0

clock

pulses

6

PA

0

63

I-i

0

PA

0

0

Ix

o

63

PA

zz

__

63

32

31

63

0

0

.

I

PA

FIGURE 19

Memory Update Timing

11

331

X

1

I+1

63

0

-

- 46

the sequence BCYL must follow, and its timing relative

During the time marked X, it does

to PLANE and CCDWE.

not matter what BCYL is.

It is easiest to make is

sequence from 0 to 31 during this time just as it does

during the intervals between X.

We can consider BCYL

to be K (modulo 32), where K is as shown in FIGURE 19.

K and BCYL change at the same rate as PLANE, every four

clock pulses, but K is 63 when PLANE is PA, and K=0

Pa is the plane we are currently

when PLANE=PA+1.

updating, and is stored in a six-bit register.

We

can then calculate K:

K = PLANE BCYL = K

(PA + 1)

(modulo 64)

(modulo 32)

= PLANE -

(PA + 1)

= PLANE + TA

(modulo 32)

(modulo 32)

The only quantity left to calculate is BSEC.

We must load the conversion register with data for

sectorI by the time sector

in the CCDs.

is available for writing

So, we may need to produce the data for

sectorI from the buffer when SECTOR still equals I-1.

The changes in BSEC are offset from the changes in

SECTOR.

Adding PA to the 14 bit quantity (SECTOR,PLANE)

and taking the eight most significant bits gives us a

number which changes when BSEC should, but when BSEC

47

-

-

should be I this number will be I-1.

only to add one to this number.

Thus, we need

Adding one to the

number after the low six bits have been discarded is

numerically the same as adding 64 before the low six

bits are removed.

Note that those low six bits are

The complete calculation

exactly K as calculated earlier.

is now:

(SECTOR, PLANE)

+ PA

(a 14 bit quantity)

(sign extended to 14 bits)

+ 64

(BSEC, K)

In all cases BBIT is the same as bit.

the low five bits of K.

as (0,...,O,PA 5 'PA 5 1 '''

BCYL is simply

Note that 64+E is the same

0)'

The circuitry which performs the loading function

is shown in FIGURES 14, 15 and 16.

In the control

logic of FIGURE 14 serial data bits are shifted into

the 74164 eight-bit shift register, until the gates

connected to the outputs of that register detect the

preamble.

Then, after the plane address has been shifted

into the low six bits of the shift register, the address

is complemented and loaded into the 74174 six-bit plane

address register.

The signals PA 5 '''' PA 0 are the

complemented plane address, PA.

At this same time,

-

- 48

RPULSE is generated and we are ready to use the next

The

32768 bits of image information which follow.

remaining logic in FIGURE 14 generated CCDWE which

goes low when PLANE=PA.

FIGURE 15 shows the buffer memory.

Eight 93471

4K static RAMIs are used to make a 32768 by 1 bit memory.

(See appendix III.)

RA14,...,RAO.

The address to the buffer is

When the signal S is low, SCLOCK writes

SDATA into the addressed location in the buffer.

When

S is high, the addressed bit appears at BDATA.

The address to the buffer is generated in FIGURE 16.

When RPULSE is generated, the counter at the top of

FIGURE 16 is reset and S is set to zero.

The counter

output, through the 74157 multiplexor, is used as the

address to the buffer.

Thus, RA follows BS.

After

32768 bits have been loaded into the buffer memory,

the flip-flop which indicates the state of S is set,

and S goes high.

Up to this point, the circuitry for

loading data into the display from the external world

has operated independently of the system clock.

At

this time, all that remains is to move the data in the

buffer to the correct locations in the CCDs.

When S becomes high, the new address to the

buffer comes from the logic beneath the multiplexor

in FIGURE 16.

49

-

-

This calculates (BSEC, BCYL, BBIT) as

defined earlier.

The exclusive-or gates rearrange

the address space for interlacing in the same fashion

as the gates which calculate A3 in FIGURE 10.

After

one revolution of the display, the entire buffer has

been written into CCD memory.

plane may be transferred.

At this time another

If no new plane is transferred,

the buffer will be written into the CCDs again because

this requires fewer parts to accomplish than to inhibit

writing after the buffer has been written once.

This

process may be interrupted at any time to load new

data into the buffer.

DATA TRANSFER RATE

If the serial optical channel transmits data

at a rate of two million bits per second it will take

about 17 milliseconds to transmit a single plane.

This

is roughly the time required for one revolution of the

display.

We must then wait one revolution for the

CCDs to be written before another plane may be sent.

Thus it takes two revolutions to update a plane, and

about 120 revolutions to update an entire field.

is roughly two seconds, an excellent figure.

This

This

number could even be halved by using two plane buffers.

While one buffer is updating the CCDs, the other is

-

- 50

being loaded from the external source.

But this is

not neccessary because it would be acceptable to wait

considerably longer than two seconds for a new image.

POWER ESTINATES

The digital electronics will require about six

amps at five volts.

The LED panel and drivers may

require another 10 amps.

This would make the power

dissipated around 75 watts.

As this must be carried

by sliprings, it may be better to supply these with

75 volts at one amp and generate the required voltages

after the sliprings.

The rotating electronics will be enclosed, so

a fan must be used for cooling.

CONCLUSION

Currently, some drivers for the LED panel have

been built and we have managed to display an even grey

scale on the panel.

We expect to have completed this

prototype in the Fall of 1978, ,at which time we will

begin construction of a larger, production prototype.

This display will have 256 sectors, 256 planes, and

128 cylinders, with a four-bit grey scale.

32 million bits of memory to store an image.

This requires

A company

has been formed to manufacture the device once the

second prototype has been completed.

I feel confident

that a workable three-dimensional display will be developed

using this system.

APPENDIX I

-

- 51

ii

T

'a

LEDscreenTM

A changing multicolor display

flat as the picture hanging on your wall.

LEDscreenTM display uses are

limited only by the imagination of

designers. It will create any pattern

that a cathode ray tube can create

- limited only by its resolution of

up to 50 lines per inch.

Images can change as rapidly

as the time required to switch the

LEDs on or off-time shorter than

the visual persistence of the human

eye. Thus, images may easily

change fast enough to create illusion

of smooth, continuous motion.

Saves space. Saves weight.

No other type of display is

nearly so compact and light in weight.

Typical thickness is 1/4" including

pins. Typical weight is 1/2 ounce per

square inch. The LEDscreen display

is ideal for portable equipment, aircraft and any other use where minimizing volume and weight is essential.

ments. The building blocks are constructed using time-proven hybrid

techniques in which IMI is expert.

Simple to drive.

The LEDs are powered by

the +5v dc supply commonly used

to power discrete TTL logic, bipolar

ICs and many MOS circuits. Each

lamp is connected to a pin on the

vertical and horizontal edge. A LED

is illuminated by simple X-Y selection

of the proper pins, thus enabling the

use of any scanning or drive

technique.

Low power for battery operation.

Each LED consumes as little as

2 ma LED at 3v dc, and as a rule

only a small fraction of the LEDs

are illuminated at any given moment.

Power consumption may be further

reduced under multiplex operation

with a 1% to 4% duty cycle.

Brightness varied to suit ambient light.

Brightness may be automatically

controlled by including a photocell

to detect ambient light levels.

A few typical displays

Dynamic functions

Avionic displays

4

-o

2-

0

LEDscreenmbuilding blocks create

any size display.

Standard building blocks may be

arrayed to create a display as large

as you wish. Building blocks of several sizes up to 4" x 2" have already

been manufactured. Custom building

blocks of nearly any other size and

shape are also available.

E0

E

4A

Waveforms

Real-time bar graphs

Rugged, long life.

No filament to burn out. The

solid-state LEDs have a virtually infinite operating life and can withstand

military shock and vibration environ-

TEMP.

MIES

RATE

OXYGEN

Electrical and Mechanical

Opto-Electric Characteristics

0.180 TYP.

Min.

Typ.

Max.

Unit

Condition

.1

.3

1.6

1.9

1.9

mcd

V

If.

.4

2.5

3.0

4.0

mcd

V

If-20mA

If - 2mA

2.5

3.0

25

4.0

50

mcd

V

nsec

If - 20 mA

If - 20 mA

10%-90%

Red Die

Luminous Intensity

Forward Voltage

Green Die

Luminous Intensity

Forward Voltage

Yellow Die

Luminous Intensity

Forward Voltage

Rise and Fall Times

.4

Maximum Ratings

Substrate storage temperature

Operating temp. in free air

10 mA

If-10mA

MAX.

-z

SCREEN

AREA

D B

IePIN

TYP.

TYP

-40C to +125*C

O'C to 70C

C

A

0.150MIN.--+

Contrastng color dot so denote row 1 column 1.

Model

PlS 800

MIS 801

PIlS802

Form No. 1000-3/77

DIA.

-0.019

Screen Size

2" x 4"

1" x 1"

2" x 2"

Matrix Size

64 x 128

32 x 32

64 x 64

A

4.48

1.58

2.58

B

2.58

1.58

2.58

Custom sizes, shapes, resolutions and colors are available.

integrated

microsystems

incorporated

Handheld

.1

0.100I~

Intensity is maintained within a

ratio of 1.5 to 1 from die tc

0.1804T

TYP.

TYP.

-

-

1215 Terra Bella Averfue

Mountain View, Calif. 94043.

Phone (415) 965-3900.

Copyright 1977

C

4A

1.5

2.5

D

2.5

1.5

2.5

computer

terminals

inteqrated

microsystems

incorperated

Dear Sir:

Thank you for your recent inquiry regarding Integrated Microsystems

Incorporated's exciting new product, LEDSCREEN.

LEDSCREEN is the result of a development effort designed to produce flat,

lightweight, low-voltage DYNAMIC GRAPHIC displays for aircraft cockpit

use.

Now, this state-of-the art product is designed into medical, test

and measurement, date terminal and portable hand-held systems.

Three standard LEDSCREENS are available:

Screen Size

Number of

red Leds

uIS 800

2" x 4"

8,192

64 x 128

$1,500.00

uIS 801

1" x 1"

1,024

32 x 32

$

250.00

uIS 802

2" x 2"

4,096

64 x 64

$

990.00

Model

Custo i-es,

apes,

resolutions

and colors

X-Y Matrix

1-9

price

are available,

Please contact me or the local

I've enclosed a LEDscreenTM data sheet.

representative shown below if you have any special requirements or

questions regarding this information.

Very truly yours,

Mike

ik

Applications Engineer

MM/cb

Enclosure

mlcrosystems

0 divion

Of aerofIex Iobli

incorporated

MIKE MALIK

Applications Engineer

1215 Terra Bella Ave

Mountain Vie Ca

94 03

1215 Terra Bella Avenue, Mountain View, CA 94043 Telephone. (415) 965-3900

LEDscreen

I

TM

Application Note

Custom sizes shapes resolutions and colors are available. The

LEDscreen can be designed to be

end and side stackable with no

visible break in resolution to form

larger displays than are possible

with single units. Complete applications information is available

from your IMI sales representative.

Table 1. Opto-Electric Characteristics

Min.

Typ.

Max.

Unit

Condition

0.1

0.3

1.6

1.9

mcd

V

If = 10mA

If = 10 mA

mcd

If = 20 mA

V

If = 20 mA

mcd

If = 20 mA

If = 20 mA

Red Die

Luminous Intensity

Forward Voltage

Green Die

Luminous Intensity

0.4

2.5

Forward Voltage

3.0

4.0

Yellow Die

Luminous Intensity

0.4

2.5

Forward Voltage

3.0

4.0

V

Rise and Fall Times

25

50

nsec

10%-90%

Intensity ratio is maintained in a ratio of 1.5:1 from die to die

Maximum Ratings

Substrate storage temperature

Operating temp. in free air

Red

-40 0 C to +125"C

00 C to 700 C

Green

100

Yellow

100

80

R

100

80

41 C

80

C

0

C

E

E

w

w

40

CD

40

20

I6

20

0 1 . II

600

I I ",I,

640 660 680

620

X- Wavelength - nm

X peak (Xp) = 650 nm

700

0

500

40

20

600

700

X - Wavelength

-

800

0 1

500

1215 Terra Bella Ave Mountain Vew Ca 94043 Phone(415)965-3900

700

-

800

nm

X peak (X p) = 570 nm

Figure 4. Emission Spectrum for Red, Green and Yellow Colors.

a dMsion of aeroflex laboratories incorporated

.I

N

600

X- Wavelength

nm

X peak (X p) = 561 nm

LLintegrated

microsystems

H

I1

60

60

60

E

w

LEDscreen

TM

Application Note

C

The LEDscreen drive circuitry

should be designed to scan either

columns or rows in such a manner

as to allow individual diode

~5V

-

U

U

01

cc0

*4

0

Z

M

I-

6-8V

current regulating. This is necessary

0

-

to assure even LED brightness

1N

N

levels throughout the display and

to maintain illumination levels

independent of displayed patterns.

-4

_

When scanning columns in

sequence, a pattern is generated by

reading row data stored in a memory function in sync with the

column scan circuitry. The scanning should completely refresh at

a minimum rate of 50 to 60 times

per second to present a f lickerfree pattern.

As a result of scanning the

display, individual diodes are

operated in a pulsed mode. The

duty cycle of the pulse is determined, in part, by number of

columns the circuitry must scan.

Therefore, to operate a LEDscreen

at a 2 mA DC equivalent light

output level and a scan rate of

100 Hz, each diode will require

200 mA current pulses. Because

of this, high current pulses can be

realized if, in any given column,

several diodes are to be turned

"on.

Column drivers should be able

to handle peak currents equal to

the number of diodes per column

times the peak current per diode.

In the above example, a one inch

column of 32 diodes would require a peak current of 6.4 amperes

to light all diodes in the column

The brightness of a pulsed LED

can be equal to or greater than

when operated at a DC forward

-

Figure 1 illustrates a typical

TTL/CMOS-compatible drive configuration. As shown, Q, develops

a constant current source with its

emitter resistor. Q2 should be

carefully selected for VcE(SAT) and

HFE. (Power Darlingtons are excellent choices in this position.)

02n

k02,

I I IN

1LM

TIMING

CIRCUIT

COLUMN

IC

SEQUENCER

MASTER

CLOCK

Figure 1. Typical TTL/CMOS-Compatible Drive Configuration.

current equal to the average pulsed

current. For example, with 40 mA

peak current at a 25% duty cycle,

the brightness will be similar to

DC operation at 10 mA. The brightness comparison will depend on

the actual pulsing conditions.

Under most conditions, the brightness will be greater with pulsed

operation.

A low duty cycle, high-intensity pulse of light appears brighter

than a constant signal equal to the

average of the pulsed signal since

the eye responds to the peak

brightness as well as to the inte-

grated brightness perceived. Besides

the lower cost, the practical benefit of multiplexed operation then,

is an improvement in display

visibility for a given average power

consumption. The brightness

variation from diode to diode is

also reduced by time-sharing. The

gain in brightness over DC opera-

tion can be significant at low duty

cycles of 1 or 2 percent and peak

currents of 50 to 100 mA.

Figure 2 is a plot of relative

light output vs. forward current.

At low currents, nonradiative

recombination processes reduce

the light output from that pre-

dicted on a linear relationship.

This is at the foot of the curve

in the 2 to 5 mA range per diode.

At high currents, the light output is reduced due to heating of

the die and loss of efficiency.

High current pulses at low duty

cycles avoid the problem of

limited power dissipation and

C

LEDscreenTM

Application Note

provide current densities for

efficient operation.

It can be seen in Figure 2 that

actual DC output at a 5 mA

average current is much less than

the ideal output. At higher peak

currents of 50 mA the peak output

falls slightly below the ideal curve.

For a 10% duty cycle at 50 mA

peak the integrated average light

output is much closer to the ideal

light level. It can also be seen that

operation in the foot of the curve

will cause variation in operation

at low DC current levels but will

be more uniform when in a pulsed

mode at low average current.

PULSED

OUTPUT

2

-

zHEATING

EFFECT

Z

0Peak

I-

Output

.o

Peak Current

Figure 3 outlines th'ree standard parts presently available in

one color. The parts are designed

to be plugged into standard pin

sockets of 0.100" spacing. Optoelectric characteristics, emission

spectrum information and maximum ratings are provided in Table

1 and Figure 4 respectively.

Ideal D.C.Il

output

-------

Ideal D.C.

output-Ave

rg

~

0

-

ee Ceen

s mA

5O mA

1OOmA

FORWARD CURRENT

Figure 2. Relative Light Output Versus Forward Current.

t'l

0.180

TYP.

I[4TYP.

0.100

-0-0.180 TYP.

J..

SCREEN

AREA

0.100

TYP

A.100

-JA

B

PIN DIA.

0.019 TYR

*

k **

117

D

1

+-

C

0.150

A

* Contrasting color dot to denote row

Model

piS 800

1 column

b

MIN.

1.

Screen Size

Matrix Size

A

B

C

D

2" x 4"

64 x 128

32 x 32

64 x 64

4.48

1.58

2.58

2.58

1.58

2.58

4.4

1.5

2.5

2.5

1.5

2.5

pIS 801

1" x 1"

jAS 802

2" x 2"

Custom sizes, shapes, resolutions and colors are available.

Figure 3. Outline and

Dimensions of Three

Standard Parts Presently

Available in One Color

A

LEDscreen

TM

Application Note

Custom sizes shapes resolutions and colors are available. The

LEDscreen can be designed to be

end and side stackable with no

visible break in resolution to form

larger displays than are possible

with single units. Complete applications information is available

from your IMI sales representative.

Table 1. Opto-Electric Characteristics

Red Die

Luminous Intensity

Min.

Typ.

0.1

0.3

Max.

Green Die

Luminous Intensity

Condition

mcd

V

If = 10mA

If = 10 mA

mcd

If = 20 mA

V

If = 20 mA

mcd

If = 20 mA

If = 20 mA

1.9

1.6

Forward Voltage

Unit

2.5

0.4

4.0

3.0

Forward Voltage

Yellow Die

2.5

0.4

Luminous Intensity

Forward Voltage

3.0

4.0

V

Rise and Fall Times

25

50

nsec

10%-90%

Intensity ratio is maintained in a ratio of 1.5:1 from die to die

Maximum Ratings

-40 0 C to +125 0 C

00 C to 70"C

Substrate storage temperature

Operating temp. in free air

I-rk----

Yellow

Green

Red

100

M-----

-

-

80

80

CR

C

0

0

40

40

20

- - -

0

600

a

20

--

0

620

640

680

660

X- wavelength

-

700

500

20

0 L

600

700

800

X peak (X p) = 561 nm

microsystems

a dMsion of aeroflex laboratories incorporated

1215 Terra Bella Ave Mountain Vew Ca 94043 Phone(415)965-3900

-1N I%

600

X-

800

700

wavelength

-

nm

X peak (X p) = 570 nm

Figure 4. Emission Spectrum for Red, Green and Yellow Colors.

integrated

Il I

500

X- wavelength - nm

nm

X peak (X p) = 650 nm

80

60

0r

0

TI

E

w

E

w

40

II

0

60

60

E

w

1A I

(

100

100

-

- 59

APPENDIX II

OCTOBER 1977

GENERAL DESCRIPTION - The F464 is a 65,536-bit dynamic serial memory configured as 16 randomly accessible shift registers, each 4096 bits long. Each of these shift

registers is designed utilizing Charge Coupled Device (CCD) techniques with the interlaced

Serial-Parallel-Serial (SPS) register structure which features both low power and high

density characteristics. The high density of the F464 is further enhanced through the use

of an electrode-per-bit memory cell approach. The high density permits packaging the

memory in a standard 16-pin (0.3"-wide) dual in-line package which allows the construction of highly dense memory systems using widely available automated testing and

insertion equipment.

LOGIC SYMBOL

6' L c

12-

11

Furthermore, this buried-channel CCD memory is fabricated using Fairchild's double-poly

n-channel Isoplanar process. This process allows the F464 to be a high performance,

state-of-the-art memory circuit which is manufacturable in large volume.

-

2

5

*T

Ao 01

02

OT1

OT2

A

10-

A2

6-

A3

cs-

-

Vcc.3

INDUSTRY STANDARD 16 PIN (0.3"-WIDE) DUAL IN-LINE PACKAGE.

0

OPERATING FREQUENCY RANGE: 1 MHz TO 5 MHz.

S

j5 s HALT TIME AT 2.0 MHz

S

LOW CAPACITANCE TTL-COMPATIBLE INPUT (EXCEPT CLOCKS).

0

3-STATE, TTL-COMPATIBLE, LATCHED DATA 6UTPtrT--S

OUTPUT DRIVE CAPABILITY:35 m

S

LOW CAPACITANCE 12 V CLOCKS:

100 pF (TYP)

01 AND 02:

30pF (TYP)

#T1AND #T2:

* LOW POWER

NORMAL OPERATION:

<336 mW (MAX) @ fmax 888

STANDBY:

<66 mW (MAX) @ fmin

- \

* STANDARD POWER SUPPLIES (+121V, +5 V, AND -5 V)

0

7

14 -. c

'5

WE

DIN

DOUT

13

IL

r 1-& 1t

OR2:

E1*

VDD

Vcc

=PI1

PIN 16

Vss =PIN 8

SVB = PIN 9

3402181

7.0,237-2796

U

CONNECTION DIAGRAM

DIP (TOP VIEW)

BLOCK DIAGRAM

A

0

1

0-4-02

...

. . .

-- . -.

..

T1

OT2

I-OF-16

-BLC

DECODER

A

VDD

1

16

Vcc

02

2

15

WE

cs

3

14

DIN

OT2

4

13 j

OT1

5

12

A0

A 3 L6

11

Al

017

10

A2

C

AH

ANDDOU

2--

-

-------------------

--

oTu

-BUFFER

A3 -5,

IDIN'

1O.UT

4096-BIT

BLOK

-------------..-----.-.

V

VDD

C

Vcc

V

4

LATCH

V5 5

'4C

8

9

VBB

B

S C

3

1

2196

Z3.4

1 1977

1977

Corporation

and Instrument

camera and

Fa.rch.Id Camera

Fairchidd

Instrumnent Corporation

Printed in U.S.A.

Printed in U.S.A.

203-11-0005-087 15M

.11

203-11 -005-D87 15M

464 ELLIS STREET, MOUNTAIN VIEW, CALIFORNIA, 94042 (415) 962-5011/TWX 910-379-6435

FQJMCH I LD.

FAIRCHILD 65,536 X 1 DYNAMIC SERIAL MEMORY * F464

PIN NAMES

Data Input

Serial Clocks

DIN

DOUT

Data Output

An

Transfer Clocks

Address Inputs

VCC

+5 V Power Supply

CS

Chip Select Input

VSS

0 V Power Supply, GND

WE

Write Enable Input (Active LOW)

VBB

-5 V Power Supply

VDD

+12 V Power Supply

1,02

#T1,

OT2

FUNCTIONAL DESCRIPTION

ORGANIZATION - The F464 is a 65,536 x 1 bit dynamic serial memory organized internally as 16

dynamic shift registers (or blocks) of 4096 bits each in length. These 16 shift register blocks are

randomly accessible through four internally decoded Address inputs (A0 - A 3 ). When a given

register is selected, its input and output are internally connected (as needed) to the DIN and DOUT

pins, respectively, thus permitting simultaneous read and write operations.

ARCHITECTURE - Each of the sixteen shift register blocks is implemented using a Serial-ParallelSerial (SPS) register architecture. In this approach N data bits are sequentially shifted into a "serial"

input register. When full, the entire N-bit word is shifted in parallel into N "parallel" registers of M

bits in length, as illustrated in Figure 1. At the other end of this parallel register structure, bits are

loaded in parallel into an N-bit serial output register. Bits in this register are then shifted out toward

the sense amplifier at the output and are automatically recirculated back to the input serial register

unless a WRITE operation is specified.

The primary advantages of this type of architecture include very high density, low power, and low

clock capacitance. These features all result from the fact that in the SPS architecture the parallel

registers which encompass most of the total storage capacity within each block are shifted at a

considerably slower rate (fIN/N) than the clock rate of the input or output serial registers (f INIn actuality, each 4096-bit block of the F464 is implemented using an "interlaced" SPS structure in

which each bit of the input serial register services two parallel registers rather than just one. The same

is true for the output serial register. In addition, "electrode-per-bit" design techniques are used to

reduce the effective cell size by minimizing the number of electrodes used to store each bit of

information. These techniques obviously enhance the memory density considerably. The dimensions

of the F464's interlaced SPS structure are 32-bit input and output serial registers and 64 parallel

registers, each 63 bits in length. See Figure 2. These dimensions were chosen in order to optimize the

power/density/latency tradeoffs inherent in the CCD memory approach.

CLOCKS - The F464 requires four MOS level clocks: two high frequency (1 to 5 MHz) serial clocks

and two low frequency transfer clocks. The serial clocks, #1 and 02, control the movement of data

within the input and output serial registers of each 4096-bit block and have a frequency equal to the

data rate. The transfer clock OT1 is used to transfer data from the input serial register to the parallel

registers while the transfer clock OT2 is used to transfer data from the parallel registers to the output

serial register.of each block. The data present in the parallel registers is shifted by internally generated

ripple clocks. This ripple clock technique allows a high bit-packing density approaching one electrode

per bit.

To achieve proper transfer phasing, the two transfer clocks are asymetrical about a 32-cycle interval

(31.5 and 32.5 cycles) but symmetrical about a 64-cycle interval. The phasing between these transfer

clocks alternates in order to achieve correct bit storage in each block. When 4 T1 occurs during 01

time, #T2 occurs during 02 time 1.5 cycles prior to OT1. When #T1 occurs during 02 time, #T2

occurs during 'Pi time 2.5 cycles prior to OT1. Figure 3 illustrates the clock phase relationships.

The clocking operation rnay be momentarily halted for as long as 15 ps once each interval of 64 or

more clock cycles provided that the clock frequency is at least 2.0 MHz or higher. During this "halt

time" it is recommended that all clock signals be in the LOW state in order to limit power dissipation.

2

FAIRCHILD 65,536 X 1 DYNAMIC SERIAL MEMORY 0 F464

INPUT SERIAL

EI

REGISTER (FREOUENCY

INPUT SERIAL REGISTER (32 BITS)

ffIN)

J-iIii

BIT 31 OR 63 BIT 30

(4

go

S

N7-B3TEl

Fig.~

OUTPUT

OUTPUT

-

BIT 31

OR

OR

V)

Co

m

M

BIT 0 OR 32

BIT 1 OR 33

62

wo

co

wo

A

mn

BIT

63 BIT 30 OR 62

1OR 33

BIT

PARALLEL

REGISTERS

D

0 OR

32

SERIAL REGISTER

FFREQUNFE

SP

=E M E T N4

~

01 SIMLIIE SPSP EXMPETITUN T

OUTPUT SERIAL REGISTER (32 BITS)

Fig. 2 INTERLACED SPS ARCHITECTURE

59

01

61

63

1

5

3

'I'll

59

61

63

1

5

3

_

02

7

9

7

_

11

9

_

13

11

13

_

15

17

15

19

17

_

21

19

_

23

21

23

_

25

27

25

29

27

I

29

31

33

31

37

33

39

37

35

39

41

41

hulllll Ulillillili

OT1

4

T2

DETAIL 1

DETAIL 2

a) OVERVIEW OF CLOCK PHASING

CYCLE 29

CYCLE 28

_f~8

_

CYCLE 30

CYCLE 31

_

f9__3\fl

CYCLE 32 --

ON

_j/-\2/~

OT1

OT2

) DETAIL 1

CYCLE 60

01

-*

4--

CYCLE 61

-*

CYCLE 62

94-

110 *

-

CYCLE 63 -

-

INPUT

4--

CYCLE 0

62

64=

62

02

_f63\__-

OT1

OT2

c) DETAIL 2

Fig. 3 F464 CLOCK RELATIONSHIPS

3

0

-+m-

FAIRCHILD 65,536 X 1 DYNAMIC SERIAL MEMORY 0 F464

CONTROLS

In addition to the four Address inputs (A0 through A 3 ), other TTL level control signals available on

the F464 include Write Enable (WE) and Chip Select (CS). The CS input, along with the address

information, is presented during 01 HIGH time and dynamically latched with the trailing edge of 01

which simultaneously disables both the address and CS buffers. This action prevents changes that

occur on the external pins from entering the internal circuitry when #1 is LOW. The WE control

signal determines whether new data from the DIN pin, or recirculated output data, is presented to the

input of the addressed block. The non-addressed blocks are automatically recirculated.

MODES OF OPERATION

STANDBY (Recirculate-only cycle)

In Standby mode (CS LOW), the contents of all 16 blocks are recirculated automatically, and the

device disregards the WE, Address, and DIN inputs. The output latch goes into the high impedance

state after the trailing edge of the #1 clock. Minimum power dissipation results when the device is

operated in the recirculate mode with minimum 01 and 0 2 pulse widths at the lowest allowed frequency.

READ-R ECIRCULATE MODE

In this mode of operation (WE HIGH and CS HIGH) the data from the selected block is presented to