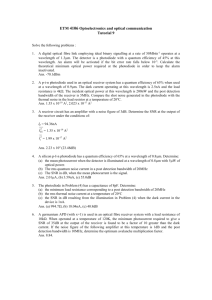

Optical Receiver Techniques for Integrated A 201

advertisement