Outphase Power Amplifiers in OFDM Systems

by

Anh D. Pham

Bachelor of Science in Electrical Engineering and Economics

California Institute of Technology, June 2000

Master of Science in Electrical Engineering and Computer Science

Massachusetts Institute of Technology, June 2002

Submitted to the Department of Electrical Engineering and Computer Science in partial

fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2005

Massachusetts Institute of Technology 2005. All right reserved.

Author_____________________________________________________________________

Department of Electrical Engineering and Computer Science

September 2005

Certified by_________________________________________________________________

Charles G. Sodini

Professor of Electrical Engineering and Computer Science

Thesis Supervisor

Accepted by________________________________________________________________

Arthur C. Smith, Ph.D.

Chairman, Committee on Graduate Students

Department of Electrical Engineering and Computer Science

2

Outphase Power Amplifiers in OFDM Systems

by

Anh D. Pham

Submitted to the Department of electrical Engineering and Computer Science on September

12, 2005 in partial fulfillment of the requirements for the degree of Doctor of Philosophy in

Electrical Engineering and Computer Science

Abstract

A trade-off between linearity and efficiency exists in conventional power amplifiers. The

outphase amplifying concept overcomes this trade-off by enabling the use of high efficiency,

non-linear power amplifiers for linear amplification. An amplitude modulated signal is first

decomposed into two constant amplitude, phase modulated signals that can be amplified

using two high efficiency switching power amplifiers. The two outputs are then recombined

to restore the original amplitude modulated signal. In this manner, an outphase power

amplifier can simultaneously achieve high efficiency and good linearity.

This thesis investigates the capability of the outphase amplifying technique in modern

wireless communication. First, a digital amplitude-to-phase conversion scheme is proposed

to facilitate the outphase decomposition. By taking advantage of the available computational

power in current digital technology, the amplitude-to-phase conversion can be implemented

with both accuracy and efficiency in the digital domain. A proof-of-concept outphase power

amplifier is fabricated using the IBM 7WL SiGe BiCMOS process technology. The test chip

includes two class-E power amplifiers and the first 5.8GHz fully integrated Wilkinson power

combiner. The low-loss integrated combiner allows efficient outphase recombining while

providing the necessary input isolation for a robust outphase power amplifier.

The outphase power amplifier achieves an efficiency of 47% at the maximum output power

of 18.5 dBm. For an input Orthogonal Frequency Division Multiplexing (OFDM) signal of

32 sub-channels of 64-QAM, the adjacent channel power leakage ratio (ACPR) is better than

32dBc. The outphase power amplifier’s error vector magnitude (EVM) is better than -25dB

for up to 20dB of output dynamic range.

3

4

To my parents Kim-Anh and Hung,

and my wife Ha.

5

6

Acknowledgements

Many people have contributed to the successful of this project. First and foremost, I would

like to thank Professor Sodini for his unwavering support and caring guidance, especially

during the early months of the project when the proposed solution was both unconventional

and questionable. Ha and I also have the honor of having Charlie and Anne at our wedding.

Next, I would like to thank the committee members, Professor Dawson and Professor

Chandrakasan, for their help and encouragement during the course of the project. Professor

Wornell’s guidance is vital in the theoretical analysis of the outphase concept in OFDM

systems.

Nir built the custom receiver that is instrumental in proving the performance and merit of the

outphase power amplifier. Todd is always available to spot holes in my proofs and help with

any Unix issues. He and John also make sure that I have enough caffeine in the afternoon.

The system experts, Andy, Farinaz, and Everest are helpful and deliberate in our many

discussions. Lunal and Albert industry experience is an excellent resource for everyone in

the office. I would also like to thank all the members of the H. S. Lee and Sodini research

groups for a great office environment and many memorable social events.

Our group administrator Rhonda Maynard does a superb job with all the forms and

scheduling, always with a bright smile.

I am especially grateful for the help of a good friend, Donhee. All the necessary equipments

for chip-on-board setup are available from Donhee’s laboratory at Harvard University.

Finally, my best man Miles, buddies Stuart and the-mad-Hungarian Zoltan deserve special

recognitions for their generous donations to the much needed college fund. It is hard to

imagine not being able to hang out with them as often.

7

8

Contents

Chapter 1

Introduction..................................................................................... 15

1.1

Motivation............................................................................................................... 15

1.2

Literature Reviews on Linearization Techniques ................................................... 16

1.2.1

Polar and Cartesian Feedback Techniques ..................................................... 16

1.2.2

Feedforward Linearization.............................................................................. 18

1.2.3

Predistortion.................................................................................................... 18

1.2.4

Envelope Elimination and Restoration ........................................................... 19

1.2.5

Linear Amplification Using Nonlinear Components (LINC)......................... 20

1.3

Outphase Amplifying.............................................................................................. 20

1.4

Outphase Literature Reviews.................................................................................. 21

1.4.1

Re-combiner Complexity................................................................................ 21

1.4.2

Mismatch Control ........................................................................................... 22

1.4.3

Overall System Efficiency .............................................................................. 22

1.5

Research Contributions........................................................................................... 22

1.6

Thesis Overview ..................................................................................................... 23

Chapter 2

Power Amplifiers Efficiency .......................................................... 25

2.1

Conditions for 100% Efficiency ............................................................................. 25

2.1.1

First Condition: Zero Power Dissipation in the Transistor............................. 26

2.1.2

Second Condition: Fundamental Power Only................................................. 28

2.2

Switching Power Amplifiers with Theoretical 100% Efficiency ........................... 28

2.2.1

Class-E ............................................................................................................ 28

2.2.2

Class-F ............................................................................................................ 31

2.2.3

Other Switching Classes (-F -1, -E/Fx) ............................................................ 32

2.2.4

Switching Power Amplifiers Linearity ........................................................... 33

2.3

Conducting-Mode Power Amplifiers...................................................................... 34

2.3.1

Operating Principle and Efficiency................................................................. 34

2.3.2

Performance Characteristics of Conducting-Mode Power Amplifiers ........... 35

2.4

Summary ................................................................................................................. 37

Orthogonal Frequency Division Multiplexing.............................. 39

Chapter 3

3.1

3.2

OFDM Constructions.............................................................................................. 39

OFDM Peak-to-Average Power Ratios .................................................................. 41

Chapter 4

4.1

Outphase Amplifying – System Analysis...................................... 47

Digital Outphase Conversion.................................................................................. 47

9

4.2

Amplitude Variation Control .................................................................................. 49

4.3

Digital Outphase Conversion in System Simulation .............................................. 52

4.4

Effect of Mismatch ................................................................................................. 54

4.4.1

Error Vector Magnitude.................................................................................. 54

4.4.2

Bit-Error Rate.................................................................................................. 57

4.5

Summary ................................................................................................................. 58

Chapter 5

An Integrated Outphase Power Amplifier .................................... 59

5.1

Class-E Design........................................................................................................ 60

5.1.1

Design Equations and Parameters................................................................... 61

5.1.2

Differential Class-E with Driver Stage ........................................................... 62

5.1.3

Simulation Results .......................................................................................... 65

5.1.4

Corner Simulation........................................................................................... 67

5.2

Power Combiner Design ......................................................................................... 68

5.2.1

Wilkinson Power Combiner............................................................................ 68

5.2.2

Shielded Coplanar Stripline ............................................................................ 70

5.2.3

A Shielded Coplanar Stripline Wilkinson Combiner...................................... 72

5.3

Summary ................................................................................................................. 73

Chapter 6

Experimental Results...................................................................... 75

6.1

Class-E and Power Combiner Measurements......................................................... 75

6.2

Outphase Power Amplifier Efficiency.................................................................... 78

6.3

Overall Outphase Power Amplifier Measurements ................................................ 79

6.3.1

Generating the Outphase Signals .................................................................... 79

6.3.2

Decode the Output Signal for EVM Measurements ....................................... 82

6.3.3

Results............................................................................................................. 84

Chapter 7

7.1

7.2

Conclusion ....................................................................................... 87

Average Efficiency Comparison............................................................................. 88

Future Related Research ......................................................................................... 90

10

List of Figures

Figure 1-1: (a) Cartesian Feedback Loop (b) Polar Feedback Loop ..................................... 17

Figure 1-2: Basic Feedforward Power Amplifier .................................................................. 18

Figure 1-3: Basic Predistortion Block Diagram..................................................................... 19

Figure 1-4: Conceptual Block Diagram of an Envelope Elimination and Restoration PA ... 19

Figure 1-5: LINC Principle Diagram..................................................................................... 20

Figure 2-1: General Power Amplifier Model......................................................................... 25

Figure 2-2: (a) Switching MOS Transistor (b) Small-signal Equivalent Circuit Model ....... 27

Figure 2-3: Simplified Model with Ideal Switch and Parasitic Capacitor ............................. 27

Figure 2-4: Class-E Schematics ............................................................................................. 28

Figure 2-5: Basic Class-E Operation ..................................................................................... 29

Figure 2-6: Class-E Waveforms............................................................................................. 30

Figure 2-7: Class-F Schematics ............................................................................................. 31

Figure 2-8: Class-F (a) and Class-F-1 (b) Waveforms ........................................................... 32

Figure 2-9: Inverse Class-F Schematic .................................................................................. 33

Figure 2-10: Input-to-Output Waveforms of Conducting-Mode Power Amplifiers ............. 34

Figure 2-11: Characteristic Waveforms of a Power Amplifier with Conduction Angle α.... 35

Figure 2-12: Drain Harmonic Currents as a Function of the Conduction Angle................... 37

Figure 3-1: N Parallel Orthogonal Sub-Channels by Using IDFT ........................................ 39

Figure 3-2: OFDM Transmitter Architecture ........................................................................ 40

Figure 3-3: PAPR of Single Channel with Various QAM Levels ......................................... 41

Figure 3-4: Additional PAPR Caused by OFDM .................................................................. 42

Figure 3-5: Amplitude Probability Distribution (128 Sub-Channels OFDM of 256-QAM). 43

Figure 3-6: BER vs. PAPR for Various Clipping Degrees.................................................... 45

Figure 4-1: Outphase Concept with Digital Amplitude-to-Phase Conversion ...................... 47

Figure 4-2: Digital Outphase Conversion .............................................................................. 49

Figure 4-3: Outphase Analog Waveforms Exhibit Significant Amplitude Variation............ 50

Figure 4-4: Signal-space Constellations for QPSK, Offset QPSK and π/4-QPSK................ 51

Figure 4-5: Optimal Outphase Conversion for Amplitude Variation Control....................... 52

Figure 4-6: OFDM Architecture with Outphase Amplifying ................................................ 53

Figure 4-7: Envelope Variation w/ and w/o Optimal Outphase Assignment ........................ 54

Figure 4-8: EVM Definition .................................................................................................. 55

Figure 4-9: Outphase EVM with Gain and Phase Mismatch of α and δº.............................. 56

Figure 4-10: Normalized EVM dues to Mismatch ................................................................ 56

Figure 4-11: BER vs. Voltage Mismatch (OFDM 128 sub-channels of 256-QAM)............. 57

Figure 4-12: BER vs. Phase Mismatch (OFDM 128 sub-channels of 256-QAM)................ 58

Figure 5-1: Die Photo............................................................................................................. 59

Figure 5-2: Test Chip Includes Two Class-E PAs and a Power Combiner ........................... 60

Figure 5-3: Class-E with Ideal Transistor Switch.................................................................. 61

Figure 5-4: Ideal Class-E Waveforms.................................................................................... 61

Figure 5-5: Class-E in Differential Configuration ................................................................. 62

Figure 5-6: (a) Differential Inductor with Center Tab (b) Differential Transformer............ 63

Figure 5-7: Differential Class-E Power Amplifier Using Center-Tapped Inductors............. 64

Figure 5-8: Differential Class-E PA with Driver Stage ......................................................... 65

11

Figure 5-9: Switching Transistor Model and Additional Shunt Capacitor CP ....................... 65

Figure 5-10: Simulation Class-E Waveforms (T=1/5.8GHz) ................................................ 66

Figure 5-11: Simulated Efficiency and Output Power vs. Supply Voltage ........................... 67

Figure 5-12: Amplitude Mismatch Due to Process Variation ............................................... 67

Figure 5-13: Wilkinson Power Combiner.............................................................................. 68

Figure 5-14: Analyzing the Wilkinson Combiner in Odd and Even Modes.......................... 69

Figure 5-15: Integrated Circuit Coplanar Stripline................................................................ 71

Figure 5-16: Coplanar Stripline with Floating Metal Shields................................................ 72

Figure 5-17: Effects of Metal Shields.................................................................................... 72

Figure 5-18: Chip Layout of the Coplanar Stripline Wilkinson Combiner ........................... 73

Figure 6-1: Laser Trim Locations and Intermediate Test Points for Individual Block

Measurements ......................................................................................................................... 75

Figure 6-2: Test Board ........................................................................................................... 76

Figure 6-3: Class-E Measured Output Power and Efficiency................................................ 77

Figure 6-4: Measured Wilkinson Combiner S-Parameters.................................................... 77

Figure 6-5: Efficiency Measurement Setup ........................................................................... 78

Figure 6-6: Outphase Power Amplifier Efficiency vs. Pout .................................................... 79

Figure 6-7: Construction of Outphase Signals for OFDM Measurements ............................ 80

Figure 6-8: OFDM Construction Block Diagram inside a Signal Generator ........................ 80

Figure 6-9: Block Diagram for Generating Outphase Signals Procedure.............................. 81

Figure 6-10: Complete Test Setup for Outphase PA Measurements with OFDM Signals ... 83

Figure 6-11: 50Ω Resistor Combiner for Calibration............................................................ 83

Figure 6-12: Gain Adjustment for Compensating Phase Mismatch ...................................... 84

Figure 6-13: Output Power Spectral Density......................................................................... 85

Figure 6-14: 64-QAM Symbols w/o Mismatch ..................................................................... 85

Figure 6-15: 64-QAM Symbols w/ 2% Mismatch................................................................. 85

Figure 6-16: 64-QAM Symbols w/ 5% Mismatch................................................................. 85

Figure 6-17: Measured EVM ................................................................................................. 86

Figure 7-1: (a) Efficiency Comparison .................................................................................. 88

12

List of Tables

Table 5-1: Power Amplifier Specification............................................................................. 60

Table 5-2: Summary of Class-E Equations and Waveforms ................................................. 61

Table 7-1: Comparison with Previously Published Results................................................... 87

13

14

Chapter 1

Introduction

The performance of a wireless communication system depends heavily on its power amplifier

(PA). Specifically, the wireless system’s data rate is often determined by the power

amplifier’s linearity. In addition, by usually accounting for more than half of the whole

transceiver power budget, a power amplifier requires not only larger and heavier batteries for

longer communication time, but also bulky heat dissipating panels.

Power amplifiers have been well studied and developed since the early days of vacuum tubes

and continued on throughout the modern era of solid-state transistors. Many classes of

operation have been proposed, and the efficiency-linearity tradeoff has been well understood.

However, most of the early study on power amplifiers has been done at low frequency range,

mostly for audio applications and low-speed data communications, from a few kHz to tens of

MHz. With the explosion of cellular phones and wireless communication networks in the

nineties, there has been a renewed interest in power amplifiers. Modern power amplifier

designers face a much tougher environment. First, the linearity requirement has been

significantly increased to accommodate many new and intricate modulation techniques.

Second, efficiency becomes much more critical with the smaller and lighter trend toward

portable devices.

Fortunately, modern design environment also offers a few advantages. First, advanced

integrated circuit (IC) technologies make it possible for larger and more complex circuits

with better matching control and accurate calibration. Second, designers can now make use

of very powerful digital signal processors with little or tolerable penalty in power

consumption. Taking advantages of these two new capabilities, many complex bias-controls

and feedback techniques have been explored in hope of simultaneously achieving high

efficiency and good linearity in power amplifiers.

1.1 Motivation

A tradeoff between linearity and efficiency exists in conventional power amplifiers.

Conducting class power amplifiers, such as class-A and -AB, offer great linearity but are

very inefficient [1,2]. On the other hand, switching classes, such as class-E and -F, have

excellent efficiency, but are very non-linear [3,4]. Traditionally, non-linear, switching class

15

PAs can only be used in phase or frequency modulated systems, while all amplitude

modulated systems require conducting class PAs with good linearity. Modern wireless

communication systems usually employ intricate modulation schemes, such as OFDM with

multi-channels of Quadrature Amplitude Modulation (QAM), to maximize bandwidth

efficiency. Such modulation often results in amplitude modulated signals with large peak-toaverage power ratio (PAPR) that requires PAs with extremely good linearity. While the

linearity requirement increases, the demand for higher efficiency also exhibits an upward

trend due to the desire for longer battery life and higher data rates. Power amplifier

designers are facing the tremendous challenge to overcome the efficiency-linearity tradeoff.

1.2 Literature Reviews on Linearization Techniques

Linearization techniques can be loosely divided into two sub-categories depending on the

type of power amplifiers they employ. The first linearization category extends the linear

output power range of conventional power amplifiers so that the PA can operate linearly over

a large output range where it is most efficient. The power amplifiers employed by this

category are usually of the conduction classes (-AB, -B, and -C), which already have some

degree of linearity. This category includes, among others, the Polar and Cartesian feedback,

feedforward, and predistortion techniques.

On the other hand, the second category of linearization employs switching power amplifiers

that are highly non-linear, for the inherently higher efficiency, while manipulating the overall

system to achieve the required linearity. This category includes the Envelope Elimination

and Restoration (ERR) technique, and LInear amplification using Nonlinear Components

(LINC).

1.2.1 Polar and Cartesian Feedback Techniques

The Polar and Cartesian feedback techniques are conceptually negative feedback systems

that have been well studied and are popular in the audio and low frequency applications [5].

However, in order to apply negative feedback to an RF transmitter, a high gain and stable

analog feedback loop is needed at the carrier frequency in the gigahertz range for modern

wireless standards. Such a feedback loop is virtually unrealizable in current technologies.

Therefore, an indirect system is employed, where the RF output is down-converted to

baseband. The feedback loop is closed at baseband where error corrections are performed.

In a Cartesian feedback system shown in Figure 1-1(a), the corrections are then performed on

the Cartesian coordinates of the quadrature symbols I and Q. Similarly, corrections are done

on the polar coordinates of amplitude and phase, in the case of Polar feedback as shown in

Figure 1-1(b).

Because of the indirect feedback loop, the Polar and Cartesian feedback techniques are

inherently narrow band and can provide linearization for systems with limited bandwidth (on

the order of a few hundred kilohertz). A major design consideration for the Cartesian

16

feedback is the phase alignment between the up-convert and down-convert mixers [6]. In

addition, the linearity of the overall system depends on the precision of the feedback

corrections as well as the linearity and bandwidth of the down-converters [7]. The most

distinguishing advantage of the Cartesian feedback loop is its resilience against process

variations, temperature fluctuations, as well as the lack of an accurate model for the power

amplifier.

Figure 1-1: (a) Cartesian Feedback Loop (b) Polar Feedback Loop

17

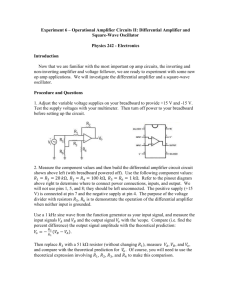

1.2.2 Feedforward Linearization

The basic principle of feedforward linearization [8,9] is shown in the block diagram of

Figure 1-2. This is an open loop, two-amplifier system with a main, non-linear power

amplifier and a smaller auxiliary amplifier. The output of the main amplifier is coupled and

compared to the original input. The difference is amplified using the auxiliary amplifier then

added to the main amplifier output to achieve a linear overall output.

Figure 1-2: Basic Feedforward Power Amplifier

There are several challenges in implementing a feedforward power amplifier. First, the

delays of the two amplifiers have to be replicated precisely in the two signal paths to

maintain the overall signal integrity. This requires accurate models for both main and

auxiliary amplifiers. In addition, in order to add the two amplifiers outputs, a power

combiner is required. Finally, unlike the Cartesian feedback, the feedforward technique is an

open loop setup that makes it vulnerable to environmental changes.

On the other hand, because of the open loop setup, feedforward linearization can operate at a

higher bandwidth. A simulated feedforward system with 7MHz bandwidth has been reported

in [10].

1.2.3 Predistortion

Conceptually, the nonlinear behavior of the power amplifier can be characterized and

preemptively undone by a predistorter inserted right before the power amplifier [11].

However, such a setup is an open loop technique that is highly vulnerable to process

variation, operating temperature, and environment changes. Therefore, predistortion is

usually employed in tandem with feedback loops as described in Figure 1-3. Instead of a

predetermined predistorter, an adaptive version [12] is employed using the two feedback

signals to correct for the power amplifier characterization as well as the overall system signal

integrity. The main difference between the predistortion feedback loop and that of the

Cartesian feedback is that it does not have to operate continuously. The rate of change of the

environment is presumably very slow. Therefore, predistortion does not suffer a bandwidth

limitation. However, it still needs an accurate model of the power amplifier. In addition,

18

circuit complexity could incur significant power overhead that degrades the overall system

efficiency.

A predistortion linearizer has been successfully implemented for class-AB power amplifier

[13].

Figure 1-3: Basic Predistortion Block Diagram

1.2.4 Envelope Elimination and Restoration

Figure 1-4: Conceptual Block Diagram of an Envelope Elimination and Restoration PA

Envelope elimination and restoration, originally proposed by Kahn [14], separates the RF

input signal into phase, using the limiter, and amplitude, using the peak detector as shown in

Figure 1-4. A highly efficient switching power amplifier is then used to amplify the phase

modulated signal. The envelope amplitude information is used to modulate the PA’s power

supply, which restores the amplitude information to the output signal.

The key challenge to the envelope elimination and restoration technique is the

implementation of an efficient and high-bandwidth switching power supply that can

accommodate the signal bandwidth while maintaining respectable overall efficiency. In

addition, phase matching between the two signal paths is critical. A 49% efficiency, 25MHz

19

bandwidth power amplifier using envelope elimination and restoration technique has been

reported in [15].

1.2.5 Linear Amplification Using Nonlinear Components (LINC)

Another way to overcome the linearity-efficiency tradeoff is to enable the use of high

efficiency, non-linear power amplifiers for linear systems. This general technique is referred

to as LInear amplification using Nonlinear Components [16]. Figure 1-5 describes the

general principle of LINC. An amplitude modulated signal x(t ) is first decomposed into two

signals s1 (t ) and s2 (t ) that can be amplified using two highly efficient, non-linear power

amplifiers. The PAs’ outputs, y1 (t ) and y2 (t ) , are then recombined to yield y (t ) for

transmission.

Figure 1-5: LINC Principle Diagram

Ideally, to be suitable for linear amplification, the output needs to be a linear scale of the

original input as described in (1-1), where G is the constant gain of the composite power

amplifier.

y (t ) = G ⋅ x(t )

(1-1)

In addition, in order to employ highly efficient, non-linear power amplifiers, the decomposed

signals s1 (t ) and s2 (t ) can not have amplitude modulation. Furthermore, the decomposition

has to be such that its inverse function, which is performed by the re-combiner block, can be

efficiently implemented using analog circuitry.

1.3 Outphase Amplifying

One method of decomposition is the outphase amplifying, which was originally proposed by

Chireix in 1935 [17]. An amplitude modulated signal can be represented as a sum of two

constant amplitude, phase -modulated signals as described in (1-2).

20

Amax

A

cos(ωt + θ + φ ) + max cos(ωt + θ − φ )

2

2

a (t )

with Amax = max a (t )

φ (t ) = cos −1

Amax

a(t ) cos(ωt + θ ) =

(1-2)

Essentially, the decomposition is the amplitude-to-phase inverse cosine function that results

in two constant amplitude signals that can be amplified using two highly efficient switching

PAs. The re-combiner is simply the addition of the two power amplifiers’ outputs. A valid

amplitude-to-phase inverse cosine conversion can be guaranteed by normalizing the

amplitude to its absolute maximum value Amax .

The outphase amplifying technique can be described in the context of Figure 1-5 as follows,

• Input: x(t ) = a(t ) cos(ωt + θ )

• Decomposition: x(t ) = s1 (t ) + s2 (t )

•

•

•

•

a(t )

Amax

φ (t ) = cos−1

cos(ωt + θ + φ )

s1 (t ) =

A

2

max

s (t ) = Amax cos(ωt + θ − φ )

Amax = max a(t )

2

2

Power amplifiers’ gain: G

Intermediate outputs: y1 (t ) = G ⋅ s1 (t ) , y2 (t ) = G ⋅ s2 (t )

Re-combiner: y (t ) = y1 (t ) + y2 (t )

Total output: y(t ) = G ⋅ x(t )

Outphase amplifying is a very simple and elegant technique that allows the use of highly

efficient, non-linear switching power amplifiers in linear systems to simultaneously achieve

good linearity and high efficiency.

1.4 Outphase Literature Reviews

Published literature on the outphase technique has focused mainly on three issues: recombiner complexity, mismatch-control feedback, and overall system efficiency.

1.4.1 Re-combiner Complexity

One way to implement the re-combiner function is the “Chireix combiner”, which uses

simple inductors, capacitors, and transformers that can be easily integrated in today

technology [18,19]. However, the Chireix combiner can only be tuned for a very small range

of outphase angles. With outphase angles outside the tuned range, isolation between the two

21

power amplifiers’ outputs is poor, resulting in significant distortion that degrades the system

linearity. Recall from (1-2) that the outphase angle is a function of the signal amplitude,

small outphase angle range means only systems with a very tight range of amplitude

modulation can employ this particular implementation of the outphase amplifying technique.

It is reported in [20] that the Chireix combiner has a significant nonlinear effect compared to

the hybrid Wilkinson combiner, which offers better isolation across a wide range of

amplitudes, and that linearization is feasible only at the expense of reduced efficiency.

1.4.2 Mismatch Control

A feedback loop and calibration scheme to correct for any gain and phase imbalance among

the two outphase paths are analyzed in [21]. In order to avoid the bandwidth limitation of a

continuous feedback loop, the transmitter is alternating between transmit and correction

modes. In correction mode, a training sequence is used to build a lookup table to provide

gain and phase mismatch corrections during the subsequent transmit mode. Simulation

results are presented for QPSK (Quadrature Phase Shift Keying) and 16-QAM with more

than 40dB improvement in ACPR (from -30dBc to -70dBc). In a similar category, the effect

of quantization error with the hypothesis of a digital implementation of the signal

decomposition is studied in [22]. It is reported that a simulated ACPR of -62dBc can be

obtained for a π/4-shifted DQPSK (Differential Quadrature Phase Shift Keying) system with

9-bits DAC.

1.4.3 Overall System Efficiency

A power recycling technique is proposed in [23] by rectifying the signal and recouping the

energy that is normally dissipated on the combiner due to cancellation of completely out of

phase signal components. The reported experimental results are obtained from a test setup

using a discrete, off-chip hybrid power combiner. Using example modulations of QPSK, 16QAM, and 64-QAM, it is reported that a relative improvement between 33% and 83% on the

average power efficiency is possible.

1.5 Research Contributions

While the basic concept of outphase amplifying is straightforward, challenges exist in

implementation. First, the practical implementation of the outphase amplifying technique

critically depends on the accuracy and efficiency of the amplitude-to-phase conversion.

Implementing the inverse cosine and other trigonometric functions using analog circuitry is

non-trivial and inevitably complex. Second, for a robust outphase amplifier that is suitable

for a wide variety of modulation schemes, complete isolation is needed between the two

power amplifiers’ outputs to prevent them from loading each other. Therefore, hybrid power

combiners, which rely on quarter-wave length transmission lines to provide isolation, are

required in summing the two output ports. For a fully integrated solution, it is very

22

challenging to design efficient and size-constrained power combiners. It could be argued that

the outphase amplifying technique, despite its early introduction in the 1935, never gained

widespread popularity because of these two challenges.

Solving the above two challenges are the main contributions of this thesis to the

understanding and advances of the outphase power amplifying technique. First, an optimal

digital amplitude-to-phase conversion scheme, that takes advantage of the vast computational

power of digital technology, is proposed to achieve the accuracy and efficiency required for

the outphase conversion. Second, an outphase power amplifier with a fully integrated and

low-loss power combiner at 5.8GHz has been successfully fabricated, for the first time. An

experimental verification of the suitability of the outphase concept in modern wireless

systems such as multi-channels OFDM/QAM has been demonstrated. A complete analysis

of the outphase power amplifier efficiency based on signal amplitude distribution is

presented during the evaluation of the outphase technique.

In addition, the effect of mismatch is analyzed and quantified using the general figure of

merit Error Vector Magnitude (EVM), as well as the more system specific bit-error-rate

(BER) in the application of multi-channels OFDM/QAM systems.

The test chip answers the two critical challenges in current power amplifier designs. First, it

shows that the outphase power amplifier simultaneously achieves good linearity and high

efficiency. Second, the fully integrated power combiner combines the output power of two

individual power amplifiers, and effectively doubles the maximum achievable output power

for a given transistors’ breakdown voltage.

1.6 Thesis Overview

For background review, Chapter 2 examines the conditions for 100% efficiency power

amplifiers and concludes that only switching class power amplifiers can offer 100%

efficiency. A brief review of several power amplifier switching classes is then presented as

examples of 100% efficiency power amplifiers. Chapter 2 concludes with a review of

conducting-mode power amplifiers that sacrifice the first condition for 100% efficiency to

achieve some degree of linearity. Next, Chapter 3 explains the construction and

characteristics of OFDM signals. Understanding OFDM construction is relevant in

subsequent system simulation implementation and measurement setups. The chapter also

provides a detailed look into peak-to-average power ratio of OFDM systems as well as more

probable PAPR numbers from a custom simulation of 231 OFDM symbols.

Chapter 4 focuses on the theoretical analysis of the outphase amplifying concept. The digital

amplitude-to-phase conversion is introduced and analyzed here. In addition, an optimal

outphase channel assignment method is also proposed to significantly reduce the outphase

envelope amplitude variations. The digital outphase conversion with optimal channel

assignment is implemented in a custom simulation to characterize the error-mismatch

sensitivity of the outphase concept.

23

The design of a proof-of-concept integrated outphase power amplifier is presented in Chapter

5. First, a differential class-E power amplifier is designed using center-tapped differential

inductors and transformer to minimize the chip area. Second, the first integrated differential

5.8GHz Wilkinson power combiner is presented. The integration is possible by using thin

perpendicular shielding strips of lower level metals to both reduce the combiner’s size as

well as its substrate-coupling loss.

Chapter 6 explains the test setups and measurement procedures to separately characterize the

class-E power amplifier and the Wilkinson combiner. Next the overall outphase power

amplifier performance in OFDM systems is measured to show the outphase amplifying

technique’s capability in modern linearity-demanding modulation systems while at the same

time achieves much better efficiency than conventional linear power amplifiers.

Finally, Chapter 7 summarizes the project results. The proof-of-concept outphase power

amplifier achieves a 47% maximum efficiency with an ACPR of -32dBc for an OFDM signal

with 32 sub-channels of 64-QAM. A comprehensive efficiency and average power

consumption comparison is made among three linear power amplifiers: the outphase, a

conventional class-A, and an adaptive class-A. Among the three, the outphase power

amplifier consumes the least average power in a high linearity requirement system of multichannels OFDM/QAM.

24

Chapter 2

Power Amplifiers Efficiency

This chapter reviews the efficiency of various power amplifier topologies. Instead of the

traditional approach of categorizing power amplifiers into classes of operation then analyzing

each class independently, a general power amplifier model is introduced, from which a

universal efficiency expression is derived. Next, conditions to achieve the theoretical 100%

efficiency are determined. Studying these conditions from a power standpoint, without

specific circuit implementation, provides better intuition for understanding power amplifier

efficiency and linearity tradeoff. Several power amplifier switching classes are then

analyzed as examples of specific implementations of the 100% efficiency conditions.

Finally, the efficiency-linearity tradeoff is demonstrated with several power amplifier

conducting classes where the conditions for 100% efficiency are forgone in exchange for

linearity.

2.1 Conditions for 100% Efficiency

Figure 2-1: General Power Amplifier Model

25

Figure 2-1 shows a typical power amplifier schematic with a common-source transistor

driving the 50 ohms antenna via a passive matching network. The transistor is connected to

the power supply via a Radio Frequency Choke (RFC) to minimize resistive loss while

allowing the drain voltage to swing higher than the supply voltage VDD . The main function

of the matching network is to transform the antenna load into appropriate loading impedance

presented to the transistor, which together with the gate biasing condition, determine the

operational characteristics of the power amplifier.

The transistor is driven with an input power Pin at the gate, while the supply power Psup is

provided via the RFC. Consider the power flow at the drain, the supply power can be

separated into two parts: the power being dissipated on the transistor Pdissipate , and the power

delivered to the matching network Pload ,

Psup = Pdissipate + Pload

(2-1)

Depending on the input drive level and the matching network, Pload generally contains the

fundamental and higher order harmonic components,

Pload = P0 + P1 + P2 + ...

(2-2)

To comply with Federal Communications Commission (FCC) spectral requirements, all the

higher order harmonics are filtered out leaving only the fundamental power, P0 , for

transmission at the antenna. The power amplifier efficiency is defined as the ratio of the

fundamental output power and the supply power.

η=

P0

Psup

(2-3)

From the power expressions in (2-1), (2-2), and (2-3), the efficiency can be rewritten as,

η=

P0

Pdissipate + P0 + P1 + P2 + ...

(2-4)

Clearly, to achieve the maximum 100% efficiency, two conditions have to be met:

Pdissipate = 0 , and P1 = P2 = P3 = L = 0 .

2.1.1 First Condition: Zero Power Dissipation in the Transistor

The first condition, Pdissipate = 0 , requires zero power being dissipated in the transistor.

Theoretically, this condition can be satisfied by operating the transistor as a switch, where

26

there is no overlap between the drain voltage and current, resulting in zero power dissipation

in the transistor. However, in switching condition, there is a non-negligible equivalent drainto-source capacitor whose discharging mechanism could affect the overall efficiency of the

power amplifier.

Figure 2-2: (a) Switching MOS Transistor (b) Small-signal Equivalent Circuit Model

(c) Equivalent Switching MOS Transistor Model

First, the origin of this drain-to-source capacitor is explained in Figure 2-2. A commonsource switching transistor in Figure 2-2(a) has an equivalent small-signal model as shown in

Figure 2-2(b), where the gate is effectively grounded due to the discrete-level nature of the

switching gate input voltage. The result is an equivalent drain-to-source capacitor cds that is

the sum of c gd and cdb . Therefore, a switching MOS transistor can be represented by a

parallel combination of an ideal switch and the equivalent capacitor cds .

Figure 2-3: Simplified Model with Ideal Switch and Parasitic Capacitor

The transistor in the general power amplifier model in Figure 2-1 is replaced with its

equivalent switching model as shown in Figure 2-3. The effect of the drain-to-source

27

capacitor cds can now be analyzed. During the off stage, the switch opens and the capacitor

is charging up. The energy stored on the capacitor is then dissipated by a discharge current

through the switch during the on stage when the switch closes. The discharge current

represents an energy loss and a reduction in overall efficiency. Since the discharge current

occurs once per cycle, the loss increases linearly with the operating frequency. One way to

eliminate this loss mechanism is to drive the drain voltage to zero right before switching on.

That way there is no charge left on the output capacitor that can be discharged through a

closed switch. This technique is generally known as Zero Voltage Switching (ZVS). In

order to have zero power dissipation in the transistor, the zero voltage switching condition

has to be satisfied, in addition to the transistor operating as a lossless switch.

2.1.2 Second Condition: Fundamental Power Only

The second condition, P1 = P2 = P3 = L = 0 means the power delivered to the matching

network contains only the fundamental power P0 . It is important to realize that the voltage

and current at the matching network can have high order harmonics, as long as for each

harmonic other than the fundamental, the corresponding voltage and current do not overlap.

This condition can be satisfied by using appropriate output matching networks. Each

matching network methodology represents a specific class of power amplifiers.

2.2 Switching Power Amplifiers with Theoretical 100% Efficiency

2.2.1 Class-E

Figure 2-4: Class-E Schematics

28

An example of 100% efficiency power amplifiers is the class-E power amplifier that uses a

series resonator LS - C S at the operating frequency as the matching network. The resonator

blocks the DC and higher order harmonics, leaving only the fundamental current into the

matching network. Therefore, regardless of the harmonic content of the drain voltage, the

power delivered to the matching network contains only the fundamental, satisfying the

second condition for 100% efficiency. As for the first condition of zero voltage switching,

class-E power amplifier uses an additional shunt capacitor C P at the drain. The value of this

shunt capacitor, together with the resonator, provides two design parameters that can be used

to set the capacitor (drain) voltage to zero right before switching on to satisfy the ZVS

condition.

In order to analyze the operational waveforms of a class-E power amplifier, the transistor is

replaced with an ideal switch and an output parasitic capacitor cds that is lumped together

with the additional shunt capacitor C P into the total capacitor C1 as shown in Figure 2-5.

Again, the resonator forces its current to be pure sinusoidal. Assume the RFC is large

enough to conduct only a DC supply current, the total current into the switch and shunt

capacitor is an offset sinusoidal,

itotal (θ ) = I dc + I rf sin (θ − θ 0 )

with θ = ωt and θ 0 is the initial phase

(2-5)

Figure 2-5: Basic Class-E Operation

This current is commutated between the switch and the shunt capacitor depending on the

switch’s state. During the on stage, the switch conducts the offset sinusoidal current, and the

capacitor voltage is zero. During the off stage, the capacitor is charging up and its voltage is

the integration of the offset sinusoidal current. Assuming a 50% switching duty cycle, the

relevant currents and voltage are as follows,

29

vd (θ ) =

I + I rf sin (θ − θ 0 ) 0 < θ ≤ π

isw (θ ) = dc

0

π < θ ≤ 2π

(2-6)

0

0 <θ ≤π

ic (θ ) =

I dc + I rf sin (θ − θ 0 ) π < θ ≤ 2π

(2-7)

θ

0

0 <θ ≤π

1

1

ic (θ )dθ =

∫

ωC1 0

ωC1 I dc (θ − π ) − I rf [cos(θ − θ 0 ) + cos(θ 0 )] π < θ ≤ 2π

(2-8)

Figure 2-6: Class-E Waveforms

By selecting the appropriate values for the resonator LS - C S and shunt capacitor C P , the

relative phase of the offset sinusoidal current can be adjusted such that the drain voltage is

driven to zero right before switching on, vd (2π ) = 0 . Typical waveforms of a class-E power

amplifier are summarized in Figure 2-6.

30

2.2.2 Class-F

Another example of 100% efficiency is the class-F power amplifier as shown in Figure 2-7.

Here the matching network includes a quarter-wavelength transmission line and a parallel

LP - C P resonant tank, both at the operating frequency. C ac is a large coupling capacitor to

block the DC current from going into the load.

Figure 2-7: Class-F Schematics

Recall that a quarter-wavelength transmission line reciprocates the load impedance, while a

half-wavelength line preserves the load impedance,

Z 02

for l =λ/4

ZL

Z in = Z L for l =λ/2

Z in =

(2-9)

The resonant tank creates a short at all harmonics except the fundamental. For all even

harmonics, the same short is presented to the drain since the transmission line appears as

some integer multiples of a half-wavelength. As a result, the drain voltage does not contain

any even harmonics. Also recall that the square wave contains only odd harmonics; the drain

voltage becomes a square wave. On the other hand, at all odd harmonics other than the

fundamental, the short created by the LP - C P tank is reciprocated into an open because the

transmission line appears as an odd multiple of quarter-wavelengths. The opens at odd

harmonics result in a load current ( iload ) without any odd harmonics except for the

fundamental, which takes the shape of half sinusoidal waveform (recall that the half

31

sinusoidal waveform contains only the fundamental and even harmonics). Therefore, by

limiting the drain voltage to contain only odd harmonics, and the load current to only even

harmonics, class-F power amplifiers guarantee that only the fundamental power is generated

at the matching network, satisfying the aforementioned second condition for 100%

efficiency. Typical class-F waveforms are plotted in Figure 2-8(a).

The drain voltage waveform in Figure 2-8(a) also satisfies the zero voltage switching

condition, where it reaches zero right before switching on. Therefore, class-F power

amplifiers satisfy both conditions for 100% efficiency.

Figure 2-8: Class-F (a) and Class-F-1 (b) Waveforms

2.2.3 Other Switching Classes (-F -1, -E/Fx)

Several other power amplifier classes also offer 100% efficiency. Each uses a different

approach to shape the voltage and current waveforms for maximum efficiency. However, the

same two principle conditions apply: zero voltage switching, and fundamental power only at

the matching network.

The inverse class-F power amplifiers swap the drain voltage and current waveforms

compared to those of the normal class-F [24]. By presenting a short at all odd harmonics

besides the fundamental, and an open at all even harmonics, the inverse class-F has a square

drain current and a half sinusoidal drain voltage as shown in Figure 2-8(b). A typical

implementation of a class-F-1 is shown in Figure 2-9.

32

Figure 2-9: Inverse Class-F Schematic

Yet another example is the class-E/Fx family [25]. Instead of removing all the even

harmonics from the voltage and all odd harmonics from the current as the class-F power

amplifiers, the class- E/Fx power amplifiers retain a few even harmonics in the voltage, and

remove those extra even harmonics in the current to remain satisfying the second 100%

efficiency condition. The advantage of this approach is the ability to control the peak drain

voltage. The more even harmonics being retained in the drain voltage, the lower its peak

voltage gets. The class-E/Fx family becomes very attractive as technology scales with

smaller and smaller breakdown voltage.

Depending on the specific application, each class of switching power amplifiers is more

suitable than the other. The three selecting criteria are the peak value of the drain voltage,

simplicity of implementation, and tuning flexibility. In general, class-E is the simplest to

implement while having the largest peak drain voltage. It is most suitable for low to

moderate output power where the large peak drain voltage can be tolerated. On the other

hand, class-F and inverse class-F are more complicated to implement, but the peak drain

voltage is smaller. The hybrid class-E/Fx family falls in between; both in complexity and

peak drain voltage value.

2.2.4 Switching Power Amplifiers Linearity

From the above efficiency analysis, it is clear that 100% efficiency power amplifier has to be

of the switching type, where there is no voltage and current overlap at the drain. A switching

transistor is unquestionably non-linear from the fact that variations in the input power are not

reproduced at the output in any acceptable form. While the phase of the input signal is

preserved at the output, the amplitude of the output signal is not a function of the input

amplitude, rather it depends on the supply voltage and output matching network. As a result,

conventional switching power amplifiers, without qualification, are not suitable for linear

amplification.

33

In order to achieve linearity, the hard switching condition has to be avoided. Instead,

variations of the input power are reproduced at the output by allowing the input voltage to

modulate the drain current in the “pseudo-linear” transconductance region. That is the basis

for conducting-mode power amplifiers where the switching condition for 100% efficiency is

sacrificed for linearity.

2.3 Conducting-Mode Power Amplifiers

2.3.1 Operating Principle and Efficiency

Figure 2-10: Input-to-Output Waveforms of Conducting-Mode Power Amplifiers

An example of a conducting-mode power amplifier is shown in Figure 2-10. A gate input

voltage within the pseudo-linear transconductance region creates a proportional drain current

at the output. The drain current, in turns, modulates the drain voltage, depending on the load

impedance presented at the drain. A change in the input drive results in a change in the drain

current, and subsequently a proportional change in the output voltage as described by the

three thick arrows in Figure 2-10. Depending on the linearity of the transistor’s

transconductance, a linear relationship between the input and output voltages is achieved.

34

Evaluating the waveforms in Figure 2-10 under the conditions for 100% efficiency developed

in previous sections, several observations can be made.

•

•

•

Drain voltage and current overlap continuously exists in the example waveforms,

resulting in power being continuously dissipated in the transistor. This is a violation

of the first condition for 100% efficiency developed in previous sections.

The amount of overlap, and the energy being dissipated in the transistor, can be

reduced by forcing the drain current to be zero for a portion of each period. This is

accomplished by lowering the initial gate bias voltage, which is the basis for reduced

conduction angle classes of power amplifiers (i.e. -AB, -B, and -C). The power

amplifier efficiency is a function of the gate bias voltage, or conduction angle.

In reduced conduction mode, the drain current is clipped to zero for a portion of each

period, resulting in higher order harmonic content in the drain current. Therefore, in

order to satisfy the second 100% efficiency condition of only fundamental power

delivered into the matching network, all harmonics have to be removed from the drain

voltage. As a result, the drain voltage in conducting-mode power amplifiers is a

usually pure sinusoid at the fundamental frequency.

2.3.2 Performance Characteristics of Conducting-Mode Power

Amplifiers

Figure 2-11: Characteristic Waveforms of a Power Amplifier with Conduction Angle α

The efficiency and linearity performance of conducting-mode power amplifiers can be

quantified by examining the harmonic content of the drain current as a function of the bias

condition. Figure 2-11 shows the general input and output waveforms on a power amplifier

with a conduction angle α. The drain current is a clipped sinusoid, where the clipping occurs

35

when the gate voltage is less than the transistor’s threshold voltage. On the other hand, the

drain voltage is tuned to pure sinusoidal without any clipping to guarantee only the

fundamental power is being delivered to the matching network as discussed in the previous

section.

The conduction angle is used to classify conducting-mode power amplifier. Power

amplifiers operate in class-A have a full conduction angle of 2π. The class-B conduction

angle is π, where the drain current is perfectly half sinusoid. Class-C power amplifiers

conduction angle is less than π.

The drain current in Figure 2-11 can be expressed in terms of the conduction angle as

follows,

I + (I max − I q )cos θ

id (θ ) = q

0

α

α

α

<θ ≤

2

2

otherwise

−

(2-10)

Iq

where cos =

2 I max − I q

Replacing the initial drain bias current I q by the conduction angle α ,

α

α

I max (cos θ − cos(α 2 ))

− <θ ≤

id (θ ) =

1 − cos(α 2 )

2

2

0

otherwise

(2-11)

From (2-11), the harmonic content of the drain current as well as the power amplifier

efficiency can be calculated as a function of the conduction angle [26]. A plot of the drain

harmonic content versus the conduction angle is shown in Figure 2-12(a), while the

efficiency curve is plotted in Figure 2-12(b).

Several observations can be made from the plot of the drain harmonic currents.

•

•

•

•

As the conduction angle is reduced from 2π, the efficiency increases as expected due

to the reduction in drain voltage and current overlap. This is further evident by the

decrease in the DC supply current.

As the conduction angle is reduced, higher order harmonic currents increase.

A class-A power amplifier has a 2π conduction angle and a maximum efficiency of

50%. For a class-B power amplifier, the conduction angle is π, and its efficiency is

π/4 or 78.5%.

Theoretically, a class-C power amplifier with a zero conduction angle can achieve

100% efficiency. However, this is the detrimental case where the output power is

also reduced to zero as shown by the fundamental and harmonic content of the drain

current.

36

Figure 2-12: Drain Harmonic Currents as a Function of the Conduction Angle

2.4 Summary

This chapter has introduced a power model to facilitate a general power amplifier efficiencylinearity tradeoff analysis. In order to achieve the theoretical 100% efficiency, power

amplifiers have to operate in the switching condition where the relationship between the

output and input amplitudes is highly non-linear. Beside lossless switching operation, the

zero voltage switching condition also has to be satisfied to eliminate energy loss due to

capacitor discharging during on-off transitions. Switching classes are categorized by the

implementation of the output matching network.

37

Conducting class power amplifiers forgo the switching condition to achieve linearity. Power

amplifiers in conducting classes are characterized by their conduction angle, which

determines both the power amplifier linearity and efficiency. A larger conduction angle

corresponds to higher linearity and lower efficiency.

38

Chapter 3

Orthogonal Frequency Division Multiplexing

Orthogonal Frequency Division Multiplexing is a multi-carrier modulation that has been

adopted as the standards for Wireless Local Area Networks, such as the 802.11a in the US

and HIPERLAN/2 in Europe. The basic idea of OFDM is to transmit blocks of symbols in

parallel by employing a number of closely-spaced orthogonal carrier frequencies. The two

most distinct advantages of OFDM are the elimination of elaborate equalization, and the

ability to adapt different sub-carriers to use different modulations depending on the channel

conditions [27,28]. The major drawback for OFDM is the large peak-to-average power ratio

of the transmitting signal, requiring power amplifiers with great linearity over a large

dynamic range of output power, that are often very inefficient.

Because of the general popularity and the high linearity requirement of OFDM, an OFDM

system with multi-channels of 256-QAM will be used throughout this thesis to evaluate the

capability of the outphase concept, and the proof-of-concept outphase power amplifier test

chip. This chapter reviews the basic digital building blocks of an OFDM system. In

addition, the probability distributions of constellation magnitudes for various OFDM systems

are presented from a custom simulation capable of large number of samples for reliable

distributions. The amplitude probability distribution data is important because it represents

more realistic peak-to-average ratios as well as enables a system study into the effect of

clipping on bit-error-rate.

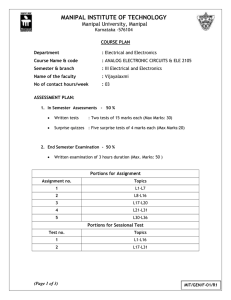

3.1 OFDM Constructions

Figure 3-1: N Parallel Orthogonal Sub-Channels by Using IDFT

39

The basic principle of OFDM is to transmit blocks of symbols in parallel using multiple

orthogonal carrier frequencies. This is accomplished by the Inverse Discrete Fourier

Transform (IDFT) function as shown in Figure 3-1. A group of symbols, one from each

parallel channel, forms the input vector to the IDFT. Recall that the IDFT operates on

frequency-domain input vectors, and outputs time-domain vectors; the IDFT places the

parallel symbols in the appropriate frequency bins. The sub-channels’ orthogonality is

guaranteed by the fact that sinusoidal functions at Fourier harmonic frequencies are

inherently orthogonal†. The parallel time-domain symbols in the IDFT output vector are then

converted to serial for transmitting. Therefore, the transmitting OFDM symbol rate is the

same as that of each individual sub-channel.

A typical OFDM system usually takes the input data in the form of a raw bits stream, maps

them onto appropriate symbols based on the modulation (e.g. QPSK, QAM, …) of each subchannel, then groups them together into parallel sub-channels before using the IDFT to place

them into orthogonal frequency bins. To complete the picture, the serial OFDM symbols are

separated into real and imaginary, or I and Q, quadrature channels before being converted

into analog baseband using two Digtal-to-Analog Converters (DACs). The baseband signals

are then filtered by two reconstruction filters that satisfy the Nyquist condition. Finally, the

quadrature I and Q channels are mixed up to the carrier frequency using appropriate phase

before being amplified for transmission. Figure 3-2 summarizes the typical building blocks

of OFDM transmitter architecture.

Figure 3-2: OFDM Transmitter Architecture

†

Two functions f ( x ) and g ( x ) are orthogonal over the interval (a, b ) when

b

∫ f (x )g (x )dx = 0 .

The

a

orthogonality of two sinusoidal channels with off-set frequencies n∆ω and m∆ω can be proved as follows,

∫ cos(ω

0

+ n∆ω ) cos(ω0 + m∆ω )dω =

T

1

(cos[(n + m )∆ω ] + cos[(n − m )∆ω ])dω = 0

2 T∫

for

T=

2π

∆ω

40

3.2 OFDM Peak-to-Average Power Ratios

In order to find the peak-to-average power ratio of an OFDM system, the PAPR of each

individual channel is required. For a single channel, the PAPR is a function of modulation

type. Figure 3-3 shows the PAPR of a single channel of various levels of QAM.

Figure 3-3: PAPR of Single Channel with Various QAM Levels

For an OFDM system, each symbol from the parallel sub-channels are group together and put

through an IDFT function to achieve OFDM symbols.

An N-point IDFT function is defined as follows,

pn =

1

N

N

∑ am e

2πi ( n −1)( m −1)

N

(3-1)

m =1

Each output OFDM symbol is the vectorial sum of all the parallel sub-channel symbols with

appropriate phase rotation. A peak OFDM amplitude results when all input symbols have

41

maximum amplitude in their respective sub-channel modulation, and perfectly line up in the

summation. In this worse case scenario, the amplitude of the OFDM symbol is N times the

amplitude of the individual sub-channel symbol, with N being the number of parallel subchannels. Therefore, an OFDM system can potentially increase the peak-to-average power

ratio by a factor of N , or 10 log10 ( N ) in dB. A plot of additional PAPR caused by using

multi-channels OFDM is shown in Figure 3-4. For example, an OFDM system of 128 subchannels causes an additional 21dB of PAPR. If each of the 128 sub-channels has

modulation of 256-QAM, then the total PAPR of the system is 25.787dB (21dB plus

4.787dB from Figure 3-3).

Figure 3-4: Additional PAPR Caused by OFDM

However, the above number is the worse case situation. The probability of all the subchannels having peak-amplitude symbols at the same time, and all perfectly lining up is very

slim. For example, the probability of the peak amplitude happens in an OFDM system with

128 sub-channels of 256-QAM is 64 −128 . In order to accommodate this extreme PAPR, the

transmitter has to handle an unreasonably large dynamic range while suffering severe

efficiency penalty for large power amplifier back-off.

For an optimal transmitter performance, a more realistic PAPR number that accounts for

amplitude probability distribution is needed. A custom C-language script is written to find

the amplitude distribution of an OFDM system with multi-channels of QAM. The script

mimics the architecture in Figure 3-2 to construct OFDM symbols. A random generator is

used to generate the input bits stream, which is then mapped onto appropriate QAM symbols

(with 8 bits per symbol for 256-QAM, and 6 bits per symbol for 64-QAM). The QAM

symbols are then put into groups of M-parallel sub-channels. Next, OFDM is applied to the

sub-channels using the M-Point IDFT function. Finally, amplitudes of the output OFDM

42

symbols are then recorded to the appropriate level of the 1024 levels that evenly divide the

OFDM amplitude dynamic range. The script is used to find the amplitude distribution for

four OFDM systems: 128 sub-channels of 256-QAM, 128 sub-channels of 64-QAM, 128

sub-channels of 64-QAM, and 64 sub-channels of 64-QAM. For each system, a set of 2 31 or

more than 2 billion OFDM symbols is used to guarantee reliable distributions. The result

amplitude distributions are plotted in Figure 3-5.

Figure 3-5: Amplitude Probability Distribution (128 Sub-Channels OFDM of 256-QAM)

Several observations can be made from the distribution plots.

•

•

The OFDM amplitudes follow the literature prediction of a Raleigh distribution.

Peak-to-average power ratios for the four systems are:

o PAPR128-channels/256-QAM=14.87dB

o PAPR128-channels/64-QAM=14.37dB

o PAPR64-channels/256-QAM=11.86dB

o PAPR64-channels/64-QAM=11.36dB

43

•

•

•

•

•

Again, it should be emphasized that the above PAPRs are deduced from the set of 2 31

symbols, and are much lower than the worse possible case. However, as mentioned

earlier, the probability of the worse case is extremely rare that could be safely ignored

without affecting the system accuracy. This effect of ignoring the large amplitude

symbols, or clipping, is quantified in terms of bit-error rate in the next section.

As expected, higher number of OFDM sub-channels corresponds to higher PAPR.

For systems with the same number of sub-channels but different QAM levels, there is

little difference in PAPR. That means the total PAPR is dominated by the number of

sub-channels rather than the modulation type of individual sub-channels.

These more realistic PAPRs are much more manageable than the worse case from the

earlier example.

All the distributions have rather long tails at the high amplitude range where the

probabilities are very small.

Since the distribution plot has a rather long tail at the high amplitude range where the

probabilities are very small, the PAPR can be further reduced using clipping. Clipping refers

to the fact that the maximum amplitude can be set at a pre-determined level, where any

symbols with exceeding amplitude are limited or “clipped” to this maximum level.

Obviously, clipping causes errors in transmission. However, clipping can be set such that its

corresponding errors are within a tolerable BER in exchange for a reduction of PAPR.

With the custom C-script, the BER-PAPR trade-off dues to clipping can be easily

determined. The total OFDM symbols used to find the distribution for each system is 2 31 .

Given a tolerable BER , the number of OFDM symbols can be clipped is simply 2 31 ⋅ BER .

Next, OFDM symbols can be discarded starting from the right most amplitude bin of 1024,

and keeping on going until the total of discarded symbols reaches 2 31 ⋅ BER . That is the

maximum level where the amplitude can be clipped. Using this new maximum level, the

new PAPR can be recalculated. Figure 3-6 plots the PAPR versus BER caused by clipping

for the four example OFDM systems. There is little difference between the four systems.

From the results in Figure 3-6, it can be concluded that for a tolerable a BER of 10-5, an

OFDM system with 128 sub-channels of 256-QAM can be clipped to limit its PAPR to less

than 11dB. This represents a tremendous improvement from the worse case number of more

than 25dB that would undoubtedly reduce the power amplifier efficiency from any

acceptable level.

Additional elaborate coding schemes with various levels of complexity can be used to further

reduce the PAPR [29,30].

44

Figure 3-6: BER vs. PAPR for Various Clipping Degrees

45

46

Chapter 4

Outphase Amplifying – System Analysis

The capability of the outphase amplifying concept in modern communication systems

depends on three main parameters: the implementation of the amplitude-to-phase conversion,

the sensitivity of bit-error rate on mismatch among the two outphase paths, and the

implementation of an accurate and low loss power combiner. Traditionally, implementing the

inverse cosine and other trigonometric functions, necessary to carry out the amplitude-tophase conversion, using analog circuits are non trivial and inevitably complex. That is the

main reason for the lack of popularity for the outphase amplifying concept since its invention

in 1935. Instead, this chapter introduces a digital implementation to obtain the required

accuracy and efficiency. In addition, an optimal outphase assignment is proposed to control

the outphase amplitude variations and significantly lower the required power amplifiers’ gain

that can be traded for higher efficiency. Based on the proposed digital conversion, the

relationship between bit error rate and mismatch can be analyzed to establish a figure of

merit in determining the suitability of the outphase concept in modern communication

systems.

4.1 Digital Outphase Conversion

Figure 4-1: Outphase Concept with Digital Amplitude-to-Phase Conversion

47

Figure 4-1 shows the principle diagram for an outphase amplifier with a digital amplitude-tophase conversion, taking advantages of the available computational capability of

contemporary digital technology. Here, the amplitude-to-phase conversion is done in the

digital domain, on the complex series x[n] representing the quadrature time sample instances

of the input signal. The outputs of the conversion box are two series x1 [n] , and x2 [n] that

correspond to the two constant amplitude, phase modulated signals s1 (t ) and s 2 (t ) after the

DACs and Up-Converters. Each of the two constant amplitude outphase signals is then

amplified using two highly efficient class-E switching power amplifiers. The outputs y1 (t )

and y 2 (t ) of the PAs are then combined to restore the original amplitude modulated signal.

In the digital domain, the amplitude-phase conversion box takes the original amplitude

modulated series x[n] as the input, and produces the two outphase series x1 [n] , and x2 [n] .

Figure 4-2 demonstrates the digital outphase conversion using three example constellations:

x[1] , x[2] , and x[3] . Each constellation x[k ] of the original series is represented as a sum of

two outphase constellations, x+φ [k ] and x−φ [k ] , such that all the outphase constellations line

up along the constant amplitude circle. The angle between the two outphase constellations

depends on the amplitude of the original constellation. A constellation with small amplitude

(e.g. x[2] ) corresponds to a large angle between the two outphases ( ∠x+φ [2]x−φ [2] ), while the

constellation with large amplitude (e.g. x[3] ) corresponds to a much smaller outphase angle

( ∠x+φ [3]x−φ [3] ). The outphase constellations are then assigned to the two outphase channels,

represented by the two series x1 [n] , and x2 [n] , with the first channel contains all the x+φ [k ] ,

while the second contains all the x−φ [k ] as shown at the bottom of the conversion box in

Figure 4-2.

The formal mathematical definition of the digital outphase conversion is as follows,

• Input: x[k ] = x[k ] exp( jθ [k ])

• Outphase conversion function: x[k ] = x+φ [k ] + x−φ [k ]

x[k ]

Amax

exp( j (θ [k ] + φ [k ])) φ [k ] = cos −1

x+φ [k ] =

2

Amax

x [k ] = Amax exp( j (θ [k ] − φ [k ]))

Amax = max x[n]

−φ

2

• Outputs: x1 [k ] = x+φ [k ] , and x2 [k ] = x−φ [k ]

48

Figure 4-2: Digital Outphase Conversion

4.2 Amplitude Variation Control

Although each of the outphase series x1 [n] , and x2 [n] contains only constant amplitude

constellations, their corresponding analog signals s1 (t ) and s 2 (t ) do not have constant

envelope amplitude. In Figure 4-3, the solid traces, connecting the outphase constellations