Anode LCT 2000 Design Abstract

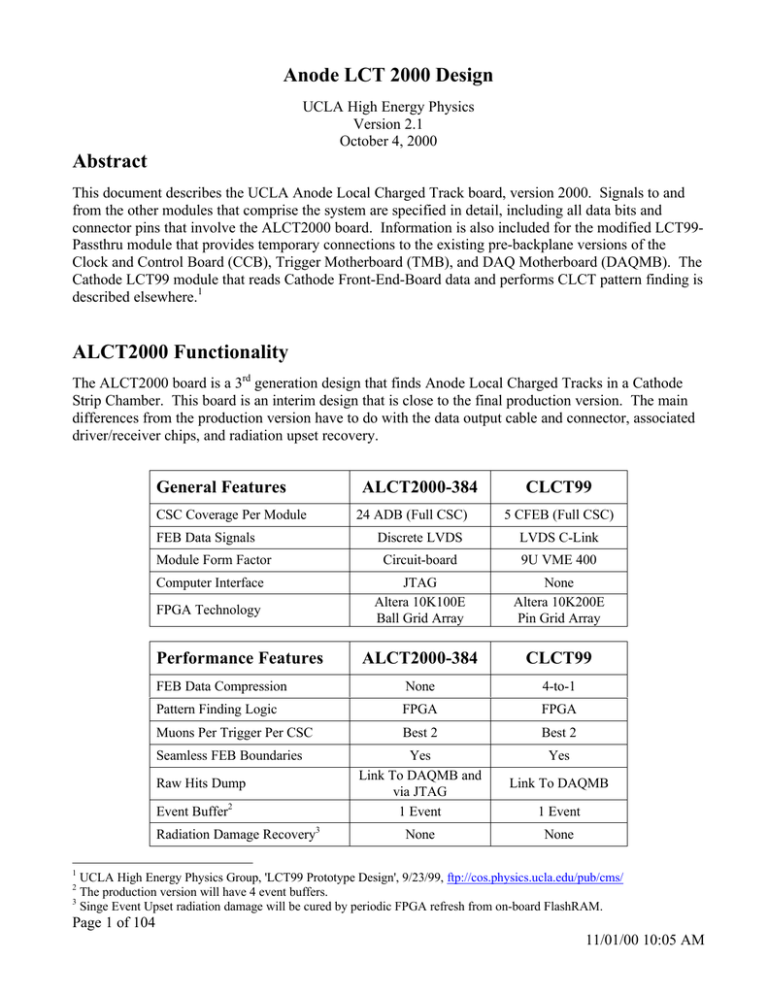

advertisement