Testing the ALCT board DRAFT 02/27/02

advertisement

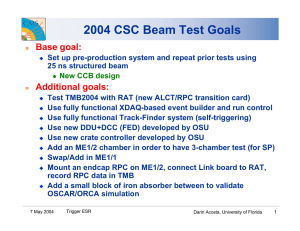

Testing the ALCT board DRAFT 02/27/02 Martin von der Mey Gennady Zhmakin Victor Barashko Jay Hauser For testing the ALCT board two test procedures are used. The first one tests the digital part of the board involving all the connections from the Virtex chip on the mezzanine board down to the AFEB input connectors. The second procedure tests the analog part of the chip involving the slow control functions of the Spartan XL chip. Digital Test I The following procedure tests following components of the ALCT board at 40 MHz: -The input connectors receiving signals from the AFEBs. -The delay chips involving adjustable delay settings -Bus exchanger (trace to Virtex chip) -Mezzanine connections between mezzanine board and ALCT board. -Input/Output connections of Virtex chip on the mezzanine board. It uses the output SCSI connector (J10) that usually rends signals to the TMB to send data from the AFEB input connectors. Usually these input connectors get data from the chamber through the AFEBs. Test procedure: In this test, the data gets injected from the Virtex chip to the SCSI connector J5. Over the cable connected between SCSI connector and the AFEB input connector the data passes through the delays and bus exchanger chips and gets back as input to the Virtex chip. The Digital test I checks the 32 data input signals of the AFEBs input connectors coming from the AFEBs. Since an ALCT-384 board has 24 AFEB input connector and they have to be tested serially it takes approximately 1 hour to test a whole ALCT board. After connecting the 32-bit output SCSI connector with one of the 24 40-pin input connectors as the figure above shows 4 test procedures can be selected: -Running 0. All 16-bits are set high expect for one that is set low. -Running 1. All 16-bits are set low except for one that is set high. -Shift 5. Each 4-bits are set to (0101). -Shift A. Each 4-bits are set to (1010). They can be selected using different dual pin connectors on the board. On the ALCT they are called TH1 and TH2. The two pictures below show TH1 and TH2 on the ALCT board. The second picture shows besides the dual pin connector the LEDs used for debug purposes. For the ALCT-384 24-input connectors are used. They get the input signals coming from the AFEBs. In the testing procedure they are grouped into pairs (12 pairs) and each pair has a left and a right connector. For selecting the pair of connectors to test the dual pin connector TH2 is used. The four pin pairs (TP1_00 to TP1_07) select which pair is selected. Each of the four pin pairs represents one bit in a 4-bit byte. The value of this byte represents the connector pair selected. The counting of the connector pairs starts at 0. If connector pair 0 needs to be selected, then none of the four pins (TP1_00 to TP1_07) should be connected. If for example, the four pin pairs are connected in the configuration 0010=2, where 1 means that the corresponding pins are shunted, the second connector pair has been selected. Selecting 0101=5 means that connector pair 5 has been selected and is going to be tested. Ones the pair is selected then the left or right connector of the pair using the dual pin connector TH1 can be selected. Therefore pins TP0_30 and GND are used. If no shunt is used the right connector is selected. If the two pins are connected the left connector is selected. The following picture shows how to select the left connector. After selecting the connector now the test procedure can be selected. If all the 16 bits need to be set to 1 for debugging of the hardware the pins TP1_07 and TP1_06 from connector TH2 have to be connected. This selection is very useful to test shortcuts between the different 16 bit signal pairs all the way down from the Virtex chip to the corresponding connector. If all the 16 bit pairs need to be set to 0 the pins TP1_06 to TP1_15 from connector TH2 need to be disconnected. This procedure is used to check for connections to power. If any of the wires used by the 16 bits pairs were connected to power, the output would stay high. The next two selections are used for checking if 2 outputs are shorted out. Therefore, following pattern 0101 0101 0101 0101 can be set connecting TP1_08 and TP1_09. If two neighboring LEDs would light up, it would show a shortage in the output. With this procedure only every second bit gets tested. For testing the remaining ones following pattern 1010 1010 1010 1010 needs to be selected connecting the pins TP1_06 to TP1_07 and TP1_08 to TP1_09. The next two procedures imply the usual running 0 and running 1 test. In order to select a running 0 test the pins TP1_10 and TP1_11 need to be connected as following picture shows: After selecting this mode all the LEDs will light up except one. In order to select now the running 1 test the pins TP1_06 and TP1_07 need to be connected and TP1_10 and TP1_11. In this case only one LED will light up corresponding to the bit just set to high. After going through this entire test procedures there is also the possibility to select certain bits inside the 16-bit pattern. In order to select this mode the pins TP1_14 and TP1_15 have to be connected. Then using the pins TP1_06 to TP1_13 the bit to set high can be selected. If for example, bit 4 is supposed to be tested (4=0100) following setting of TH2 is necessary: Important: Every time a new procedure of the described ones is selected it is necessary to reset the system connecting shortly the pins TP1_28 and TP1_29 in connector TH2. In order to monitor the tests using the LEDs the pins TP1_20 and TP1_21 in connector TH2 have to stay connected. This enables a slow running of the LEDs. If it is necessary to pause the running of a test it can be done connecting pins TP1_26 and TP1_27. Shunting this pins will pause the test, disconnecting them again will resume the test. Test of the Slow Control functions The following test uses the ALCT test board and a JTAG connection to the computer. The JTAG connection to the computer is necessary for sending function to the slow control chip like setting threshold, setting standby, etc. The first test consists in setting the threshold. In order to check these functions the Virtex chip is programmed to generate a 1 MHz test signal send down to the output connectors. Since the test board is connected to these connectors it gets the signal and send it out to test point J5Z middle on the test board. The appearance of the square pulse can then be checked using an oscilloscope. It should be a perfect square pulse with a frequency of 1 MHz and amplitude of 1 V. After verifying this, the threshold can be change from minimum (setting=0) to maximum (setting=255) using the program running on the computer. The result to the pulse is a change in the baseline position. During this periodically makes the square pulse jump up and down. In all this cases it is to check that the square maintains its form and frequency. This procedure has to be accomplished for all 24 channels in the ALCT-384 board for at least three setting of the thresholds for each channel. The same square pulse is send to the 6-lemo connectors on the ALCT board. By connecting the oscilloscope to each of them and checking the good shape of the square pulse the good or bad connectivity gets tested. The next function to test is the standby function. Using the program on the computer now the standby instruction can be sending to the diverse output connectors. The LEDs on the ALCT board monitor the functions. The LEDs in the right column show the channel to which standby has been send. The LEDs on the left column show the channel selected. The LEDs used for these purposes are D15-D23 and D17-D25 correspondingly, where D23 and D25 are the lowest bits. If a mismatch is found between the LEDs on the left column and the ones on the right columns it means that the standby signal is not working properly for the corresponding channel. The only connections that cannot be tested this way are the high voltage. One chip that cannot be tested this way yet is the delay chip. Therefore, it is tested manually. In future a routine will be added to the firmware to do the testing automatically. Digital Test II In the following test we want to test the remaining digital connections between the ALCT board and the SCSI connector. Especially the remaining signals in the J4 SCSI connector. Therefore we disconnect the JTAG cable and similar to the test in Digital Part I we load a new firmware into the Virtex chip and use the LEDs to monitor the test. The selection of the programs using the dual pin connectors TH1 and TH2 are the same as in Digital Part I. The LEDs show again the signals tested. The only signals that cannot be tested this way are the Reset signal and the Select Chain signal. The picture below shows the dual pin connector J6z on the test board. Since there are only 16 LEDs to display the signals tested and there are more than 40 signals to test a switch on the board is used to select which signal group is being displayed. The following table summarizes which signals are included in each signal group and which LEDs are displaying which signal. It summarizes the connections between the LEDs and the signals tested. Important: Inputs Jtag_s0, Jtag_s1, and output hard_rst (ALCT j4 ) are inaccessible for test. from: Test board control: p 47,48 (ALCT j5 ) System clock : p 7,8 ( test board J6z) name: f_kqlty1 CLK40 to: test board p22,21(ALCT j5) name: S/B clock The mapping between LED_X and the names of the LEDs on the board is as following: LED_0: D28 LED_1: D26 LED_2: D24 LED_3: D23 LED_4: D21 LED_5: D19 LED_6: D16 LED_7: D15 LED_8: D14 LED_9: D13 LED_10: D17 LED_11: D18 LED_12: D20 LED_13: D22 LED_14: D25 LED_15: D27 LED_16: D29 LEDs D10 and D11 are used to display which of the two signal groups is selected and displayed by the LEDs while the test is running. Then the column also contains the information at which pin of which connector for each LED is leaving the ALCT board and is getting back to the ALCT board. Due to this feature, each signal in reality tests two connections inside the ALCT board. So every time a LED flashes it is displaying two signals. Green LED (D10): Important: Pins 16 and 17 of test board dual pin connector J6z should be shunted. LED_0: LED_1: LED_2: LED_3: LED_4: LED_5: LED_6: LED_7: LED_8: LED_9: LED_10: LED_11: LED_12: LED_13: LED_14: LED_15: from: p 1,2 p 3,4 p 5,6 p 7,8 p 8,10 p 11,12 p 29,30 p15,16 p17,18 p19,20 p 45,46 p 21,22 p 23,24 p 25,26 p 27,28 p 29,30 (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j4) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) name: f_valid f_qlty0 f_key0 f_key2 f_key4 f_key6 tdo daq_d0 daq_d2 daq_d4 f_key1 daq_d6 seq_sts0 ddu_specl seq_sts1 lct_specl to: p 35,36 p 37,38 p 39,40 p 41,42 p 43,44 p 45,46 p 29,30 p 49,50 p 1,2 p 3,4 p33,34 p 7,8 p 9,10 p 11,12 p 13,14 p 15,16 name: (ALCT j4) rsrvd_in0 (ALCT j4) seq_cmd0 (ALCT j4) ext_injct (ALCT j4) brcst_str1 (ALCT j4) ccb_brcst2 (ALCT j4) ccb_brcst2 (ALCT j4) rsrvd_in1 (ALCT j4) tms (ALCT j4) tdi (ALCT j4) j_tck (ALCT j4) async_adb (ALCT j4) ccb_brcst1 (ALCT j4) ccb_brcst3 (ALCT j4) dout_str (ALCT j4) I1 accpt (ALCT j4) seq_cmd1 Red LED (D12): Important: Pins 9 and 10 of test board dual pin connector J6z should be shunted LED_0: LED_1: LED_2: LED_3: LED_4: LED_5: LED_6: LED_7: LED_8: LED_9: LED_10: LED_11: LED_12: LED_13: LED_14: LED_15: from: p 33,34 p 35,36 p 37,38 p 39,40 p 41,42 p 43,44 p 29,30 p45,45 p23,24 p25,26 p27,28 p 49,50 counter counter counter counter (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j5) (ALCT j4) (ALCT j5) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j5) name: daq_d2 daq_d1 bxn2 bxn0 f_key5 f_key3 tdo f_key1 rsrvd_out0 actv_feb_fg rsrvd_out1 f_amy to: p 35,36 p 37,38 p 39,40 p 41,42 p 43,44 p 45,46 p 29,30 p 49,50 p 1,2 p 3,4 p33,34 p 7,8 (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) (ALCT j4) name: rsrvd_in0 seq_cmd0 ext_injct brcst_str1 ccb_brcst2 ccb_brcst2 rsrvd_in1 tms tdi j_tck async_adb ccb_brcst1 Testing Software This software is dedicated to perform a set of testing procedures for the ALCT boards. Using this software it is possible to do operator-level tests of general functionality and more detailed designer-level tests for hardware troubleshooting. The software is able to operate under Microsoft Windows and Linux X-Window environments. The package is organized as a set of pages with special functions. The results of these functions are displayed into a Log Window. Setup Page Communication: For communication with the ALCT board using the JTAG connection it is necessary to open a JTAG connection using one of the installed drivers. Note: Under Windows only the “LPT Driver” is available. Under Linux both drivers are available. The JTAG driver under Linux is used for compatibility with other packages used. Select X-Blaster Channel: Using a drop-down list the JTAG channel (chain for X-Blaster JTAG adapter) can be selected. Four channels are available which represent 2 chains for programming (loading the firmware) the FPGA and EPROM chips for slow control and fast logic operations and 2 chains to interact with slow control and fast logic. Note: The majority of operations performed by the software automatically switch to the required JTAG channels. Manual switching of chains could be required when using manual JTAG communication, scripting automation and for operations through JTAG XBlaster outside of the testing software itself (Ex.: Downloading firmware using Xilinx Foundation software under Windows). ID Codes: To read all ID Codes from Chips in chains. Could be used to check: JTAG communication with ALCT board and with particular JTAG chain ALCT Operation mode (programming or controlling). Mezzanine Board Type: Trying to detect installed mezzanine board type (actually Virtex chip type) Programming operations of the mezzanine board cannot be performed if board type is unknown. Manual JTAG Commands: Allows working with JTAG chains by sending low-level JTAG commands using IR (Instruction Register) and DR (Data Register). Could be used for simple debugging. Firmware For operations with the firmware: The software allows: Read ID Codes from EPROM and FPGA chips on the ALCT board and mezzanine card. Blank Check of EPROM chips Erase EPROM firmware from Chips Load firmware to EPROMs using MCS Hex files Load firmware directly to FPGAs using BIT files Before any firmware related operations make sure that the ALCT board is in the programming state meaning that frequency should be turned off. The Loading procedure for both Slow Control and Virtex operation chains is the same For downloading firmware into EPROMs: Read ID Codes to make sure that programming chain is accessible (Optionally) Erase EPROM (Optionally) Blank Check EPROM to make sure that EPROM is erased and blank Load EPROM (choose MCS file for downloading from File Open dialog) (Optionally) Blank Check EPROM to make sure that EPROM is loaded For downloading firmware directly into FPGAs: Read ID Codes to make sure that programming chain is accessible Load FPGA (choose BIT file for downloading from File Open dialog) After that turn ALCT frequency is on. Slow Control How to test the slow control functionality? The slow control firmware should be loaded The software allows to: Check User ID Code inside Slow Control chip Set and read all thresholds (single and all thresholds) Set Test Pulse Amplitude Set and read Test Pulse Wire Group Mask Set and read Test Pulse Strip Layer Mask Set and read Standby Register Set and read Test Pulse Power Read Power Supply Voltages Read Power Supply Currents Read onboard Temperature Perform a slow control Self Test The program has a separate self-test window, which displays the status of execution. Delay Chips The program provides functionality for testing the delay chips. Again the special firmware should be loaded for testing purposes. The delay values are sent to JTAG in 120 bit data chunk, which represent 16-step (4bit) value of delay chip and 16 bit pattern for 6 delay chips – one delay chips group. 6chips X (4bit delay + 16bit pattern) = 120 bit. The loading of the delay groups occurs in parallel mode. And it is possible to load all delay chips by sending one 120 data chunk (enabling all delay groups). Delay Groups: Set Delay Groups mask. Marked groups will be loaded. Delay Value and Pattern: Define delay values and patterns for each delay chip in-group Set: Send delay chips values to ALCT Read Patterns: Read back patterns from all delay chips Check Patterns: Compare patterns that were sent to ALCT with patterns that were read back from ALCT and show results. Test Sets: Provide standard set of test, which allow locating data path problems on ALCT board. Script Engine Allows write simple tests without modifying of software. ALCT Slow Control Tests Slow Control General Testing Procedure 1. Power Off 2. Set Frequency to Off 3. Power On 4. Set Slow Control Programming Chain 5. Read Slow Control Chain Chip ID Codes 6. Upload Slow Control Firmware into EPROM 7. Set Frequency On 8. Set Slow Control Controlling Chain 9. Read Slow Control Chip User ID Code 10. Cycle Power 11. Do Functional Self Test Procedure (2 or more Passes) 12. Turn Power Off 13. Set Frequency Off 14. Turn Power On 15. Set Slow Control Programming Chain 16. Read ID Codes 17. Erase EPROM 18. Blank Check EPROM 19. Set Frequency to On 20. Read ID Codes 21. Cycle Power 22. Read ID Codes 23. Repeat Steps 1-11 (Optionally Direct Firmware Uploading to FPGA) 24. Repeat Steps 13-24 25. Repeat Steps 1-5 26. Upload Slow Control Firmware directly into FPGA 27. Set Frequency On 28. Set Slow Control Controlling Chain 29. Do Self Test Procedure (2 or more Passes) 30. Repeat Steps 1-10 to restore operational state 31. Power Off Slow Control Self Test Procedure 1. Read Slow Control Chip User ID Code 2. Cyclically (from 0 to 250 with 50 step) Set DAC values and Read Back Thresholds for all channels 3. Set and Read Back Standby Register 4. Set and Read Back Test Pulse Power Up Register 5. Set and Read Back Test Pulse Power Down Register 6. Set and Read Back Test Pulse Group Mask Register 7. Set and Read Back Test Pulse Strip Mask Register 8. Read Back Voltages for 4 channels of Power Supply 9. Read Back Currents for 4 Channels of Power Supply 10. Read Back On Board Temperature (Optionally) 11. Set Test Pulse Power Amplitude Values and Check it manually