Instrumentation for quantum computers

by

Wei-Han Huang

Submitted to the Department of Electrical Engineering and Computer

Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

December 2003

@ Massachusetts Institute of Technology 2003. All rights reserved.

Author.

..

Department o'

... ........ .... ........ ............

ctrical Engineering and Computer Science

December 12, 2003

....... ..................

Certified by.

Isaac L. Chuang

Associate Professor

Thesis Supervisor

Accepted by .............

Chairman, Department Committee on Graduate Theses

MASSACHUSETTS INSTiTUTE

OF TECHNOLOGY

APR 1BARKER

LIBRARIES

Instrumentation for quantum computers

by

Wei-Han Huang

Submitted to the Department of Electrical Engineering and Computer Science

on December 12, 2003, in partial fulfillment of the

requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

Abstract

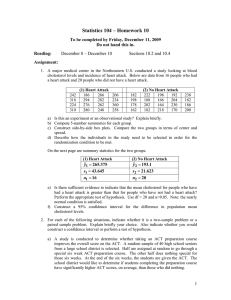

Quantum computation poses challenging engineering and basic physics issues for the

control of nanoscale systems. In particular, experimental realizations of up to sevenqubit NMR quantum computers have acutely illustrated how quantum circuits require

extremely precise control instrumentation for pulsed excitation.

In this thesis, we develop two general-purpose, low-cost pulse programmers and

two Class E power amplifiers, designed for precise control of qubits and complex pulse

excitation. The first-generation pulse programmer has timing resolutions of 235 ns,

while the second-generation one has resolutions of 10 ns. The Class E power amplifier

has ps transient response times, a high quality-factor, and a small form factor.

The verification of the pulse programmer and the Class E power amplifier is

demonstrated using a customized nuclear quadrupole resonance (NQR) spectrometer, which incorporates both devices. The two devices control the generation of RF

pulses used in NQR experiments on paradichlorobenzene (C 6 H 4C1 2 ) and sodium ni35

trite (NaNO 2 ). The NQR signals originating from 14 N in sodium nitrite and from C1

in paradichlorobenzene are measured using the NQR spectrometer. The pulse programmer and the Class E power amplifier represent first steps towards development

of practical NMR quantum computers.

Thesis Supervisor: Isaac L. Chuang

Title: Associate Professor

3

4

Acknowledgments

During my senior year in undergraduate studies, I was introduced to a fascinating

subject - Quantum computation.

It involved all the subjects I loved - computer

science, electrical engineering, and quantum physics. Since coming to MIT, I had the

opportunity to continue my interest and learn more about the science. The past two

years has been an amazing learning experience, both in life and academics.

My advisor, Isaac Chuang has been a great inspiration. His wealth of knowledge

in the field has helped guide the work conducted in this thesis, and he has taught me

how to motivate my work and put it into perspective. His actions has set an example

for me on how to conduct myself as a scientist.

I would like to thank my lab mates in the Quanta group for being both a wonderful

source of support and friendship. I would like to thank Jeff Brock for being a great

friend both in and out of the lab. I wish Jeff and Amy's beautiful, baby girl LucyClare good health and a long, happy life. One of the nicest friends I have known is

Murali Kota - thanks for the many interesting late night dinner conversations and

Sunday lunches about physics. The old man of our group, Matthias Steffen, has been

a wonderful source for guidance. His advice on oral and writing presentations has been

extremely helpful. Terri Yu's suggestion on taking 8.321 was a great idea. The class

gave me better intuition about quantum physics. My UROP student Zilong Chen has

been a great help. He is a superposition of both theorist and experimentalist. What

can I say about Andrew Houck? His silly antics have always been a source for laughs.

Josh Folk, Andy's boss, is an incredible experimentalist as well as a BBQ chef. Many

thanks also to Aram, Francois, Andrew Cross, and Joshusa Powell for being great

group members and amazing theorists.

Working at NIST over the summer of 2003, I found John Martinis to be a great

source of knowledge about electronics and Josephson junctions. I greatly appreciate

his hospitality as well as his family's. John's excitement and energy shines through

day after day. To the NIST crew, Ray Simmons, Robert McDermott, and Dave

Pappas - thanks for the interesting conversation both about science, politics, and ape

5

behavior. Steve Waltman is truly a master of analog electronics, especially microwave

electonics.

electronics.

Every conversation I have had with him, I have learned

something new. Special thanks to Rebecca Tarantino for putting up with me over

the summer and being the best roommate that I have ever had.

To my closest friends from undergraduate:

thank you Willy, Phil, Cindy, and

Raymond for coming up and visiting, time to time, and keeping me grounded.

Finally, I would like to thank my family for their support and guidance. To mom,

dad, SueBee, Linda, Amy, Will, AK, Dave, Kay, Mike, and the two newest members

of our family Momo (Emily) and Giddy (Allison).

6

Contents

1

2

19

Introduction

1.1

Historical background . . .

19

1.2

Purpose of my work . . . .

21

1.2.1

Pulse programmer

22

1.2.2

Class E amplifier

23

1.2.3

Nuclear quadrupole resonance spectrometer

23

1.3

Organization of thesis . . .

24

1.4

Contributions

. . . . . . .

25

1.5

Literature

. . . . . . . . .

26

Background: Theory of Quantum Computation

29

2.1

Axioms of quantum mechanics . . . . . . .

29

2.2

Quantum bits ...................

32

2.3

Multiple qubits . . . . . . . . . . . . . . .

33

2.4

Computation using quantum systems . . .

34

2.4.1

Entanglement . . . . . . . . . . . .

34

2.4.2

Quantum parallelism and quantum measurement

35

2.5

2.6

. . . . . . . .

36

2.5.1

Unitary evolution . . . . . . . . . .

36

2.5.2

Single-qubit gates . . . . . . . . ..

37

2.5.3

Two-qubit gates . . . . . . . . . ..

40

. . . . . . . . . . .

42

Quantum gates and circuits

Quantum algorithms

2.6.1

Shor's algorithm

44

. .

7

2.7

3

Sum m ary

46

Nuclear Magnetic Resonance Quantum Computing

49

3.1

NMR historical background .....

.......................

50

3.2

NMR quantum computing ......

........................

51

3.3

3.2.1

NMR quantum computer: the physical system .........

51

3.2.2

RF pulses perform quantum operations . . . . . . . . . . . . .

53

NM R spectrom eter

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

55

Transmitter: pulse programmer and power amplifier . . . . . .

57

NM R experiments . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

59

3.4.1

Experimental realization of Shor's algorithm . . . . . . . . . .

59

3.4.2

The experiment and the importance of the pulse programmer

60

3.3.1

3.4

3.5

3.6

4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instrumentation issue for quantum computers

. . . . . . . . . . . . .

63

3.5.1

NMR readout: measurement . . . . . . . . . . . . . . . . . . .

63

3.5.2

Transient data acquisition

. . . . . . . . . . . . . . . . . . . .

64

3.5.3

Recovery tim e . . . . . . . . . . . . . . . . . . . . . . . . . . .

65

Sum mary

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Class E Amplifier

4.1

66

67

History of the Class E amplifier . . . . . . . . .

. . . . .

67

4.1.1

Motivation: a solution to increasing SNR

. . . . .

70

4.2

Operation and design . . . . . . . . . . . . . . .

. . . . .

70

4.3

Design equations

. . . . . . . . . . . . . . . . .

. . . . .

73

4.4

Class E amplifier characteristics . . . . . . . . .

. . . . .

75

4.4.1

. . . . . . . . .

. . . . .

78

. . . . . . . . . . . . . . . . . . . . .

. . . . .

79

4.5

Measurement difficulties

Sum m ary

5 Pulse Programmer

5.1

81

Problem and approach . . . . . . . . . . . . . . . . . . . . . . . . . .

81

5.1.1

Introduction to the pulse programmer . . . . . . . . . . . . . .

82

5.1.2

A case study: the Varian pulse programmer

83

8

. . . . . . . . . .

5.2

Designing an NMR quantum computer pulse programmer . .

88

5.3

First-generation pulse programmer

. . . . . . . . . . . . . .

88

5.3.1

Architecture of first-generation pulse

program m er . . . . . . . . . . . . . . . . . . . . . . .

5.3.2

Hardware implementation of first-generation pulse

program mer . . . . . . . . . . . . . . . . . . . . . . .

5.3.3

5.4

program mer . . . . . . . . . . . . . . . . . . . . . . .

95

. . . . . . . . . . . . .

97

Architecture of second-generation pulse

program m er . . . . . . . . . . . . . . . . . . . . . . .

5.4.2

5.5

98

Software implementation of second-generation pulse

program m er . . . . . . . . . . . . . . . . . . . . . . .

5.4.4

97

Hardware implementation of second-generation pulse

program m er . . . . . . . . . . . . . . . . . . . . . . .

5.4.3

93

Performance evaluation of first-generation pulse

Second-generation pulse programmer

5.4.1

90

Software implementation of first-generation pulse

program mer . . . . . . . . . . . . . . . . . . . . . . .

5.3.4

88

99

Performance evaluation of second-generation pulse

program m er . . . . . . . . . . . . . . . . . . . . . . .

110

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

112

Sum m ary

113

6 NQR Testbed

6.1

NQR spectrometer ........

. . . . . . . . . . . 114

6.2

Impedance matching probe . . .

. . . . . . . . . . . 115

6.2.1

LC resonator as a probe

6.2.2

Probe design

. . . . . . . . . . . 116

. . . . . .

. . . . . . . . . . . 119

. . . . . . . .

. . . . . . . . . . . 123

6.3

Pin diode switch

6.4

Receiver . . . . . . . . . . . . .

. . . . . . . . . . .

127

6.4.1

Homodyne receiver . . .

. . . . . . . . . . .

127

6.4.2

Heterodyne receiver . . .

. . . . . . . . . . .

128

9

7

6.5

Experiment

6.6

Summary

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

129

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

132

Conclusions

7.1

135

Future Prospects: pulse programmer

. . . . . . . . . . . . . . . . .

A NQR Theory

136

139

A.1

NQR historical background ...........

. . . . . . . . . . . . .

139

A.2

Qualitative comparisons of NMR and NQR . . . . . . . . . . . . . .

140

A.3

NQR Hamiltonian and resonance frequencies . . . . . . . . . . . . .

141

A.4 Pure NQR selection rules ..............

. . . . . . . . . . . . .

143

A.5 RF excitation and effective signal averaging

. . . . . . . . . . . . .

146

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

148

A.6

Summary

B Appendix A: First Generation Code

B.1 Source code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

151

157

C VHDL Pulse Programmer

173

D Probes

199

E Class E amplifier

205

10

List of Figures

2-1

(a) Bloch sphere representation of the state 1,0) of a single qubit. (b)

The position in the Bloch sphere of five important states. The states

are not norm alized. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-2

33

Quantum circuit representation of (a) an arbitrary single-qubit rotation

U, and (b) the

NOT

gate. . . . . . . . . . . . . . . . . . . . . . . . . .

operation, and (b) the

operation. 40

2-3

Truth tables for (a) the

2-4

Quantum circuit representation of (a) a controlled-NOT gate, (b) a

CNOT 12

CNOT 2 1

40

zero-controlled-NOT, (c) a SWAP gate, and (d) a controlled-U gate.

The * symbol denotes the control qubit - the controlled operation is

only executed if the qubit is in the 1) state. The o symbol denotes the

zero-controlled qubit, i.e., the operation is only executed if the control

qubit is in the state 10).

2-5

. . . . . . . . . . . . . . . . . . . . . . . . .

Quantum circuit representation of a

TOFFOLI

gate and its decomposi-

tion into two-qubit gates. . . . . . . . . . . . . . . . . . . . . . . . . .

2-6

41

42

The quantum circuit which performs the order-finding algorithm in

Shor's algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

46

3-1

Overview schematic of an NMR spectrometer [FR86]

56

3-2

Picture of an Oxford Instruments 500MHz narrow-bore NMR magnet

3-3

The NMR cabinet houses the transmitter and control electronics for

the Varian spectrometer.

3-4

. . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . .

57

58

Quantum circuit illustrating the order-finding algorithm in Shor's al-

gorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11

60

3-5

The molecule hexafluoro butadiene is used as the NMR quantum computer in Shor's algorithm . . . . . . . . . . . . . . . . . . . . . . . . .

3-6

61

NMR pulse sequence for implementing Shor's algorithm to factor N=15

with seven qubits. The tall lines represent 90' pulses acting on one of

the seven qubits (horizontal lines) about the positive i (no cross),

negative , (lower cross) and positive

4-1

(top cross) axis.

. . . . . . .

A schematic of a Class E amplifier is shown. The resonant load network

circuit is used to tune the resonant frequency of the amplifier. ....

4-2

62

72

Example of ideal, transient waveforms for the input and output of the

Class E amplifier. When the gate is switched on, the voltage at the

drain VD decreases, while the voltage VOUT increases. When the gate

is switched off, VD rises and VOUT decreases. . . . . . . . . . . . . . .

72

4-3

The Class E amplifier schematic shown for amplifier tuned at 4.64 MHz. 75

4-4

Measurements of the voltages at the drain and the gate of the power

transistor are shown.

The drain voltage is about 3 times the gate

voltage, fitting closely with theoretical predictions . . . . . . . . . . .

4-5

77

The Class E amplifier shown for the amplifier constructed and tested.

The resonance frequency is 4.64MHz. . . . . . . . . . . . . . . . . . .

78

5-1

Structure of the Varian pulse programmer [VNMO1] . . . . . . . . . .

85

5-2

Block diagram of the first-generation pulse programmer.

90

5-3

The hardware uses a buffer to store the pulse sequence and access the

. . . . . . .

commands during execution. . . . . . . . . . . . . . . . . . . . . . . .

5-4

91

The Rabbit RCM2200 module used as the hardware for the firstgeneration pulse programmer.

. . . . . . . . . . . . . . . . . . . . . .

92

5-5

The daugther board customized for the Rabbit RCM2200 module. . .

92

5-6

The state machine for the rabbit pulse programmer. . . . . . . . . . .

95

5-7

Anatomy of a pulse sequence. Each operation has an associated overhead cost for processing a command. The larger the overhead time,

the higher the timing resolution. . . . . . . . . . . . . . . . . . . . . .

12

96

5-8

Structure of pulse programmer for the second-generation pulse program m er . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

98

.

100

5-10 Main framework for VHDL code . . . . . . . . . . . . . . . . . . . . .

101

5-9

Functional block diagram of Digilab 2E development board [Dig02]

5-11 The finite state machine for the pulse programmer entity. The initial state is the exit state. In this state, the pulse programmer loops

infinitely. When an enable signal is set, the state machine executes

command code fetched from the FIFO. . . . . . . . . . . . . . . . . .

104

5-12 UART data format. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

105

5-13 The finite state machine for the LED controller. The LED utilized is

on the Diligent Inc. D210 board.

. . . . . . . . . . . . . . . . . . . .

108

5-14 The main finite state machine shows the overall behavior of the pulse

program mer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

109

5-15 At 100MHz, the minimum pulse width was 10 ns, which matched with

the predicted value. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-1

110

A block diagram of an NQR spectrometer, illustrating the three main

components: the transmitter, probe, and receiver. The sample material

is placed in the coil.

6-2

. . . . . . . . . . . . . . . . . . . . . . . . . . .

115

LC matching network to the probe. When the capacitors are tuned

properly, impedance is matched to a 50Q coaxial line and power transfer is maxim ized.

6-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Schematic of the matching network circuit used for analytic solution.

Rwire is the resistance of the wire. In the analysis Rwzre = 3Q.

6-4

117

The tuning and matching capacitors of the matching network.

. ..

.

118

The

capacitors are enclosed in a metal RF box to shield the system from

extraneous noise.

6-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

119

A single coil used in the probe of the NQR spectrometer, where 1 is

the length of the coil. . . . . . . . . . . . . . . . . . . . . . . . . . . .

13

120

6-6

An example of a coil made using the described technique. The inductance of the coil is 9.7pH and the number of turns, N, is 32. . . . . .

6-7

121

The probe encapsulating the test tube and the coil. The sample material is placed in the test tube holder for NQR spectroscopy. . . . . .

122

6-8

The schematic of the pin diode switch. . . . . . . . . . . . . . . . . .

123

6-9

Design consideration: a notch filter forms when the PDS is shut off.

The resonance frequency of the notch filter must be considered in the

design of the system . . . . . . . . . . . . . . . . . . . . . . . . . . . .

124

6-10 The Bode plot of a poorly designed pin diode switch. The resonance

frequency is at 4.73MHz which is very close to the resonance frequency

of the matching network. Thus, small signals are attenuated by 1. . .

125

6-11 The transmission board containing: (1) RF mixers for producing gated

pulses, (2) a pin diode driver circuit, and (3) a pin diode switch. . . .

126

6-12 An example of a receiver chain is shown. A block diagram shown in

this figure corresponds to the real devices as seen on the right-hand side. 127

. . . . . . . . . . . . .

128

in paradichlorobenzene . . . . . .

130

. . . . . . . .

131

6-16 The data points from a nutation experiment on NaNO2 . . . . . . . .

132

6-13 A general schematic of a heterodyne receiver.

6-14 The FID signal produced from

3

1C1

6-15 The FID signal of NaNO 2 captured on an oscilloscope.

7-1

A block diagram of a pulse programmer designed for superconducting

Josephson-phase qubits.

A-1

. . . . . . . . . . . . . . . . . . . . . . . . .

137

A bessels function is the average FID signal induced in NQR experiments. A "7r/2" pulse is produced when wt is 0.667r. The amplitude is

normalized in this example.

. . . . . . . . . . . . . . . . . . . . . . .

148

B-1 Overview of the entire schematic for the first generation pulse programmer. The next 4 sections show full size schematic diagrams of the

daugther board. The sections start from left to right and move from

top to bottom .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14

152

B-2 The top left corner schematic of the rabbit daugther . . . . . . . . . .

153

B-3 The top right corner schematic of the rabbit daugther board . . . . .

154

B-4 The bottom left corner schematic of the rabbit daugther board . . . .

155

B-5 The bottom right corner schematic of the rabbit daugther board . . .

156

. . . . . . . . . . . . .

172

B-6 The PCB layout of the rabbit daugther board

D-1 A die-cast Al RF box is used as the container for the probe and tuning

and matching capacitors.

Large copper sheet metal is used as the

wiring between components. Sheet metal is used to lower parasitic

inductance. The probe holder is a piece of paper rolled into a cylinder.

The coil is wrapped around the paper. The resonance frequency is

4.649MHz, with C1 = 260pF, C2 = 760pF, and L1 = 1.2pH.

. . . . .

200

D-2 The second probe utilizes similar construction methods as the first.

The major difference is variable air capacitors are used as the tuning

and matching capacitors. Use of the variable air capacitors turns out

to be a poor design choice, because the air capacitors have a lot of

undesired capacitively coupling to other components. The resonance

frequency was not attainable.

. . . . . . . . . . . . . . . . . . . . . .

201

D-3 The third probe is the same design as the first, except the length of

the coil is increased to maximize the

Q. The

length of the coil is the

same as the diameter of the coil, 0.78 inches. The resonant frequency

is 4.649MHz with C1 = 26pF, C2 = 95pF, and L, = 9.6uH. . . . . . .

202

D-4 The last probe is shown here with a 9.7pH coil. The coil slides over a

0.78 inch test tube which fits in the center of the copper cylinder. The

tuning and matching capacitors are described in section 6.2.1.

. ..

.

203

D-5 The mechanical drawings (completed in the software Omax) for the

probe (in Figure D-4) is show with lengths in units of inches.

. . . .

204

E-1 Protel schematic of a Class E amplifier tuned at 4.638MHz. A IRF510S

power transistor is used in the design.

15

. . . . . . . . . . . . . . . . .

206

E-2

Protel PCB layout for the Class E amplifier. The board is made to fit

into a NIM box. Additional debugging pins and thru holes (vias) are

added to the board. The back-to-back pin diode switches are incorporated into the design of the PCB. . . . . . . . . . . . . . . . . . . . .

207

E-3 Simulations of the Class E amplifier are completed in Protel. Here, the

voltage at the gate of the transistor (volt-b) is plotted along with the

voltage at the drain (v-out) and the voltage across the resistor (output). 208

16

List of Tables

2.1

The solution to order-finding problem is explicitly calculate for L

=

15.

Theorderof isr=2 for x=4. . . . . . . . . . . . . . . . . . . . . .

45

4.1

Dependence of P, R, V.c, and V on Qload [Sok98]

74

4.2

Parameters used for the design of a CEA. The resonance frequency is

tuned to 4.64M Hz.

4.3

. . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

75

Class E measurements: the measured and simulated values of the amplifier are shown in the table. The percent error is also displayed.

. .

78

5.1

Characteristics for evaluating the Varian pulse programmer . . . . . .

86

5.2

Characteristics for the Varian pulse programmer.

87

5.3

The performance of several lab-built pulse sequencers for various ap-

. . . . . . . . . . .

plications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4

87

The list of operational codes available to the RCM2200 pulse sequencer.

Currently port C is the only available output channel.

. . . . . . . .

93

. . . . . . . . . . .

96

5.5

Characteristics for the Rabbit pulse programmer.

5.6

Pulse sequence byte code and operational code for the pulse programmer. 102

5.7

Control code for the pulse programmer . . . . . . . . . . . . . . . . .

5.8

Characteristics for the second-generation pulse programmer. This table shows the parameters for clock speeds of 100MHz and 150MHz.

6.1

102

. 111

The calculated values used for NQR spectrometer matching network.

The resonance frequency of the circuit is 4.64MHz.

17

. . . . . . . . . .

119

18

Chapter 1

Introduction

"I'm not happy with all the analyses that go with just classical theory, because Nature

isn't classical, dammit, and if you want to make a simulation of Nature, you'd better

make it quantum mechanical, and by golly it's a wonderful problem!"

Quote from Richard Feynman [Fey8l]

1.1

Historical background

In 1947, research by Shockley, Bardeen and Brattain at Bell Labs led to the fortuitous discovery of the first solid state transistor [BB48].

The advent of transistors

ushered in a new era in modern computing. Soon after, integrated circuits were introduced. At that time, integrated circuits (ICs) yielded lower cost, higher reliability,

and simpler circuit designs than conventional electronics; consequently, the computing industry expanded rapidly. The burst in the field of digital computing led Moore

to propose that the number of transistors that could fit onto a square inch of silicon would double every 12 months [Moo65]. His prediction, known as Moore's Law,

has held surprisingly true for the past 30 years. But as the number of transistors in

microprocessors continued to increase, the sizes of transistors decreased in order to

maintain reasonable power efficiency and low costs. The shrinking sizes raised concern

among researchers. As technology continued to abide by Moore's Law, the sizes of

individual elements made their behavior increasingly affected by the laws of quantum

19

mechanics. Foreseeing this trend, researchers began to ponder the fundamental and

physical limits of computation.

In 1981, Feynman discussed the problem of simulating physics with computers

[Fey82].

He asked whether a universal, classical computer could simulate physics

exactly and efficiently. Then, he made a crucial insight. Instead of using classical

computers, he proposed using nature to simulate physics. Another words, rather than

a classical Turing machine, use a machine based on the laws of quantum mechanics

to perform simulations. He produced an abstract model illustrating how a quantum

system could be used to do computations.

As a result, research into the idea of

computational devices based on quantum mechanics quickly emerged.

Physicists and computer scientists explored the questions laid out by Feynman,

Deutsch, and Benioff [Fey82, Deu85, Ben82]. In 1985, Deutsch realized that Feynman's insight could lead to a general-purpose computer.

He extended the theory

of quantum computation with the development of the universal quantum computer

and the quantum Turing machine [Deu85]. The feasibility of a general-purpose quantum computer led scientists to investigate quantum algorithms. In 1992, Deutsch

and Jozsa discovered the Deutsch-Jozsa algorithm [DJ92], which suggested quantum

computers might be capable of efficiently solving mathematically hard problems.

Then Shor's discovery propelled quantum computing into the limelight. In 1994,

he showed that the problem of factoring the product of two prime numbers could

be solved efficiently using a quantum computer [Sho94]. Shor's algorithm not only

generated academic interest, but it also garnered the attention of the public because

of its potential to break encryption schemes, thereby disrupting electronic commerce.

Shor's algorithm enables one to decipher encryption codes based on the difficulty

of prime factorization. The Rivest-Shamir-Adleman (RSA) algorithm is an example

of a popular, public-key crypto-system used for electronic commerce, which can be

deciphered using Shor's algorithm.

Since the conception of Shor's algorithm, researchers have investigated suitable,

physical systems for quantum computers such as Josephson junction superconducting circuits, ion traps, silicon-based semiconductors, and quantum dots [MNAUO2,

20

Kan98, KMWO2, GAPA99] but these physical systems are still in their infancy. Even

so, one technology, nuclear magnetic resonance (NMR), has made moderate advances.

Through radio-frequency (RF) waves, one can manipulate a quantum system that

is physically represented by an ensemble of molecules in a liquid solution. NMR

quantum computing is the forerunner in demonstrating the tools and language necessary for quantum computation. Numerous experiments have been performed, which

demonstrate the Deutsch-Jozsa algorithm, Grover's algorithm, and Shor's algorithm

[SvDH+03a].

1.2

Purpose of my work

NMR quantum computing experiments have demonstrated the validity of quantum algorithms and have demonstrated the complexity of implementation. Current solution

NMR techniques for quantum computation, applied at room temperature and using

standard magnetic fields for polarization, face experimental challenges that make it

unlikely such systems will scale to many quantum bit (qubit) sizes. Because of this,

the usefulness of solution NMR quantum computing has been called into question

[War97].

Nevertheless, for the development of quantum computers, the techniques and instrumentation of NMR provide a powerful language and tool set.

The language

developed helps describe and provide physical understanding for controlling quantum

computers. Underlying the physical control of the qubit is the NMR spectrometer

and its RF electronics.

Modern NMR achieves exquisite control, typically apply-

ing several hundred RF pulses using sophisticated electronics such as digital pulse

programmers, RF amplifiers, phase shifters, mixers, and low-noise amplifiers. The

instrumentation is extremely large and expensive, requiring careful maintenance by

technicians. Although conventional NMR spectrometers are the cutting-edge tool for

quantum computing, they are not optimized for that purpose.

By designing electronics specifically for NMR quantum computing applications,

we can sidestep some problems associated with current systems. NMR quantum com21

puters require complex pulse programmers and power amplifiers to finely control the

generation of RF pulses and pulsed excitation. In our research, we investigate and

provide low-cost, compact pulse programmers and power amplifiers, which meet the

needs for NMR quantum computing. We study two electronic components: the pulse

programmer and the Class E amplifier (CEA) [Sok75]. We discuss the pulse programmer and the CEA in Sections 1.2.1 and 1.2.2 and the targeted design parameters for

each device. In Section 1.2.3, we test the pulse programmer and Class E amplifier by

incorporating both devices in a nuclear quadrupole resonance (NQR) spectrometer

and performing basic NQR experiments.

1.2.1

Pulse programmer

In an NMR quantum computer, a pulse programmer controls the duration, amplitude

and phase of RF waves applied to a qubit. A series of RF pulses, known as a pulse

sequence is generated by the programmer, and quantum logical operations can be

accomplished.

Pulse sequences are transmitted via RF electronics, known as RF

channels. Generally, there exists one RF channel to control one qubit.

NMR quantum computers demand complex, high-speed pulse programmers to

control the qubits.

There are several requirements for NMR quantum computing

applications, including scalability and high timing resolution.

As the number of

qubits increases, the number of RF channels increases. The pulse programmer needs

to control more RF channels, making scalability an important design issue. Another

design issue is the timing resolution of the pulse programmer. For example, suppose

a pulse programmer has a pulse resolution of 50 ns; then it can typically output pulse

durations in multiples of 50 ns. Interestingly, a timing resolution of 50 ns is available

in some commercial NMR spectrometers. High resolution pulses are used to perform

relaxation experiments with special pulse sequences such as the spin echo [Fre97].

For quantum computers, higher resolutions can possibly reduce errors in quantum

operations [Ste03].

In this work, we develop two multiple-channel pulse programmers with accurate

timing resolutions. For the first pulse programmer, we concentrate on the develop-

22

ment of a transparent, user-friendly interface. High timing resolution becomes central

to the design of the second programmer. We attempt to design and implement a pulse

programmer with 10 ns timing resolution.

1.2.2

Class E amplifier

The control of qubits often requires accurate control of RF field strengths applied

on the qubit.

Often, power amplifiers are used in NMR systems to obtain such

control. For accurate control, the power amplifier used in NMR technology poses

several problems and issues, including ringdown time, efficiency, large size, and high

production costs. We address the deficiencies of a typical power amplifier by replacing

it with a CEA topology [Sok75].

The CEA is a switching mode power amplifier that has high power efficiency, high

quality factor (Q), fast ringdown times, and a priori designability. Because of its fast

ringdown time, the signal-to-noise ratio in NMR measurements may be increased. In

this work, the goal was to improve the ringdown time of the power amplifier.

1.2.3

Nuclear quadrupole resonance spectrometer

To test the pulse programmer and the Class E amplifier, we built an NQR spectrometer, demonstrating both devices performing pure NQR spectroscopy experiments.

Pure NQR is very similar to NMR, requiring a similar spectrometer design with minor changes. In pure NQR spectroscopy, researchers exploit the nuclear quadrupole

moment and electric field gradient surrounding the nucleus with pulse sequences of

RF fields to detect a small signal, known as a free induction decay (FID) signal. To

produce pulse sequences, digital and analog electronics in NMR and NQR spectrometers are similar, both requiring a pulse programmer and a power amplifier. The main

difference between NMR and NQR spectrometers is the absence of a large, superconducting magnet in NQR systems. Since no magnet is required, an NQR spectrometer

is cheaper and faster to design and construct than an NMR spectrometer.

23

1.3

Organization of thesis

We start with two introductory chapters describing the basic requirements for NMR

quantum computing: quantum computation theory and NMR theory. In the next

two chapters, we motivate the need to build electronics for NMR quantum computers,

specifically the CEA and the pulse programmer. Next, we present the designs for the

CEA and for the pulse programmer. In the final chapter, we discuss a customized

NQR spectrometer for the express purpose of testing the pulse programmer and CEA.

Chapter 2 starts by laying out the fundamental theory of quantum computation, providing the language and background necessary to understand NMR quantum computation and the progress made in the field. We start with the basic axioms

of quantum mechanics, and illustrate how computation is accomplished based on the

fundamental unit of quantum information: the quantum bit or qubit. Building on this

foundation, we illustrate how the properties of entanglement and unitary evolution

can be used to compute quantum logical operations and how these operations can be

reduced to quantum circuits, which can be used to describe quantum algorithms. We

end by describing Shor's algorithm using quantum circuits.

Next, we delve into the world of NMR quantum computing in Chapter 3. A single

spin-1/2 nucleus is a suitable physical system to represent a qubit. We first describe

how a single qubit can be controlled by RF pulse sequences and how to apply quantum

computation on multiple qubits via the J-coupling among nuclei. We describe the

experimental progress on NMR quantum computing, highlighting Shor's algorithm

in Section 3.4. The NMR implementation of Shor's algorithm demonstrates the requirements for the pulse programmer and the power amplifier in an NMR quantum

computer. By defining the requirements for the pulse programmer and power amplifier, we can design low-cost control instrumentation for NMR quantum computers.

In Chapter 4, we introduce the CEA and present the design and implementation

of a CEA tuned for NQR spectroscopy. The circuit operation and topology is described in detail, emphasizing the trade-offs between high

Q and

power efficiency. As

an example, the design of an amplifier tuned at the resonance frequency of 4.64MHz

24

is illustrated. Finally, we discuss several electrical characteristics of a CEA, including:(1) the output power, (2) efficiency, (3)

Q and

Chapter 5 describes the pulse programmer.

(4) ringing time.

First, we describe the functionali-

ties of a pulse programmer citing an example of one from Varian, Inc. [VNMO1].

Next, we describe two generations of pulse programmers. The first-generation one is

implemented with a Rabbit RCM2200 programmable chip with a customized daughterboard, which I designed.

The second-generation programmer utilizes field pro-

grammable logic arrays (FPGA) to generate pulse sequences.

The framework of

the code is presented for the second generation pulse programmer. For each pulse

programmer, we characterize the behavior by evaluating parameters such as timing

resolution, memory size, minimum and maximum pulse delay, and number of RF

channels.

In order to validate the CEA and the pulse programmer, we develop an NQR

spectrometer as a testbed. In Chapter 6, we describe an implementation of an NQR

spectrometer and demonstrate the CEA and pulse programmer working in this system. We outline the hardware design, starting off by discussing the three main components of the spectrometer: (1) the transmitter, (2) the probe, and (3) the receiver.

The design of each component is discussed by describing the RF methodology for the

basic circuit elements, such as the mixer, the LC resonator, the inductor, and the

amplifier. Some preliminary results are obtained from the hardware, showing basic

signal response from sodium nitride (NaNO 2 ).

The last chapter, Chapter 7, summarizes the work in this thesis and recommends

future work. It addresses the extension of the pulse programmer to superconducting

Josephson phase qubits.

1.4

Contributions

In Chapter 4, the CEA is an extension of the work done by graduate student Yael

Maguire, who designed a 34MHz CEA for NQR spectroscopy of paradichlorobenzene.

Based on his initial designs, I redesigned a CEA tuned at 4.64MHz.

25

I laid out a

printed circuit board (PCB) and verified the functionality in Protel. Zilong Chen

and I "stuffed" the boards and characterized the behavior of the device.

The framework for the pulse programmer described in Chapter 5 was designed with

guidance from Professor Chuang. I created an initial version of the pulse programmer

using a low-cost, programmable logic device using the programming language C.

For the second generation pulse programmer, I wrote the code in very high-speed

integrated circuits (VHSIC) hardware description language (VHDL), and tested and

debugged the system.

The NQR spectrometer described in Chapter 6 was a collaborative effort including

me, Zilong Chen, and Professor Chuang. I laid out the transmission board, including

the pin diode switch, in Protel. Several versions of the matching network and probe

were created before a final circuit was completed. Measurement code was written in

Matlab. Prof. Chuang provided code for Fourier transform and GPIB data acquisition. Zilong Chen and I constructed nuclear instrumentation module (NIM) bins for

the spectrometer based on designs I produced in Omax. I built several versions of

the NQR spectrometer, slowly refining the electronics behind the spectrometer. The

goal is to continuously refine and advance the electronics in the system and integrate

much of the system into several PCBs. I also designed a well-shielded probe. UROP

student Jeff Brock assisted me in procuring the materials necessary for the completion

of the probe.

1.5

Literature

The following is a compilation of texts that are particularly useful to this thesis:

Quantum information theory

Nielson and Chuang's Quantum Computation and Quantum Information is a comprehensive introduction to quantum information theory [NCOO]. It covers a wide range

of topics, from quantum algorithms to error correction, and highlights the numerous

open problems in the field. Another useful book is Gruska's Quantum Computing

[GruOO]. This text merges the ideas in the fields of quantum information Theory and

26

Computer Science, making the book accessible to beginners. John Preskill's lecture

notes for Physics 219/Computer Science 219 course presents delightful discussions

describing quantum computing in an intuitive fashion [Pre98].

Nuclear magnetic resonance

Ernst, Bodenhausen, and Wokaun's Principlesof Nuclear Magnetic Resonance in One

and Two Dimensions is a wonderful and comprehensive resource for the treatment

of NMR, both classically and quantum mechanically [EBW87]. A great companion

to the book is Ray Freeman's Spin Choreography [Fre97], which gives an intuitive

overview of high-resolution NMR techniques and spin dynamics.

Spectrometer instrumentation

Experiment Pulse NMR: a Nuts and Bolts Approach is a great book for experimentalists. Fukushima and Roeder discuss NMR spectroscopy from a practical viewpoint

and various approaches for constructing a spectrometer [FR86].

Petersen's thesis

entitled Pulsed Nuclear Quadrupole Resonance Instrumentation and Study of N14

Spectrum and Relaxation in Sodium Nitrite is an invaluable resource [Pet75], providing tips and techniques that proved to be indispensable to the work covered in this

thesis.

27

28

Chapter 2

Background: Theory of Quantum

Computation

We review the fundamental principles in the theory of quantum computation, illustrating how quantum mechanical operations can be reduced to unitary, logic operations. Section 2.1 discusses the axioms of quantum mechanics. Building on these

concepts, we describe how quantum systems are abstractly represented in Sections 2.3

and 2.4 and introduce the necessary ingredients for performing quantum computations, including the phenomena of entanglement and quantum parallelism, which give

certain quantum algorithms their speed-up over their classical counterparts. Based

upon these properties, we show how quantum operations reduce to quantum gates

and circuits, as discussed in Section 2.5. Using quantum gates, we discuss the following algorithms in Section 2.6: the Deutsch-Jozsa algorithm, Grover's algorithm, and

Shor's algorithm.

2.1

Axioms of quantum mechanics

Quantum theory is a mathematical model of the microscopic, physical world.

To

characterize the model, we need to specify how it will represent states, observables,

measurements, and dynamics in a closed system. We present the basic axioms of

quantum mechanics, which are based on discussions in Preskill's lecture notes

29

[Pre98].

1. States: A state is a complete description of a physical system. In quantum

mechanics, a state is a vector in a Hilbert space over the complex numbers C. Vectors

are denoted in Dirac's notation as ket 1,0). The complex conjugate and transpose of

state IV)) is known as bra (41.

norm 11|0)11 2 = (4{4), where

The state is defined to be complete, such that, the

(..f..) denotes the inner product. The inner product of

1') and 1#), (V510), maps an ordered pair of vectors to a scalar in the set C and is

defined by the following properties:

* Positivity: (0140) > 0 for

4') # 0;

" Linearity: (#| (aI11) + b 102)) = a (#q11) + b (#412); and

* Skew symmetry: (01)

= ($0)* .

2. Observables: An observable is a property of a physical system that can be

measured in principle. In quantum mechanics, an observable is a self-adjoint operator,

i.e., A = At, where A is a linear operator. An operator is a linear map taking vectors

to vectors,

(2.1)

A: 14)->AI).

A self-adjoint operator in Hilbert space has a spectral representation. Another

words, the eigenstates form a complete orthonormal basis. We can express a selfadjoint operation A as

A

(2.2)

anPn,

=

n

where an is an eigenvalue of A and P, is the projector onto the eigenspace of A with

eigenvalue an. For example, if an is nondegenerate, then Pn

=

In )1(, where In) is

the eigenvector with eigenvalue an.

3. Measurement: The measurement process of a quantum system has numerous

interpretations, but the most common version is called the Copenhagen interpretation.

In quantum mechanics, the numerical outcome of a measurement of the observable

A is an eigenvalue of A, an. Measurement of a quantum state IV)) is described by the

30

measurement operator P, which gives the output a, with probability

P(an) = |IPnjV)f1 2 = (OjPnkb).

(2.3)

The measurement operator must satisfy the completeness relation

(2.4)

= I.

EP

n

If the outcome is an, then the normalized quantum state after measurement becomes

Pn|b)

1

((OlPn n)

10)) 1/2-+ .(2.5)

If the measurement is immediately repeated, then according to this rule, the same

outcome is attained again, with probability one. The state of the quantum system

collapses to a post-measurement state. Collapse of the quantum state implies that

the information contained in the coefficients of the eigenstates is instantaneously and

irreversibly destroyed.

Post-measurements cannot reveal information on the other

states.

4. Dynamics or Evolution: Under a closed system, the time-evolution of a

quantum state is described by unitary operators, where an unitary operation U has

the property UtU = I. In the Schr6dinger picture of dynamics, the vector describing

the system moves in time as governed by the Schr6dinger equation

hd

i. dth 1(t)) = HMO(t)),

where H is the Hamiltonian and h is Planck's constant.

(2.6)

Note that in subsequent

equations h is set to 1. For the time-independent Schr6dinger equation, the solution

is

14(t)) = exp (-i7=Lt)I (t = 0))).

31

(2.7)

We denote the time-evolution operator as U(t), where

U(t) = exp (-i'Ht)

(2.8)

|V(t)) = U(t)14'(t = 0)).

(2.9)

and

This completes the four axioms of quantum mechanics. Next, we explore the fundamental unit that makes quantum computation possible: the quantum bit.

2.2

Quantum bits

The indivisible unit of classical information is the bit, which takes on one of two possible values: logical 0, or logical 1. The corresponding unit of quantum information

is known as the "quantum bit" or qubit. In contrast to classical bits, a qubit can

exist in a superposition of states 0 or 1, otherwise denoted by the quantum states:

10) and 11).

The most general normalized state for a single qubit can be expressed

mathematically as

14)

(2.10)

= alO) + b1l),

where a and b are complex numbers that satisfy Ia12 + b12

=

1. The overall phase of

the qubit is physically irrelevant and cannot be revealed by any measurement. We

can also write |0) as

4') = cos

()

10) + exp (iq) sin

(0)

1).

(2.11)

The state of a qubit can be visualized as a vector in a sphere, called the Bloch

sphere, as shown in Figure 2-1. In this representation, the qubit has two degrees of

freedom, 6 and

#.

If the state of the qubit is along the i-axis, then 1') = 10) or 11).

When the vector lies along the 2

-

Q plane,

11).

32

the qubit is in a superposition of

10) and

10>

10>

IV>

10>-i>

-----------IV>

lo+ 1>

) +il1)

Figure 2-1: (a) Bloch sphere representation of the state 1') of a single qubit. (b) The

position in the Bloch sphere of five important states. The states are not normalized.

2.3

Multiple qubits

If we have two or more qubits, then the picture of the Bloch sphere does not hold

true. The state of two qubits, each in an arbitrary superposition

11) = a10) + bill)

and 1b2 ) = a 2 10) + b2 11), is written as

10)

=

101) 0102)

(2.12)

1')

=

aia 2 |00) + a 1 b2 101) + bia 2 10) + bib 2 |11).

(2.13)

where 0 is the tensor product or Kronecker product symbol. The coefficients of the

terms in the joint superposition state of the two qubits can be viewed independently

of each other. Thus, a more general statement is

1#) = cool00)

where ICool

2

+

coil 2 + cio|

2

+

+ cio10O) + ci11),

+ coi0)

(2.14)

Icnl 2 = 1. For n qubits, a general quantum state 1)

can be described as:

2n-1

I)

cili),

=

(2.15)

i=o

where i is the decimal representation, and ci satisfies the normalization condition

2

n-

1

Icil2

The Hilbert space in an n-qubit system has 2" dimensions, and the state of the

33

quantum system

4')

can be in a superposition of 2" states. Notice that the number

of degrees of freedom for an n-qubit system grows exponentially.

2.4

Computation using quantum systems

Now, we examine the quantum mechanical properties that makes quantum computations possible, such as entanglement, quantum parallelism, and unitary evolutions.

2.4.1

Entanglement

An n-qubit system can be expressed as

4')

(2.16)

=

where |0j) is the quantum state of the i-th qubit and D represents the tensor product

of n states. For example, Equation 2.13 is in the form of Equation 2.16. If the state

of a quantum system can be expressed in the form of Equation 2.16, then the state

is deemed separable.

One of the properties that makes quantum mechanics unique is that there exists

states (in the physical realm) where it is impossible to express a separable state in

such a form. We call such a state non-separable or entangled because the qubits are

correlated. Entanglement is a very important concept in quantum information theory

because it is believed to be a necessary resource to speed up certain algorithms. An

important entangled state is the two-qubit Bell states (also known as EPR pairs):

|3oo)

=

100),+i)

(2.17)

1001)

=

101),+10)

(2.18)

,00)-l)

and

)

111i)|#11)==

101) - 110) .

34

(2.19)

(2.20)

2.20

Note that the measurement of a qubit in the Bell state reveals the state of the second

qubit. This correlation is what Einstein called "spooky action at a distance."

2.4.2

Quantum parallelism and quantum measurement

Suppose we apply a classical reversible gate, g(x), where IV) = cob0)

+ ciii). By

linearity, applying g(x) on the superposition yields:

colo) + ciii)

'-4

colg(0)) + c1|g(1)).

(2.21)

Interestingly, application of the gate g(x) results in the parallel computation of both

states 10) and 11). We begin to see how quantum computation may yield exponential

speed-up for certain algorithms. Consider a two-qubit system in the state

+ cio10)

1') = coo 00) + coi01)

+ cii1l).

(2.22)

The execution of g(x) results in the output state

14)

= coo g(00)) + coilg(Ol)) + ciolg(10)) + c11 Ig(11)),

(2.23)

so that four values have been evaluated in parallel. In general, for every additional

qubit, the number of parallel evaluations doubles. A function that is applied on n

qubits results in the evaluation of 2" possible states:

2"-1

2"-1

1:1X) F- E

x=O

Ig W)

(2.24)

x=O

where x is the integer encoded by a string of n bits.

As the number of qubits grows linearly, the number of evaluations grows exponentially. Thus, a quantum computer can simultaneously perform a number of parallel

operations.

This property was first introduced by David Deutsch in 1995, and was termed

quantum parallelism [Deu85]. As a consequence of quantum parallelism, quantum

35

computers that utilize superposition appeared to have exponentially more power than

classical computers. However, as mentioned in Section 2.1, the measurement process

collapses the superposition of quantum state into a single eigenstate. Measurement

has great implications in the context of quantum parallelism.

Suppose, there exists a 2-qubit system. When a measurement of a superposition

state occurs, the result probabilistically returns either g(OO), g(01), g(10), or g(11). If

n qubits are in a superposition of 2n states, only one of the 2n states will be the result

after the measurement. It appears that the exponential power of quantum computers

is not accessible. However, quantum measurement is not necessarily detrimental to

quantum computation. Despite the necessity of measurement, algorithms exist that

utilize entanglement and quantum parallelism to speed up classical computations.

2.5

Quantum gates and circuits

The mathematics describing quantum computing can be abstracted to a quantum

circuit language, analogous to Boolean, logic gates in electrical engineering.

We

present a description of unitary operations at an intermediate level of abstraction

based on quantum gates analogous to classical gates, such as, the NOT, AND, and

XOR gates. We describe:

" quantum gates that can be implemented on a quantum computer,

* quantum circuit notation for relevant quantum gates, and

* a universal set of implementable quantum gates.

2.5.1

Unitary evolution

Unitary evolution is used to describe the construction of quantum circuit.

One of

the axioms of quantum mechanics (Section 2.1) dictates the dynamics of a quantum

system, i.e., the time-evolution of a quantum state, are described by:

10(t)) = U(t)10(t = 0)),

36

(2.25)

where we denote the time-evolution operator as U(t) as:

U(t) = exp (-iZHt).

(2.26)

H is the Hamiltonian and h is set to 1. Using density operator p, the time-evolution

is given by:

p(t)

=

Epi

(2.27)

piU(t)I i(t = 0))(Oi (t = 0)Ut (t).

Oi(t))(4'i(t)I

The time-evolution of the quantum state can be visualized as rotations of a single

qubit in the Bloch sphere, as shown in Figure 2-1, while multiple qubits can be

visualized as rotations in Hilbert space. We can utilize time-evolution to perform

quantum logic computations.

2.5.2

Single-qubit gates

Unitary evolutions are generated by Hamiltonians, and by controlling these Hamiltonians, specific quantum computations are achieved. A single qubit

Rb)

is described

by col0) + c1 1), which can be expressed in matrix notation as:

(co

1') =

(2.28)

C1

where

14))

is a column vector of two entries, co and ci, and Ico12 + c

Here, 10)

1

=

0)

and 11)

0

=

12

. Note that the matrix representation of (01 is

a row vector; specifically, it is the complex conjugate and transpose of

4').

A single-qubit operation can be describe as a 2x2, unitary matrix acting on

4'initial:

4 )final =

U4)initial.

(2.29)

For example, consider the NOT operation. The NOT function takes 10) to 1) and 11)

37

to |0). The unitary matrix for a NOT operation corresponds to:

UNOT

By applying

UNOT

0

1

1

0

(2.30)

=-

on state IQinitial, we see that:

0

0fnal -

1

cO

Ci

0)

ci

CO

(2.31)

This operation switches the states 10) and 1). We have shown that a single qubit can

be visualized as a rotation in the Bloch sphere (Figure 2-1). More specifically, any

single-qubit rotation takes the form

U = exp (ia)Rj(0),

(2.32)

where R(O) also corresponds to a 0 rotation in the Bloch sphere about the r-axis.

We can define Rf1(6) in the following manner:

) =cos (-)cr

2CO

R (0) = exp (- i '2

where 0 = (o,, u-Y, o-)

i

sin

-

(nru + nYo- + nzo-),

20

(2.33)

-y , and oz denote the Pauli matrices:

and o-,

0

-

1

1 0

,

=-

(

1

0

0

( -iJ

,o-,

7

(2.34)

and a- denotes identity matrix: The Pauli matrices give rise to three useful classes

of unitary matrices, the rotation operators about the

Rx(0)

Ry(6)

exp

exp (-i

2

2

Gi-?

RZ(6)- exp (-i 2)

2

= cos

)

(-)

2()

20

o-r

-

38

y-,

i sin

c-i -isin

-

(2

-,

i

and i-axes:

-

c-2,

(2.36)

-

sin -

(2.35)

o-.

2 UZ

(2.37)

A rotation about the i-axis of 90' corresponds to an unitary matrix R,(90'), while

a rotation R,(180') is a NOT operation with an overall global phase factor.

Another interesting single-qubit gate is the HADAMARD gate, given as the matrix

1(1

H=

vl2

1N

1

.

(2.38)

-1)'

The HADAMARD gate transforms the basis state, 10) or 11), into equal an equal su-

perposition of states 10) and 11) with different phases:

)

(2.39)

10)- 1)

(2.40)

0)

I1)

*

This gate can be implemented by -- and

Q-rotations:

H = R'(1800 )R9(900 ) = Rv(90')Rs(180 0 ).

Single quantum operations are represented using circuit diagrams.

(2.41)

A unitary

operation, U, is shown in Figure 2-2(a). The NOT gate is represented by the symbol

D, as shown in Figure 2-2(b).

39

U

(b)

(a)

Figure 2-2: Quantum circuit representation of (a) an arbitrary single-qubit rotation

U, and (b) the NOT gate.

2.5.3

Two-qubit gates

The "classical" two-qubit gate is the controlled-NOT, or CNOT, gate. The CNOTij

gate has two qubit inputs, i and

j.

Qubit

j

is called the target, and qubit i is known

as the control qubit. If qubit i is in the state 11), then the target qubit is flipped;

otherwise the target qubit remains the same. The truth table is shown in Figure 2-3.

Input(ij)

00

01

10

11

Output (i)

00

01

11

10

Input(ij)

00

01

10

11

(a)

Output(ij)

00

1 1

10

0 1

(b)

Figure 2-3: Truth tables for (a) the CNOT 12 operation, and (b) the CNOT 21 operation.

For a two-qubit state 1) = coo100)+coi 01) +c 1o110) +cjI| 11), the unitary matrices

for the CNOT gates are:

0 1 0 0

1 0 0 0

0 1 0 0

UCNOT

12 =

and

UCNOT 2 1

1 0 0 0

=

0 0 0 1

0 0 1 0

0 0 1 0

0 0 0

(2.42)

1

An extension of the CNOT gate is the controlled-U gate, where a single-qubit operation

U is performed on the target qubit if and only if the control qubit is 1). There is also

40

the zero-controlled-U gate, in which U is executed if and only if the control qubit is

10).

Finally, another two-qubit operation is the SWAP gate:

1

0 0 0

Uswap =

(2.43)

,

0 1

0

0 0

0 0

1)

which switches the state of the two qubits. An alternate to express the SWAP operation

is by a series of CNOT operations:

SWAP

12

= CNOT 12 CNOT 21 CNOT

(2.44)

12 .

The quantum circuit representations of all two-qubit operations presented in this

section are shown in Figure 2-4.

U

(a)

(b)

(c)

(d)

Figure 2-4: Quantum circuit representation of (a) a controlled-NOT gate, (b) a zerocontrolled-NOT, (c) a SWAP gate, and (d) a controlled-U gate. The e symbol denotes

the control qubit - the controlled operation is only executed if the qubit is in the

11) state. The o symbol denotes the zero-controlled qubit, i.e., the operation is only

executed if the control qubit is in the state 10).

One can create multiple-qubit operations, i.e., three or more qubits, using onequbit and two-qubit gates. For example, the TOFFOLI gate, as shown in Figure 2-5,

is composed of CNOT gates and controlled-V, where:

v=

2

41

(2.45)

The TOFFOLI operation flips the target qubit (the third qubit) if and only if the

two control qubits are 11); hence, it is also referred to as a doubly-controlled NOT or

CCNOT

gate.

V'

V

V

Figure 2-5: Quantum circuit representation of a TOFFOLI gate and its decomposition

into two-qubit gates.

The quantum circuits in this section correspond to logical operations similar to

classical Boolean circuits. In classical computation, a small set of gates (e.g. AND,

OR, NOT) can be used to compute an arbitrary classical function. Such a set is uni-

versal for classical computation. Similarly, there exists a set of quantum gates that is

universal for quantum computation, i.e., any unitary operation may be approximated

to arbitrary accuracy by a set of quantum gates. For example, an arbitrary singlequbit gate and CNOT gate form a set of universal quantum gates. With a universal

set of quantum gates, quantum algorithms can be implemented.

2.6

Quantum algorithms

This section discusses examples of some milestone quantum algorithms developed in

the field of quantum information theory and illustrates Shor's algorithm using quantum circuits. We also describe the Deutsch-Jozsa algorithm and Grover's algorithm.

These three algorithms have been proven to be faster in computational steps than

their known classical counterparts, requiring less resources, such as quantum memory

(e.g. spin of an electron) or quantum channels (e.g. fiber optic line). We briefly give

an overview of the Deutsch-Jozsa algorithm and Grover's algorithm, followed by a

quantum circuit description of Shor's algorithm.

42

In 1992, Deutsch solved Deutsch's problem, showing an exponential speed-up of

the quantum solution over the classical one. Deutsch's problem is stated as follows:

Suppose Bob has a black box, or oracle, f(x) with n input bits and one output bit.

Alice selects an n-bit number ranging from 0 to 2" - 1. She sends the number to Bob,

and he calculates the number using the oracle. The output of the oracle is promisedto

be either constant for all possible input values or balanced, i.e., equal to 1 for exactly

half of all possible input values, and 0 for the other half. Alice's goal is to determine

with certainty whether Bob's oracle is constant or balanced.

Classically, Alice needs to send Bob 2/2+1 different inputs to determine whether

Bob's oracle is constant or balanced. Deutsch and Jozsa realized that a quantum computer can solve the problem exponentially faster than the classical approach. In the

quantum algorithm, the initial input to the oracle is the equal superposition of all

possible values from 0 to 2' - 1. During the computation the wrong answers destructively interfere while the correct answer interferes constructively. In this approach,

only one query of the oracle is needed, highlighting the potential advantage of a

quantum computer. Unfortunately, there are no practical applications known to take

advantage of Deutsch's algorithm. It is only a clear demonstration of how a quantum

computer can solve certain problems with an exponential speed-up over a classical

computer.

In contrast to the Deutsch-Jozsa algorithm, Grover's algorithm has practical applications. Grover showed that a quantum computer can search an unsorted database

with polynomial speed-up over the best possible classical, unstructured search algorithm. An example of an unstructured search is finding the name corresponding with

the phone number in a phone book with n alphabetically listed names. On average,

one would look up (n(n + 1)/2 - 1) /n ~ n/2 different numbers before finding the

name. With Grover's algorithm, one can find the name in V/n attempts.

As in the Deutsch-Jozsa algorithm, there is the notion of a promise problem in

Grover's algorithm. In this case, an oracle returns either f(x) = 0, for all values of x

except for the unique entry x = x 0 , or f(x) = 1, where x = xo. The input is put into

an equal superposition of all possible values, using the HADAMARD transformation,

43

and sent through a quantum circuit, which performs a number of Grover iterations

and eventually returns xO. Intuitively, Grover's iteration constructively builds up the

amplitude of Ixo) while reducing the amplitudes of the remaining terms. Note that the

amplitude of Ixo) peaks to a maximum value, and afterwards, the amplitude oscillates

sinusoidally. The measurement of the output will be xO with high probability.

Shor's algorithm

2.6.1

Shortly before Grover's algorithm was discovered, another algorithm had made a

large impact in the field of quantum computing. In 1997, Shor made a tremendous

discovery in the problem of factorization and the computation of discrete logarithms

[Sho97]. He showed an exponential speed-up over the best known classical algorithms

and provided a method to efficiently decipher public-key crypto-systems that rely on

the difficulty of factoring, such as the RSA encryption algorithm. The factorization

algorithm quickly became famous and was dubbed as Shor's algorithm. We describe

Shor's algorithm and highlight the major steps necessary for obtaining the solution,

including the order-finding problem.

We outline the solution to the factorization problem. Note that much discussion

about the mathematics behind this algorithm is left out of the discussion. The solution

to factorization is mainly due to results from number theory.

Suppose L is the product of two prime numbers. Shor's algorithm states:

" If L is even, then return the factor 2, else

" If L = ab for a > 1, b > 2, and a, b E Z, then the factors can be efficiently,

probabilistically determined, and the factors are returned.

" If L fits neither of the first two conditions, randomly choose x such that 1 <

x < (L - 1). If gcd(x, L)> 1, then return the factor gcd(x, L).

* If the first three conditions do not return a factor, then use the order finding

subroutine to find the order r of x Modulo L.

44

* If r is even and x 2

-1(mod L), then the factors of L are computed by the

ged(xl + 1,L) and and the gcd(x" - 1,L). Finally, test to see if these factors

are non-trivial. If so, return the factors; otherwise, the algorithm fails.

The key step to the exponential speed-up over classical algorithms is the quantum

order-finding algorithm, which determines the order, r, of x(mod L).

function is represented by the function

f(j)

=

Suppose a

xi (mod L). If L = 15 and x = 4, then

the order r is 2. We explicitly calculate the order for L = 15 in Table 2.6.1.

j f(j)

0

1

2

3

4

5

1

4

1

4

1

4

Table 2.1: The solution to order-finding problem is explicitly calculate for L = 15.

The order of is r = 2 for x = 4.

The quantum circuit for the order-finding algorithm is shown in Figure 2-6. The

unitary operation U performs the transformation

Li) 1k)

-+

j) |ximod

L). The size of

the first register is approximated as t = 2 log(L), and the second register is approximated as log(L). The operation, controlled-Us, is efficiently implemented using the

modular exponentiation procedure [NCOO]. The circuit operates as follows:

" Initialize the quantum state to 10) 1).

* Apply the HADAMARD operation to create a superposition of states on the first

register, changing the quantum state to

2-1)1).

-E

* Apply controlled-Uj operations to create

1 E~-I I)lxj(modL)) ~

1 ENt--1

r_ exp (27ris/r) 1j) Ius),

where s/r is an n-bit approximation of s/r and us) =

exp (-2isk xkmod L)

Note that if we wish to approximate s/r to an accuracy of n-bits with probability of success at least 1 - e, we choose t = n + [log (2 + 1/2c)]

45

* By applying the quantum Fourier transform to the first register, the quantum

state becomes L 1

I s/r)Iu,).

" Measurement of the first register yields s/r.

t

)ot

H t

lif

Figure 2-6: The quantum circuit which performs the order-finding algorithm in Shor's

algorithm.

The continued fractions algorithm is applied to the result of the quantum orderfinding circuit to reveal r [NCOO]. Finally, the factors of L are determined by calcu-

lating gcd(x' + 1,L) and gcd(xl - 1,L).

2.7

Summary

Based on the axioms of quantum mechanics, we have established methods to perform

quantum computations. Simple logical operations are accomplished on a single qubit,

which can be mapped to the Bloch sphere.

However, the Bloch sphere does not

apply for quantum operations on multiple qubits.

Operations on multiple qubits

can correspond to a parallel number of computations; quantum systems containing

n qubits can be represented by 2n complex variables.

This concept of quantum

parallelism can be used along with entanglement to possibly speed up certain quantum

algorithms, which can efficiently solve certain mathematically hard problems.

Quantum algorithms can be described by quantum circuits that correspond to

unitary evolutions. As quantum circuits increase in size, the complexity of the circuit

46

grows, raising the probability of failure in a quantum circuit; thus, implementing

complex RF pulse sequences is a challenging task, requiring precise control of the RF

pulse to accomplish a quantum logical operation.

In this chapter, we have focused on the ideal theoretical scenario. However, realistically generating precise pulsed excitation to control the qubit system requires

one to understand the physics of the system, representing the quantum computer,

and the requirements for control. In the next chapter, we describe nuclear magnetic

resonance (NMR) quantum computers and identify the methods and tools underlying

the control of qubits.

47

48

Chapter 3

Nuclear Magnetic Resonance

Quantum Computing

The language of quantum computation and quantum circuits can be translated to

a sequence of RF pulses, which are generated via analog and digital circuits, such

as the pulse programmer and the power amplifier, in a nuclear magnetic resonance

(NMR) spectrometer. We begin, in Section 3.1, by describing the history of NMR

spectroscopy. Then, Section 3.2 discusses how quantum circuits and operations are

accomplished using NMR techniques and RF pulses. Underlying pulsed NMR techniques, there is the NMR instrumentation, which consists of numerous components

including the magnet, probe, receiver, workstation, and receiver, as described in Section 3.3. Two major components are of interest: the power amplifier and the pulse

programmer.

Understanding the limitations of the NMR system for quantum computing helps

us identify the problems associated with it. The experimental demonstration of Shor's

algorithm shows the need for pulse programmers capable of executing complex, fast

RF pulse sequences and low-noise, power amplifiers.

In Sections 3.4 and 3.5, we

discuss the instrumentational issues with pulse programmers and power amplifiers

used for NMR quantum computers, highlighting the challenges of generating complex

pulses and decreasing ringdown time of power amplifier, which can increase the signalto-noise ratio (SNR) during readout.

49

3.1

NMR historical background

The purpose of spectroscopy is the characterization of a molecular system by a "spectrum." In most cases, the spectrum presents resonance properties of a physical system

and can thus provide insight into its quantum mechanical structure. One example

of a spectroscopy is nuclear magnetic resonance (NMR) spectroscopy. The first experiments and discoveries about NMR were executed by Bloch and Purcell in 1945

[BHP46, PTP46].

They discovered that it is possible to transfer energy from RF

waves to certain nuclei, whose resonance is defined by a uniform, strong magnetic

field applied along a fixed axis. Furthermore, they were able to excite the state of the

system, populating higher energy levels. When the system relaxed to its equilibrium

state, a small signal was induced, which was detected using using a coil.

Over the last two decades, NMR spectroscopy has gone through a renaissance.

The advancement of modern digital electronics have made it possible to apply novel

techniques in NMR such as Fourier analysis, which in turn, made high-resolution

NMR possible. The advancement in NMR spectroscopy has made it one of the most

powerful analytical tools in modern science with applications including solid state

physics, chemistry, molecular biology, and medicine. Interestingly, NMR spectroscopy

also has connections to quantum computation.

In 1997, Gershenfeld and Chuang [GC97a], and independently Cory, Havel, and

Fahmy [CFH97], proposed to use bulk spin NMR for experimental quantum computation. They showed how to implement quantum logic operations using liquid state