Final Assembly and Test (FAST) site Installation Manual. Installation

advertisement

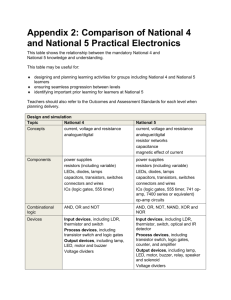

Final Assembly and Test (FAST) site Installation Manual. Installation Before you begin: Check the power voltage selectors on all equipment, and set them to the power voltage for your country if necessary. The instruction below assumes that you already have the chamber with the on-chamber electronics installed. The chamber should be also flushed with the proper gas mixture. Shown below is the list of components that you will need to assemble the FAST site: Table 1 List of components for FAST site assembly 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 CFEB-DMB cables CFEB-TMB cables ALCT-TMB cables LVMB-DMB cable 9U VME crate with VME64x J1 backplane Peripheral backplane GTLP termination voltage regulators for the peripheral backplane VME controller Dynatem-D360 CCB TMB DMB Cat5 network cable (twisted pair) Gigabit Ethernet optical cable Network hub 10-100 Mbit FAST site computer with software and hardware installed in UF Computer monitor Keyboard Mouse High Voltage system /// High Voltage Cable Low Voltage Power supplies, 7.65V 12 A minimum Low Voltage Power cables (AWG 10 or thicker wire) Scintillators and accompanying electronics Mechanical setup 1.Install small peripheral backplane into the 9U VME crate (see Figure 3). 5 5 2 1 1 1 2 1 1 1 1 3 1 1 1 1 1 1 1 1 2 4 1 set a.The power terminals and all board positions have labels showing what is what. b.Put the backplane into the crate and fix it with the screws. It is important to use all screw positions, otherwise the backplane can be damaged. c.You will not have to modify the configuration files if you install the backplane with CCB in position 11. d.Selecting the proper backplane position relative to J1 connector could be perplexing. Simplest way is to insert CCB into the crate and then adjust the backplane according to it. e.Insert the GTLP termination voltage converters into the small connectors on the back of the backplane. There is only one way to do it. f.Connect the GND and 3.3V power from VME crate to the screw terminals on the back of the backplane with thick wires. 2.Install VME controller (D360) into position 1 of VME crate. 3.Connect socket J8 on D360 to the network hub with the Cat5 network cable. 4.Connect network hub to the FAST site computer with the Cat5 network cable. FAST site computer has two network cards. Figure 4 shows the correct connection. This forms a local network, which will be used for VME controller access only. This local network cannot be included into a building network. 5.Connect the FAST site computer to the building network with the Cat5 cable. Figure 4 shows the correct connection 6.Insert CCB into the proper position of the crate (see labels on the backplane) 7.Install TMB into the VME crate: a.Attach 2 ALCT-TMB cables to the TMB connectors, according to labels on TMB and cables (see Figure 9). b.Make sure these cables pass through an opening in TMB front panel, and the TMB cross bar is holding them properly. c.With the ALCT cables attached, insert TMB into the proper position of the crate (see labels on the peripheral backplane). 8.Insert DMB into the proper position of the crate (see labels on the backplane). 9.Attach 5 CFEB-TMB cables to the connectors of TMB and CFEBs, according to Figure 6, Figure 7 and Figure 10. 10.Attach 5 CFEB-DMB cables to the connectors of DMB and CFEBs, according to Figure 6, Figure 7 and Figure 11 11.Attach LVMB-DMB cable to the connectors of DMB and LVMB, according to Figure 8 and Figure 11. 12.Set up both low voltage power supplies for 7.65 volts output, 12 A current limit. 13.Attach low voltage power cables to the output terminals of the low voltage power supplies and to the input terminals of the LVDB (no picture yet). 14.Attach Gigabit Ethernet optical cable to DMB and FAST site computer, according to Figure 4 and Figure 11. Pay attention to connect transmitter of DMB to receiver of computer’s Gigabit Ethernet card, and vice versa. 15.Attach external Level 1 Accept from scintillators to the input connector of CCB according to Figure 12. Currently, the delay of the scintillator trigger logic is required to be as small as possible, otherwise the scintillator-triggered tests may not work properly. 16.Connect monitor, keyboard and mouse to the FAST site computer. 17.Connect High-Voltage cable to the chamber and High-Voltage system. The mechanical portion of the setup is complete. Please check thoroughly that you have connected everything strictly according to the instructions shown above. Bringing the system up 1.Check the power voltage selectors on all equipment, and set them to the power voltage for your country if necessary. 2.Turn on the power of the FAST site computer and the network hub. Wait until the system shows the login screen. 3.The account which you will use for all test activities is: Username: fastdev Password: … 4.The root password … 5.The user can change all passwords, of course. 6.Turn on the low voltage power supplies. The power LED’s of all on-chamber boards should blink once. 7.Turn on the power of the VME crate. 8.Do not turn on the High-Voltage at this point. Configuration files setup The only file containing site-specific parameters is: /home/fastdev/data/daqmb_config/daqmb_config_0023 Shown below are the modifications in this file, and instructions what parameter to modify: 1. 2. 3. 4. Set crate_slt to the position of DMB in the crate Set ccb_slt to the position of CCB in the crate Do not modify tmb_slt Set ALCTtx, ALCTrx and CFEBrx parameters to values corresponding to the cable length you are using, by uncommenting the proper section in the file, and commenting out the other two sections with these parameters. All 12 skew clear cables on your setup must be of equal length. Each cable has a label with the part number: 530020006 – 9 meters 530020007 – 10 meters 530020008 – 11 meters 5. Set DACzero parameter as shown in “DMB test pulse DAC calibration” section below: DMB test pulse DAC calibration Several tests are using the internal DMB test pulse generator. The DACs controlling the amplitude of this pulse are a little bit different on each DMB, so calibration is required. It appears to be possible to correct the difference by using just one parameter - zero offset. The slope of DAC characteristics is pretty uniform for all DMBs, but the zero is different. Please follow the procedure described below, for each newly installed setup or if DMB or CFEB-DMB skew-clear cables have been replaced: 1. Set parameter DACzero in daqmb_config_0023 file to 0. 2. Run “cfeb_control –P 0_32_1”, where 32 is the initial DAC setting in DAC bits. 3. With the millivoltmeter, measure the voltage on the CFEB’s capacitor shown on Figure 13. It should be 39 mV. 4. If it is not 39 mV, adjust the initial DAC setting (32 in step 1) and execute step 2 again, until you see 39 mV on the capacitor. It may require several iterations. Each DAC bit is very approximately equivalent to 1 mV. Let’s say your DAC setting in step 2 after adjusting the voltage is X. 5. Set parameter DACzero in daqmb_config_0023 file to (X-32). It should be decimal number, positive or negative, which represents the deviation of the DAC zero from nominal. 6. Verify if you did everything right by running “cfeb_control –P 0_32_1” again, and measuring the voltage on the capacitor. This time it should be 39 mV. All other modifications of the configuration files must be discussed with the FAST site development team. Downloading the FPGA configuration 1.Start cfeb_control program: cfeb_control<Enter> /// 2.From the menu select: Config->Load Proms->(see table below) 3.Select the SVF file from the file list window (see table below) 4.Press OK and wait until the programming is complete. 5.Exit cfeb_control. 6.Switch the low voltage power supplies off and back on. FPGA configuration files and menu selections: Table 2 Board ALCT CFEB Menu selection after Config->Load Proms Load ALCT-> load ALCT prom Load/prg FEBs->FEBn: load ISPROM (repeat for n = 1 to n = 5) SVF file Depending on your type of ALCT: alct672_virtex.svf alct384_virtex.svf alct288_virtex.svf fcntl_v4_r1.svf Initial tests In all examples below, only the significant portion of the program’s output is shown. LVMB test lvmbctp +v –-chamtype n --test In the command line above n is the chamber type: 0 1 2 3 4 5 6 - ME1/1 ME1/2 ME1/3 ME2/1 ME2/234 ME3/1 ME4/1 This program will repeatedly try to turn the low voltage power on and off for each onchamber board. It will also read voltages and consumption currents from LVMB, and will print error messages if some of the voltages/currents are out of limits. Valid output should look like this: === Testing LVMB Control cfeb_control: Incoming connection cfeb_control: Waiting for data -: No such file or directory Number of passes for each test - 5 All Boards Turned On Test Finished with 0 errors All Boards Turned Off Test Finished with 0 errors Turned On CFEB1 Board Test Finished with 0 errors Turned On CFEB2 Board Test Finished with 0 errors Turned On CFEB3 Board Test Finished with 0 errors Turned On CFEB4 Board Test Finished with 0 errors Turned On CFEB5 Board Test Finished with 0 errors -: No such file or directory Turned On ALCT Board Test Finished with 0 errors === All Tests Finished with 0 errors ALCT test “actp” program will test various parts of ALCT. The supported commands are shown below: --ID Reads ID registers from Virtex and Slow control FPGA. Valid output should look like this: II actp: slow control id: format):07.09.2001 II actp: fast control id: format):25.09.2002 chip:8; version:11; date (Euro chip:7; version:0; date (Euro --rvolt Reads power voltages from ALCT. Valid output should look like this: II actp: 1.8V-> 1.787V, 3.3V-> 3.256V, 5.5V#1-> 5.631V, 5.5V#2-> 5.625V --rcurrent Reads power currents from ALCT. Valid output should look like this: II actp: 1.8I->0.6303A, 3.3I->1.5144A, 5.5I#1->1.5383A, 5.5I#2->1.3890A --rtemp Reads the temperature of FPGA from ALCT. Valid output should look like this: II actp: FPGA temperature: 31.9C --test +v Runs self-test procedure. This test takes a few minutes, so be patient. It will print error messages, if there are any. CFEB test cfeb_eprom_loader program will test CFEBs. Valid output should look like this (the insignificant initial section is skipped): loading new firmware to Cable 1 CFEB 671 PROM ******** buffers transfered 40138 ******** ******** largest buffer 40125 ******** loading new firmware to Cable 2 CFEB 810 PROM ******** buffers transfered 115016 ******** ******** largest buffer 40125 ******** loading new firmware to Cable 3 CFEB 898 PROM ******** buffers transfered 189894 ******** ******** largest buffer 40125 ******** loading new firmware to Cable 4 CFEB 904 PROM ******** buffers transfered 264772 ******** ******** largest buffer 40125 ******** loading new firmware to Cable 5 CFEB 669 PROM ******** buffers transfered 339650 ******** ******** largest buffer 40125 ******** Cable 1 CFEB 669 FPGA loaded correctly Cable 2 CFEB 669 FPGA loaded correctly Cable 3 CFEB 669 FPGA loaded correctly Cable 4 CFEB 669 FPGA loaded correctly Cable 5 CFEB 669 FPGA loaded correctly Reading FEB1 temperature 28.977861 Reading FEB2 temperature 30.081373 Reading FEB3 temperature 30.198891 Reading FEB4 temperature 29.195616 Reading FEB5 temperature 28.799318 passed down threshold = 0.100000 threshod of 0.100000 digitized to 0F89 dv 7 adc value 0d 7f DAQ Voltage 3455.000000 mv passed down threshold = 0.600000 threshod of 0.600000 digitized to 0D40 dv 7 adc value 0b 84 DAQ Voltage 2948.000000 mv CFEB08: comp daq (.50+-.01) 507.000000 passed down threshold = 0.100000 threshod of 0.100000 digitized to 0F89 dv 8 adc value 0d 6c DAQ Voltage 3436.000000 mv passed down threshold = 0.600000 threshod of 0.600000 digitized to 0D40 dv 8 adc value 0b 74 DAQ Voltage 2932.000000 mv CFEB09: comp daq (.50+-.01) 504.000000 passed down threshold = 0.100000 threshod of 0.100000 digitized to 0F89 dv 9 adc value 0d 7b DAQ Voltage 3451.000000 mv passed down threshold = 0.600000 threshod of 0.600000 digitized to 0D40 dv 9 adc value 0b 7f DAQ Voltage 2943.000000 mv CFEB10: comp daq (.50+-.01) 508.000000 passed down threshold = 0.100000 threshod of 0.100000 digitized to 0F89 dv 10 adc value 0d 7e DAQ Voltage 3454.000000 mv passed down threshold = 0.600000 threshod of 0.600000 digitized to 0D40 dv 10 adc value 0b 83 DAQ Voltage 2947.000000 mv CFEB11: comp daq (.50+-.01) 507.000000 passed down threshold = 0.100000 threshod of 0.100000 digitized to 0F89 dv 11 adc value 0d 71 DAQ Voltage 3441.000000 mv passed down threshold = 0.600000 threshod of 0.600000 digitized to 0D40 dv 11 adc value 0b 78 DAQ Voltage 2936.000000 mv CFEB12: comp daq (.50+-.01) 505.000000 After this test the right version of firmware must be downloaded into CFEBs’ configuration EEPROMs. Please see “Downloading FPGA configuration” section for details. Taking data 1.Set the high voltage on the chamber, if the test you want to run requires that. 2.Type run_control <Enter> 3.You will see this window: Figure 1 Init button is used to initialize hardware for the selected test Start button is used to start data acquisition for the selected test Set operator’s name in this field Number of events to acquire in this test. This field is set automatically. Set test number here. The configuration files’ numbers below will be updated automatically. Chamber type (22 means ME2/2) 4.Set test number in Setup Files combo-box (see picture). The configuration files and number of events to collect will be updated automatically. 5.If the chamber type displayed in “Cham” field is wrong, set it to correct value by clicking on this field. 6.Press Init button. Wait until the system finished initializing the hardware. 7.Press Start button. 8.If you need to stop the run, press Stop button, which has appeared as you started the run. All acquired data are written into this directory: /csc_data The filenames are created using the formula: “cscdata_”+(6-digit decimal run number)+”.dat”. The run number increments automatically when the user starts next run. Things to watch during data taking Event display This program can display the event data in the process of data acquisition. Start it by typing event_display<Enter>. Then select File->Open event in shared memory>(Active run number). Figure 2 shows the screenshot of the Event Display. Message Window This program displays various system messages. Critical errors are shown in red color. Start it by typing message_window<Enter>. Troubleshooting Symptom The system was working perfectly, and now it does not. Actions Try these steps one by one, checking if the system works again after trying each one: 1.Close all windows, starting from run_control, then start run_control and try to collect data again. 2.Switch the power of the VME crate and on-chamber electronics off and on again, wait about 1 minute and restart run_control. 3. Reboot the computer. Software is stuck in the middle of the initialization sequence 4. Reload the configuration into all on-chamber boards (see “Downloading the FPGA configuration” section) 1.Check that the chamber type is selected properly (see Figure 1) 2.Check the positions of the boards set in daqmb_config_0023 file. See “Configuration file setup” section for details. 3.Check the cable length setting in daqmb_config_0023 file. See “Configuration file setup” section for details Check the connection of the optical cable. The message “No trigger” appears in the message window, no data is collected The run is stuck in the middle of Disk is full. Remove unused files from /csc_data the test, message “Event is directory. partially written. Errno=28” appears in message window Known issues 1.Message “No trigger” sometimes appears in Message Window. Data collected properly. 2.Message “Checksum error: …” sometimes appears in Message Window. It does not affect the results of the tests. Figure 2 Event display screenshot CFEB data display. Red bars show the peak values of signals detected by CFEBs in this event, for each strip ALCT data display. Blue rectangles show hits in wiregroups detected by ALCT in this event. Use this button to configure the program, and to select data file for display. GTLP voltage regulators Power and ground terminals Figure 3 “Peripheral backplane installation” Building network Local network connection for communication with D360 Figure 4 “Computer back panel connections” Optical cable from DDU. If the connection is correct, LEDs next to connector should be lit as shown when the setup is initialized (Init button is pressed, see Figure 1) Figure 5 “ALCT-TMB cables on ALCT” 1 2 3 4 5 Figure 6 “Order of CFEBs on the chamber” CFEB-TMB cable (5 means CFEB #5, T means TMB) CFEB-DMB cable (5 means CFEB #5, D means DMB) Figure 7 “CFEB-TMB and CFEB-DMB cables connected to CFEB #5” Figure 8 “LVMB-DMB cable connected to LVMB” Figure 9 “ALCT-TMB cables connected to TMB. This connection has to be made BEFORE TMB is inserted into the crate” TMB front panel CFEB-TMB cables ALCT-TMB cables Figure 10 “Cables entering TMB” DMB front panel LVMB-DMB cable CFEB-DMB cables Optical cable to computer Figure 11 “Cables entering DMB” Input connector. Supply external Level 1 accept (ECL) to pins 17(+) and 18(-). It should be positive pulse about 300-500 ns long. Pin 1 Figure 12 “CCB input connector for external Level 1 Accept from scintillators” + _ Figure 13 Measure DMB DAC voltage on CFEB, across the capacitor shown in red.