Sunil Maloo Verilog Presentation 1

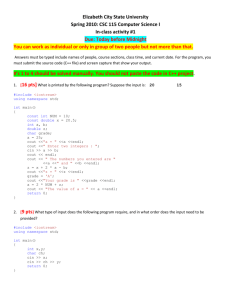

advertisement

Sunil Maloo

Verilog Presentation

1

Verilog HDL

☞ What is Verilog?

➥ Verilog HDL is a Hardware Description Language (HDL)

➥ Verilog HDL allows describe designs at a high level of

abstraction as well as the lower implementation levels

➥ Primary use of HDLs is the simulation of designs

➥ Verilog is a discrete event time simulator

☞ What is VeriWell?

➥ VeriWell is a comprehensive implementation of Verilog HDL

Sunil Maloo

Verilog Presentation

2

Program Structure in Verilog

☞ Verilog allows hierarchy in a design using modules and ports

System

➣

Module_1

Module_2

System instantiates Module_1

and Module_2

➣ Module_2 instantiates Sub_Mod

Sub_Mod

Sunil Maloo

Verilog Presentation

3

Modules

☞ Verilog language describes a digital system as a set of modules

➥ Each of these modules has an interface to other modules to

describe how they are interconnected

➥ Modules represent pieces of hardware ranging from simple

gates to complete systems

➥ Modules can either be specified behaviorally or structurally

(or a combination of the two)

➫ A behavioral model of a module is an abstraction of how

the module works

✔ Useful in early design process to simulate the intended behavior

➫ A structural specification expresses the behavior of a digital

system as a hierarchical interconnection of sub modules

Sunil Maloo

Verilog Presentation

4

Structure of a module

module <module name> (<port list>);

<declares>

<module items>

endmodule

Sunil Maloo

Verilog Presentation

5

Data Types

☞ Physical Data Types

➥ For modeling registers (reg) wires (wire)

➫ The reg variables store the last value that was procedurally

assigned to them

➫ The wire variables represent physical connections between

structural entities such as gates

➥ Memories are specified as vectors of registers

☞ Abstract Data Types

➥ These data types include: integer, real, time

Sunil Maloo

Verilog Presentation

6

Operators

☞ Binary Arithmetic Operators

➥ + - * / %

☞ Unary Arithmetic Operators

➥ - Unary Minus

Changes sign of its operand

☞ Relational Operators

➥ > >= < <=

==

!=

☞ Logical Operators

➥ ! && ||

☞ Bitwise Operators

➥ ~ & | ^

Sunil Maloo

~&

~|

~^

Verilog Presentation

7

Operators

☞ Unary Reduction Operators

➥ ~ & | ^ ~& ~|

~^

☞ Other Operators

➥ ===

Case equality

➥ !==

Case inequality

➥ { , } Concatenation

➥ <<

Shift left

➥ >>

Shift right

➥ ?:

Conditional

Sunil Maloo

Verilog Presentation

8

Tasks and Functions

☞ Tasks are like procedures in other programming languages

☞ Functions act like function subprograms in other languages, except

➥ A Verilog function must execute during one simulation time

unit, i.e., no time controlling statements

➥ A task may contain time controlled statements.

➥ A Verilog function can not invoke (call, enable) a task; whereas

a task may call other tasks and functions.

Sunil Maloo

Verilog Presentation

9

Control Constructs

☞ Selection - if and case Statements

☞ Repetition - for, while and repeat Statements

Timing Control

☞ Verilog language provides two types of explicit timing control

over when simulation time procedural statements are to occur

➥ Delay control

➥ Event expression

☞ If there is no timing control, simulation time does not advance

Sunil Maloo

Verilog Presentation

10

Example

bIn

x1

cOut

x8

x7

x5

aIn

cIn

x2

x4

x3

x9

sum

x6

A One-Bit Full Adder

Sunil Maloo

Verilog Presentation

11

module fullAdder(cOut, sum, aIn, bIn, cIn)

output cOut, sum;

input

aIn, bIn, cIn;

wire

x2;

nand

xnor

nor

or

not

(x2, aIn, bIn),

(cOut, x2, x8);

(x9, x5, x6);

(x5, x1, x3),

(x1, aIn, bIn);

(x8, x1, x7);

(sum, x9),

(x6, x4),

(x4, cIn),

(x7, x6);

endmodule

Sunil Maloo

Verilog Presentation

12

/* A 4 bit ripple carry adder is implemented using structural Verilog HDL */

/* code. a and b are 4 bit inputs and s and c_out are ouputs. s is a 4 bit */

/* sum output and c_out is a 1 bit carry output. */

module adder ();

reg[3:0] a, b;

wire[3:0] s;

wire c_out;

/* declare data types of inputs a and b */

/* declare data type of ouput s */

/* declare data type of output c_out */

/* Instantiate the 1 bit full adder module defined below to form the */

/* 4 blocks of ripple carry adder. The input carry is assumed to be zero. */

fulladder FA0(c1, s[0], a[0], b[0], 1’b0);

fulladder FA1(c2, s[1], a[1], b[1], c1);

fulladder FA2(c3, s[2], a[2], b[2], c2);

fulladder FA3(c_out, s[3], a[3], b[3], c3);

Sunil Maloo

Verilog Presentation

13

/* Test bench to give the inputs and check the output values. The time */

/* variable, inputs and outputs are displayed. */

initial begin

/* Beginning of initial block */

/* The monitor statement monitors the value of variables at all instants */

/* and displays the result whenever there is any change. */

$monitor ($time, “a=%b, b=%b, s=%b, cout=%b, c1=%b, c2=%b, c3=%b “, a,

b, s, c_out, c1, c2, c3);

a=0; b=0;

/* give specific input values */

#100 $display ($time);

/* display the time variable */

#900 a=15; b=15;

#100 $display ($time);

#900 a=0; b=15;

#100 $display ($time);

#900 a=15; b=1;

#100 $display ($time);

#900 a=5; b=7;

#100 $display ($time);

end

/* end of the initial block */

endmodule

/* end of the adder module */

Sunil Maloo

Verilog Presentation

14

/* 1 Bit Full adder module */

module fulladder (cout, si, ai, bi, cin);

parameter delay2=1, delay3=2, delay4=3;

/* variables defined as parameter */

input ai, bi, cin;

output cout, si;

/* declaring inputs */

/* declaring ouputs */

and #delay3 (si1, ~ai, ~bi, cin),

(si2, ~ai, bi, ~cin),

(si3, ai, ~bi, ~cin),

(si4, ai, bi, cin);

or #delay3 (si, si1, si2, si3, si4);

/* si1=~ai.~bi.cin */

/* si2=~ai.bi.~cin */

/* si3=ai.~bi.~cin */

/* si4=ai.bi.cin */

/* si=si1+si2+si3+si4 */

and #delay2 (ci1, ai, bi),

(ci2, ai, cin),

(ci3, bi, cin);

or #delay3 (cout, ci1, ci2, ci3);

endmodule

Sunil Maloo

/* ci1=ai.bi */

/* ci2=ai.cin */

/* ci3=bi.cin */

/* cout=ci1+ci2+ci3 */

Verilog Presentation

15

Output

0 a=0000, b=0000, s=xxxx, cout=x, c1=x, c2=x, c3=x

3 a=0000, b=0000, s=xxxx, cout=0, c1=0, c2=0, c3=0

4 a=0000, b=0000, s=xxx0, cout=0, c1=0, c2=0, c3=0

7 a=0000, b=0000, s=0000, cout=0, c1=0, c2=0, c3=0

100

1000 a=1111, b=1111, s=0000, cout=0, c1=0, c2=0, c3=0

1003 a=1111, b=1111, s=0000, cout=1, c1=1, c2=1, c3=1

1007 a=1111, b=1111, s=1110, cout=1, c1=1, c2=1, c3=1

1100

2000 a=0000, b=1111, s=1110, cout=1, c1=1, c2=1, c3=1

2003 a=0000, b=1111, s=1110, cout=1, c1=0, c2=1, c3=1

2004 a=0000, b=1111, s=0001, cout=1, c1=0, c2=1, c3=1

2006 a=0000, b=1111, s=0001, cout=1, c1=0, c2=0, c3=1

2007 a=0000, b=1111, s=0011, cout=1, c1=0, c2=0, c3=1

2009 a=0000, b=1111, s=0011, cout=1, c1=0, c2=0, c3=0

2010 a=0000, b=1111, s=0111, cout=1, c1=0, c2=0, c3=0

2012 a=0000, b=1111, s=0111, cout=0, c1=0, c2=0, c3=0

2013 a=0000, b=1111, s=1111, cout=0, c1=0, c2=0, c3=0

2100

Sunil Maloo

Verilog Presentation

16

3000

3003

3004

3006

3007

3009

3010

3012

3013

3100

4000

4003

4004

Sunil Maloo

a=1111, b=0001, s=1111, cout=0, c1=0, c2=0, c3=0

a=1111, b=0001, s=1111, cout=0, c1=1, c2=0, c3=0

a=1111, b=0001, s=1110, cout=0, c1=1, c2=0, c3=0

a=1111, b=0001, s=1110, cout=0, c1=1, c2=1, c3=0

a=1111, b=0001, s=1100, cout=0, c1=1, c2=1, c3=0

a=1111, b=0001, s=1100, cout=0, c1=1, c2=1, c3=1

a=1111, b=0001, s=1000, cout=0, c1=1, c2=1, c3=1

a=1111, b=0001, s=1000, cout=1, c1=1, c2=1, c3=1

a=1111, b=0001, s=0000, cout=1, c1=1, c2=1, c3=1

a=0101, b=0111, s=0000, cout=1, c1=1, c2=1, c3=1

a=0101, b=0111, s=0000, cout=0, c1=1, c2=1, c3=1

a=0101, b=0111, s=1100, cout=0, c1=1, c2=1, c3=1

Verilog Presentation

17

Instructions On Using The Veriwell Simulator

☞ Type your code using any text editor like emacs, vi, or pico.

➥ Name the file as <file name>.v, i.e., use .v extension for file name

☞ To simulate the code using the simulator, type “eng veriwell &”

at the prompt. This will open the veriwell console.

☞ Goto menu bar and click on PROJECT. Under PROJECT, click on

NEW PROJECT to create a project. Once a project has been created

you can open the existing project by clicking on OPEN PROJECT.

☞ In the project window, click on PROJECT and add all your

Verilog files by clicking on ADD FILE.

☞ Then simulate your code by clicking on RUN. The output

will appear on the Veriwell console.

☞ For more information on Veriwell simulator, check the online

manual at URL http://www.wellspring.com/download.htm

Sunil Maloo

Verilog Presentation

18