Lab 8: Yet Another Arithmetic Unit Lab

advertisement

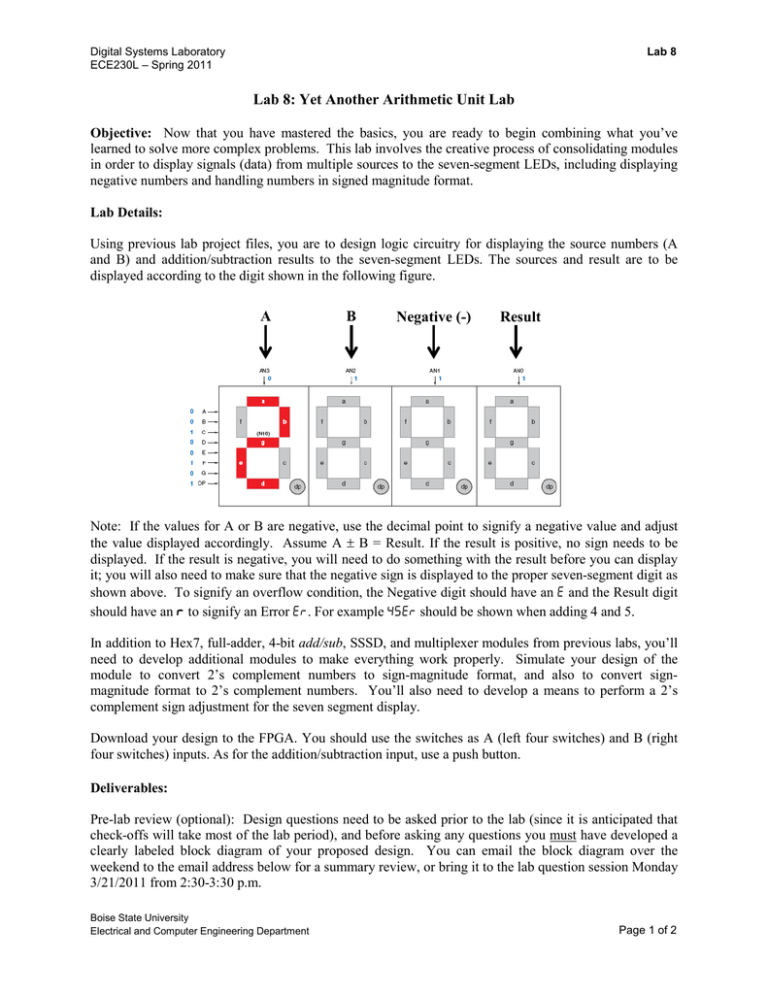

Lab 8 Digital Systems Laboratory ECE230L – Spring 2011 Lab 8: Yet Another Arithmetic Unit Lab Objective: Now that you have mastered the basics, you are ready to begin combining what you’ve learned to solve more complex problems. This lab involves the creative process of consolidating modules in order to display signals (data) from multiple sources to the seven-segment LEDs, including displaying negative numbers and handling numbers in signed magnitude format. Lab Details: Using previous lab project files, you are to design logic circuitry for displaying the source numbers (A and B) and addition/subtraction results to the seven-segment LEDs. The sources and result are to be displayed according to the digit shown in the following figure. A B Negative (-) Result Note: If the values for A or B are negative, use the decimal point to signify a negative value and adjust the value displayed accordingly. Assume A ± B = Result. If the result is positive, no sign needs to be displayed. If the result is negative, you will need to do something with the result before you can display it; you will also need to make sure that the negative sign is displayed to the proper seven-segment digit as shown above. To signify an overflow condition, the Negative digit should have an and the Result digit should have an to signify an Error . For example should be shown when adding 4 and 5. In addition to Hex7, full-adder, 4-bit add/sub, SSSD, and multiplexer modules from previous labs, you’ll need to develop additional modules to make everything work properly. Simulate your design of the module to convert 2’s complement numbers to sign-magnitude format, and also to convert signmagnitude format to 2’s complement numbers. You’ll also need to develop a means to perform a 2’s complement sign adjustment for the seven segment display. Download your design to the FPGA. You should use the switches as A (left four switches) and B (right four switches) inputs. As for the addition/subtraction input, use a push button. Deliverables: Pre-lab review (optional): Design questions need to be asked prior to the lab (since it is anticipated that check-offs will take most of the lab period), and before asking any questions you must have developed a clearly labeled block diagram of your proposed design. You can email the block diagram over the weekend to the email address below for a summary review, or bring it to the lab question session Monday 3/21/2011 from 2:30-3:30 p.m. Boise State University Electrical and Computer Engineering Department Page 1 of 2 Digital Systems Laboratory ECE230L – Spring 2011 Check-off: TA to check off your implementation on the FPGA by end of lab period Submission: Due by Midnight Thursday 3/24/2011 Lab 8 Email: To: ece230lreport@gmail.com cc: your team partner Subject: Lab8_TeamX report (X is your team no.) Attachment: Lab8_TeamX.zip (contents as listed below) Attachment: (must be zip format – no others accepted) Contents of zip file: 1. Report File: \Lab8_TeamX_Report.pdf Report Content (create in Word using template previously provided) 1. Team number, team member names, lab no. and name 2. Clearly and completely describe your design (your design ideas and design decisions), and trade-offs that you have made. Include all appropriate information. After report has been created in Word, create a pdf and then zip. Boise State University Electrical and Computer Engineering Department Page 2 of 2