Lab 5: Seven Segment Decoder Design

advertisement

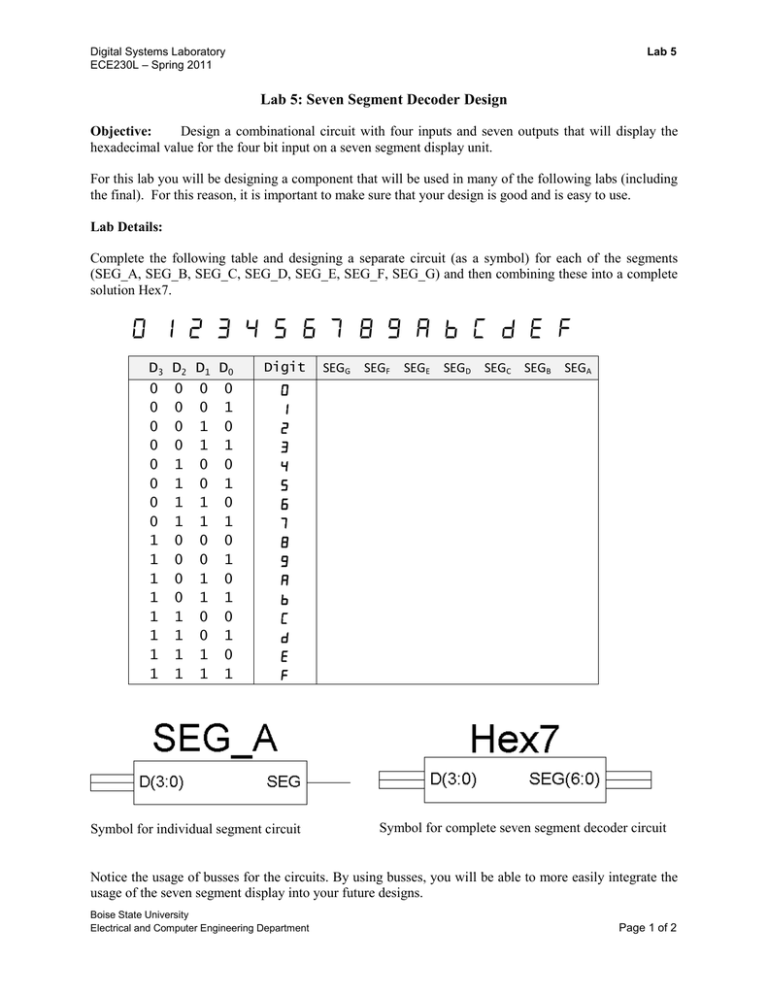

Lab 5 Digital Systems Laboratory ECE230L – Spring 2011 Lab 5: Seven Segment Decoder Design Objective: Design a combinational circuit with four inputs and seven outputs that will display the hexadecimal value for the four bit input on a seven segment display unit. For this lab you will be designing a component that will be used in many of the following labs (including the final). For this reason, it is important to make sure that your design is good and is easy to use. Lab Details: Complete the following table and designing a separate circuit (as a symbol) for each of the segments (SEG_A, SEG_B, SEG_C, SEG_D, SEG_E, SEG_F, SEG_G) and then combining these into a complete solution Hex7. D3 D2 D1 D0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Digit SEGG SEGF SEGE SEGD SEGC SEGB SEGA Symbol for individual segment circuit Symbol for complete seven segment decoder circuit Notice the usage of busses for the circuits. By using busses, you will be able to more easily integrate the usage of the seven segment display into your future designs. Boise State University Electrical and Computer Engineering Department Page 1 of 2 Digital Systems Laboratory ECE230L – Spring 2011 Lab 5 When you have run simulations on the individual segment and combined designs, you can create an instance of the Hex7 symbol in a top level module and connect the inputs to four switches and the appropriate segments of the seven segment display. The values that you will see displayed on the seven segment display will be shown four times. We will be able to send our values to individual elements in future labs. Tasks: 1. From the truth table that you complete, create the minterm Boolean expression for the seven outputs, Draw the schematic for the simplified expressions, Using Xilinx ISE, perform a simulation to verify that the design you have produced gives the results you have for each truth table, Merge the eight output functions into a single circuit utilizing #2 (use the create symbol tool in Xilinx ISE), Implement your design on the FPGA. checkoff______ 2. 3. 4. 5. Report: Record all results in your team report. 1. Truth table, 2. Boolean simplification technique, 3. Chip/FPGA used, 4. Schematic diagram, 5. Simulation waveform, and 6. Results and reflections. Deliverables: Check-off: TA to check off your circuit by end of lab period (11:55 AM) Submission: Due by Midnight Thursday 2/24/2011 Email: To: ece230lreport@gmail.com cc: your team partner Subject: Lab5_TeamX report (X is your team no.) Attachment: Lab5_TeamX.zip (contents as listed below) Attachment: (must be zip format – no others accepted) Contents of zip file: 1. Report File: \Lab5_TeamX_Report.pdf Report Content (create in Word using template previously provided) 1. Team number, team member names, lab no. and name 2. The original and simplified Boolean expressions 3. The original and simplified truth table 4. Simplification technique(s) 5. Type and number of chips used 6. Schematic diagram 7. Simulation waveform 8. Results and reflections After report has been created in Word, create a pdf and then zip. Boise State University Electrical and Computer Engineering Department Page 2 of 2