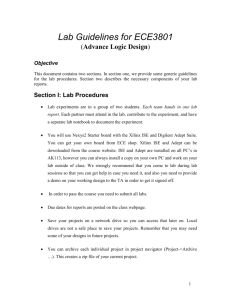

by S. M. Loo, Arlen Planting Department of Electrical and Computer Engineering

Boise State University

Digital Systems Laboratory

EE230L by

S. M. Loo, Arlen Planting

Department of Electrical and Computer Engineering

Boise State University

First Released: Spring 2005 with ISE 6.3i

Updated: Fall 2006 with ISE 8.1i

Updated: Spring 2009 with ISE 10.1

Introduction to Xilinx ISE 1

Boise State University

Digital Systems Laboratory

Introduction

• This tutorial will introduce the Xilinx ISE Computer-Aided

Design (CAD) Software

• The goal of this tutorial is to provide you with the skills to use ISE to facilitate learning digital designs

• This software tool is capable of simulating any digital importantly, in a real-world environment

• You will enter a logic circuit that implements the equal function!

• This tutorial has been prepared by your friendly neighborhood lab assistant and course instructor

EE230L Introduction to Xilinx ISE 2

Boise State University

Digital Systems Laboratory

Start Project Navigator

• Find the Xilinx ISE 10.1 icon on desktop to start Xilinx

Project Navigator and doubleclick the icon

EE230L

• • This is the Xilinx ISE window

• ISE always opens the most recent project! If this subwindow contains data, then use FILE

→

Close Project.

• Note Project Navigator in

Windows task bar.

Introduction to Xilinx ISE 3

Boise State University

Digital Systems Laboratory

Create New Project

• To create a new project, File

→

New Project

EE230L Introduction to Xilinx ISE 4

Boise State University

Digital Systems Laboratory

Name Schematic

When all the fields have been filled, click Next.

EE230L Introduction to Xilinx ISE

• Give a name to the project

• Make sure that the project location is where you want it. has a D drive, and can be used for your designs.

• Top-Level Module

Type is Schematic

5

Boise State University

Digital Systems Laboratory

EE230L

Target Device Specification

• This is important, and will be used later for

FPGA designs.

• Make sure other values match what is shown

• This device required for targeting the FPGA we have in the lab. This will be important when we download to the

FPGA.

Introduction to Xilinx ISE 6

Boise State University

Digital Systems Laboratory

Skip these Dialogs

EE230L Introduction to Xilinx ISE 7

Boise State University

Digital Systems Laboratory

Lab1-Equals Project

• Note the project name

FPGA ID

EE230L Introduction to Xilinx ISE 8

Boise State University

Digital Systems Laboratory

Add Schematic Source to Project

• Now we need to add a schematic source to the project

EE230L Introduction to Xilinx ISE 9

Boise State University

Digital Systems Laboratory

Name Schematic

• Select Schematic

• Name Schematic

EE230L Introduction to Xilinx ISE 10

Boise State University

Digital Systems Laboratory

EE230L

New Schematic Window

Introduction to Xilinx ISE

• A blank schematic sheet has been created and added to the project.

• Double click on

• • You will get this schematic capture window. Re-size the window to optimize the working area. Try to close the middle window (the

“Select Options” window)

11

Boise State University

Digital Systems Laboratory

Change Page Size

• Since this is a small design, we will change the page size to fit an 11”x8.5” sheet of paper.

EE230L Introduction to Xilinx ISE 12

Boise State University

Digital Systems Laboratory

Set Page Size to 11”x8.5”

EE230L

• You can always increase the page size by revisiting these steps.

Introduction to Xilinx ISE 13

Boise State University

Digital Systems Laboratory

EE230L

Add Symbols

• Now we want to add the component symbols to the schematic

• Select the Add

Symbol button from the toolbar.

Introduction to Xilinx ISE

• Hitting the Esc key will cancel the Add

Symbol mode.

14

Boise State University

Digital Systems Laboratory

Add Title to Schematic Diagram

• Symbol categories

• Symbols within each category

EE230L Introduction to Xilinx ISE 15

Boise State University

Digital Systems Laboratory

EE230L

Add Inv Symbols

• Select “Logic”

Category and find

“Inv” (abbreviation for inverter)

• Place two “Inv” on the sheet, by clicking at the desired locations

• Symbols can be moved by clicking once at the symbol. This turns the symbol to red, then it can be moved

Introduction to Xilinx ISE 16

Boise State University

Digital Systems Laboratory

Add 2-input AND Symbols

• Select the

AND2 symbol and click on drawing where you wish to add symbol

• Add two

AND2 symbols

EE230L Introduction to Xilinx ISE 17

Boise State University

Digital Systems Laboratory

EE230L

Add 2-input OR Symbol

• Select the

OR2 symbol and click on drawing where you wish to add symbol

Introduction to Xilinx ISE

• Add one OR2 symbol

• Organize the symbols as you see in this figure

18

Boise State University

Digital Systems Laboratory

Label Symbols

• Right Click on symbol and select Object Properties

– This step is to label the symbols to something that could be more meaningful to you by changing to the Value of InstName

• This step is optional

EE230L Introduction to Xilinx ISE 19

Boise State University

Digital Systems Laboratory

Set Symbol’s Properties

• Change InstName Value as you desire

EE230L Introduction to Xilinx ISE 20

Boise State University

Digital Systems Laboratory

EE230L

Add Wires

• Now add wires to connect the symbols

• Close the Source window by (pulldown menu) View

→

Source

• Open the Processes window by

(pull-down menu) View

→

Processes

• Select the Add Wire button from

• On the options tab, select the Use the Manual method …

• Hitting the Esc key will cancel the

Add Wire mode and lead to this window that is very useful for selecting a wire

Introduction to Xilinx ISE 21

Boise State University

Digital Systems Laboratory

Add Wire Step 1

• Connect these two segments as indicated by the green arrows

EE230L Introduction to Xilinx ISE 22

Boise State University

Digital Systems Laboratory

Add Wire Step 2

• Hover over as indicated by the red arrow until the cursor image changes to connection point indicator

• Connection point indicator

EE230L Introduction to Xilinx ISE 23

Boise State University

Digital Systems Laboratory

Add Wire Step 3

• Left click (hold the left button) and drag wire as shown in figure

• Once connection indicator appears, release mouse button

EE230L Introduction to Xilinx ISE 24

Boise State University

Digital Systems Laboratory

Schematic with Wires

• Repeat until you have connected all of the pins

• For pins that are connected to external devices such as switches and LEDs, just add wire and leave unconnected on that end

• Does your schematic look like the one above?

EE230L Introduction to Xilinx ISE 25

Boise State University

Digital Systems Laboratory

Add I/O Markers (or I/O Pads)

• Select the Add

I/O Marker button from the toolbar

EE230L Introduction to Xilinx ISE 26

Boise State University

Digital Systems Laboratory

Add Input/Output Markers

• Select “Add an input marker”

• Add input markers

• Select “Add an output marker”

• Add output marker

EE230L Introduction to Xilinx ISE 27

Boise State University

Digital Systems Laboratory

Label I/O Markers

• Right Click I/O Markers and select Rename

Port

• Input names should be

• Output name should be LED1

EE230L Introduction to Xilinx ISE 28

Boise State University

Digital Systems Laboratory

Save and Check Schematic

• Save the schematic diagram

• Activate the schematic check routine (pull-down menu), Tools

→

Check

Schematic

• Fix any error you might have and run the check routine

– Observe the bottom window for these messages

• “Start DRC …”

• “No error or warning is detected”

• You can print your schematic diagram (portrait or landscape) or even

• Save the diagram before you exit the schematic capture tool (by clicking on the

× on the top right hand corner of the schematic capture window)

EE230L Introduction to Xilinx ISE 29

Boise State University

Digital Systems Laboratory

Back to Project Design

Summary

EE230L Introduction to Xilinx ISE 30

Boise State University

Digital Systems Laboratory

Add Test Bench Source

• The circuit entry is completed, but how do we know whether the design works?

• We will test our design using a test bench!

EE230L Introduction to Xilinx ISE 31

Boise State University

Digital Systems Laboratory

Name Test Bench

• Select Test Bench

Waveform

• Name Test Bench

EE230L Introduction to Xilinx ISE 32

Boise State University

Digital Systems Laboratory

Associate Test Bench With Schematic

• Select the schematic that is to be used by this

Test Bench

EE230L Introduction to Xilinx ISE 33

Boise State University

Digital Systems Laboratory

Test Bench Creation

EE230L Introduction to Xilinx ISE 34

Boise State University

Digital Systems Laboratory

EE230L Introduction to Xilinx ISE 35

Boise State University

Digital Systems Laboratory

Accept Default Timing

Values

EE230L Introduction to Xilinx ISE 36

Boise State University

Digital Systems Laboratory

New Test Bench Window

• The waveform window is part of ISE

EE230L Introduction to Xilinx ISE 37

Boise State University

Digital Systems Laboratory

Define Input Values

• Note the vertical blue line in column 1000 - this is the end of test marker. It was set in the initial slide. You can reset this number by positioning the pointer on top of the blue line close to the time ruler and right clicking.

• Why are the values for SW1 and SW2 defined this way?

You need to understand.

EE230L Introduction to Xilinx ISE 38

Boise State University

Digital Systems Laboratory

Save Test Bench Definition

• The Test Bench is not added to the project until you have saved this file

EE230L Introduction to Xilinx ISE 39

Boise State University

Digital Systems Laboratory

Test Bench & Project

• Note that the Test Bench

TB_Equals has been added to the project

• Select the “Behavioral

Simulation” from the pulldown menu as shown and waveform window

EE230L Introduction to Xilinx ISE 40

Boise State University

Digital Systems Laboratory

Activate Simulation

• Make sure that

TB_Equals.tbw is selected

• Note the entries in figure

• We want to use Simulate

Behavioral Model

• This will create a new set separate from ISE

EE230L Introduction to Xilinx ISE 41

Boise State University

Digital Systems Laboratory

Wave Default

• Multiple windows will appear on Xilinx ISE

Simulation

EE230L Introduction to Xilinx ISE 42

Boise State University

Digital Systems Laboratory

Zoom to View Wave

• You can move the blue cursor to observe the values at different times.

EE230L Introduction to Xilinx ISE 43

Boise State University

Digital Systems Laboratory

• Close Xilinx ISE 10.1

Close Windows

EE230L Introduction to Xilinx ISE 44

Boise State University

Digital Systems Laboratory

Now wasn’t that simple ?

EE230L Introduction to Xilinx ISE 45

Boise State University

Digital Systems Laboratory

And don’t you forget it !

EE230L Introduction to Xilinx ISE 46