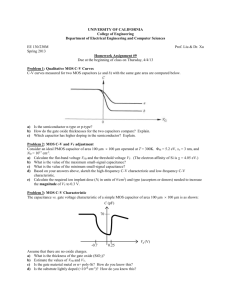

Hysteresis and Memory Effects in ... Embedded MOS Capacitors Eralp Atmaca

advertisement