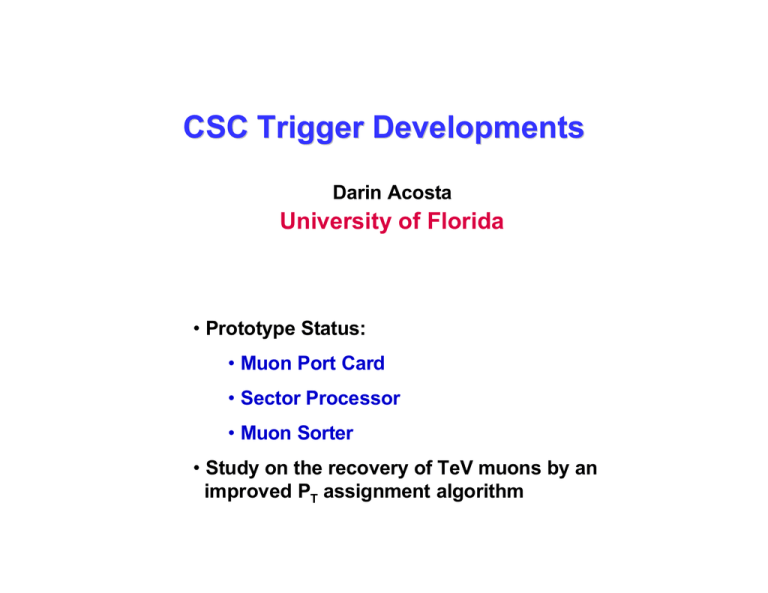

CSC Trigger Developments University of Florida Darin Acosta improved P

advertisement

CSC Trigger Developments Darin Acosta University of Florida • Prototype Status: • Muon Port Card • Sector Processor • Muon Sorter • Study on the recovery of TeV muons by an improved PT assignment algorithm CSC Muon Trigger Scheme TriDAS part: Second generation prototypes EMU part: mostly in production Muon Portcard (1) Trigger Motherboard (9) Clock Control Board Trigger Timing & Control DAQ Motherboard (9) D T D T D T D T D T C MT D T D T D T D M M M MM M M M M M C P M M M M M M M M C B B B B B B B B B B B C B BB B B B B B O N T R O L L E R Optical link 1 of 5 Muon Sorter (1) 1 of 5 Sector Processor (12) CFEB CFEB CFEB CFEB CFEB CSC Track-Finder Crate (1) In underground counting room 3-D Track-Finding and Measurement CMS Week, 25 Feb 2003 Peripheral Crate on iron disk (1 of 48) Cathode Front-end Board 1 of 2 1 of 24 LVDB ALCT Anode LCT Board On detector Trigger Primitives 2 CSC Anode Front-end Board D.Acosta, University of Florida Muon Port Card (2nd Prototype) Rice VME Interface (glue logic) GTLP Receivers Optomodules CMS Week, 25 Feb 2003 TLK2501 serializers Mezzanine card 3 D.Acosta, University of Florida MPC Design Status Rice • 3 boards have been fabricated and assembled in summer • Have 6 UCLA mezzanine cards in hand • Tested MPC standalone (sorter logic) and with one and two Trigger Motherboards and full-size custom backplane - various patterns sent from TMB to MPC at 80Mhz - feedback “winner” bits from MPC to TMB - periodic FPGA reconfiguration from EPROMs (both MPC and TMB) upon “hard reset” - measured the board latency Waiting to test with Sector Receiver/Processor CMS Week, 25 Feb 2003 4 D.Acosta, University of Florida CSC Track-Finder Crate Muon Sorter SRSR SRSR SRSR / / / / / / SP SP SP SP SP SP MS CCB Clock and Control Board SBS 620 Controller Second generation prototypes SRSRSR SRSR SR / / / / / / SP SP SP SP SP SP Sector Processor From MPC (chamber 4) From MPC (chamber 3) From MPC (chamber 2) From MPC (chamber 1B) From MPC (chamber 1A) To DAQ • Single Track-Finder Crate Design with 1.6 Gbit/s optical links CMS Week, 25 Feb 2003 5 D.Acosta, University of Florida Next Generation Sector Processor New SR links Phi Global LUT Eta Global LUT and LUTs DC-DC Converter Phi Local LUT EEPROM VME/CCB FPGA Stiffener Indicators Main FPGA XC2V4000 Fits all of previous SP board logic! FM RJ45 TLK2501 Transceiver Front FPGA From CCB To MS DDU FPGA PT LUT Optical Transceivers (16) Mezzanine Card MB1-to-SP ME1-to-DT SRAM CMS Week, 25 Feb 2003 6 D.Acosta, University of Florida Next Generation Sector Processor CMS Week, 25 Feb 2003 7 D.Acosta, University of Florida Tests underway… CMS Week, 25 Feb 2003 8 D.Acosta, University of Florida Track-Finder Test Plans Tests Both SP main board and mezzanine board pass power-up and initial FPGA programming tests p EEPROMs programmed via JTAG through VME bus è Validation of VME interface is underway è Optical link tests are next è Oops… Approximate schedule è è è è è Feb.’03: SP prototype completed, initial tests begin Mar.’03: MPC→SP optical link tests Apr.’03: SP trigger logic tests May.’03: CSC system tests with cosmic rays and beam tests at CERN June ’03… : Tests with Muon Sorter and DT Track-Finder CMS Week, 25 Feb 2003 9 D.Acosta, University of Florida CSC Muon Sorter Rice Univ. Functionality VME J1 BACKPLANE 9U * 400 MM BOARD VME/JTAG INTERFACE LVDS DRIVERS • Selects 4 best muons out of 36 arriving from 12 Sector Processors • Sorting is based on 7-bit Rank • Transmits 4 best muons to Global Muon Trigger crate over LVDS links in ranked order SCSI-3 CONNECTORS CCB SP1 1st CABLES TO GLOBAL MUON TRIGGER CRATE CCB INTERFACE SP3 SP10 2nd SORTER LOGIC 3rd INPUT AND OUTPUT FIFO BUFFERS 4th SP12 SP5 CUSTOM BACKPLANE SP8 SP6 SP7 SP4 SP9 SP2 MEZZANINE CARD Xilinx XC2V4000 SP11 WINNERS GTLP TRANSCEIVERS Status • Board layout just completed • Expect 3 PCBs in early March • Uses same mezzanine card as SP • Standalone tests in March-May Tests with SP starts in summer CMS Week, 25 Feb 2003 10 D.Acosta, University of Florida CSC Track-Finder Control and DAQ A draft document on the control and DAQ software framework for CSC Track-Finder has been started: è http://www.phys.ufl.edu/cms/tfcvs/cgibin/cgi/viewcvs.cgi/TrigDAQ/doc/ trigdaq.ps è (includes brief description of data format) Inputs and outputs of Sector Processors are read out upon L1A (including Sorter “winner bits”) Useful for High Level Triggers as well as monitoring and debugging è Send by optical links to an Endcap Muon FED è CMS Week, 25 Feb 2003 11 D.Acosta, University of Florida Study: PT Misassignment from Muon Bremsstrahlung • Poor PT assignment is caused by track segments not collinear with actual muon. • We should be able to eliminate these segments by examining all ∆φ values from 4 ME stations. • Example, for Generated Pt=75 GeV, reconstructed Pt=14 GeV: Overlapped Event Display § ∆φ12= 1 Strip § ∆φ13= 1 Strip § ∆φ23= 1.5 Strips µ Station 3 Hits Station 2 Hits § ∆φ24= 1 Strip § ∆φ34= 1/2 Strip Should be < 1 strip B. Scurlock CMS Week, 25 Feb 2003 12 D.Acosta, University of Florida Pt Misassignment from Bremsstrahlung and Showers We can eliminate bad LCTs by adding some simple “trajectory cleaning” logic within the Sector Processor. For Example: ME1 ME2 ME3 ME4 X X X X • If |∆φ13|> |∆φ12| AND • |∆φ23|> |∆φ24| AND • |∆φ13|>threshold, ∴ should drop ME3 segment from track and use (∆φ12, ∆φ24) for PT assignment. n.b. Translation to Verilog, and latency, must still be studied… B. Scurlock CMS Week, 25 Feb 2003 13 D.Acosta, University of Florida TeV µ Pt Assignment: Using ME4/1 and AU Correction •Plot Level-1 trigger efficiency for PT=300 GeV (P~1 TeV) muons to pass “tight” (3-station) CSC T-F requirement for adequate rate reduction. ME4/1 does recover efficiency. With ME4/1 AND AU Corrections Without ME4/1 Pt>14 Pt>20 Pt>30 Pt>14 Pt>20 Pt>30 ME4/2 ME4/1 RPC Limit 1.8<η<2.1 and Pt>20 With ME4/1 AND AU Corrections: ε = 87.8%, was 74% (No ME4/1) B. Scurlock CMS Week, 25 Feb 2003 ∆ε/ε=15.4% ! 14 D.Acosta, University of Florida 50<Pt<100 Assignment: Using ME4/1 and AU Correction • Plot same CSC T-F efficiency for muons with 50 GeV<PT<100 GeV to pass “tight” (3-station) requirement. With ME4/1 AND AU Corrections Without ME4/1 Pt>14 Pt>20 Pt>30 Pt>14 Pt>20 Pt>30 ME4/2 ME4/1 RPC Limit 1.8<η<2.1 and Pt>20 With ME4/1 AND AU Corrections: ε = 92.6%, was 82% (No ME4/1) B. Scurlock CMS Week, 25 Feb 2003 ∆ε/ε=11.5% 15 D.Acosta, University of Florida 50<Pt<100 Assignment: Using ME4/1 and AU Correction • Plot Pt Efficiency for muons with 50 GeV<PT<100 GeV. Note: Negative Slopes disappear 10 10 20 40 20 60 40 60 With ME4/1 AND AU Corrections With ME4/1 NO AU Corrections B. Scurlock CMS Week, 25 Feb 2003 16 D.Acosta, University of Florida Adding Neutrons at L =3x1034cm-2s-1 PT > 20 Conservative choice Single TeV µ Events Single µ Events 50<PT<100 Without ME4/1: ε = 72% With AU Corrections: ε = 86.3% ∆ε/ε = 20% Without ME4/1: ε = 79.5% With AU Corrections: ε = 90.8% ∆ε/ε = 14% Even larger improvement seen CMS Week, 25 Feb 2003 17 D.Acosta, University of Florida Summary of Study In Region 1.8<η<2.1: ε No Neutrons No ME4/1 No Neutrons AU Correction With Neutrons No ME4/1 With Neutrons AU Correction 50<PT gen<100 82% 92.6% 79.5% 90.8% TeV 74% 87.8% 71.9% 86.3% ∆ε/ε Neutron Effect No ME4/1 Neutron Effect AU Correction AU Correction Effect No Neutrons AU Correction Effect With Neutrons 50<PT gen<100 -3% -2% +13% +14.2% TeV -2.8% -1.7% +18.6% +20% Only works if we re-scope ME4… B. Scurlock CMS Week, 25 Feb 2003 18 D.Acosta, University of Florida