Computer Architecture - QA Chapter 2. By Shinping Wang

advertisement

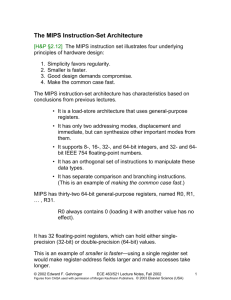

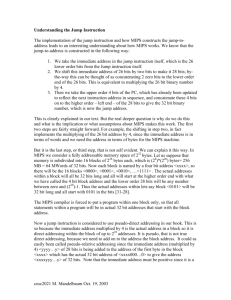

Computer Architecture - QA Chapter 2. By Shinping Wang 2.12 Putting it all together MIPS architecture Section 2.2 – use general purpose registers with load store machine section 2.3 – Supporting addressing mode: displacement, immediate, and register indirect. section 2.5 – supporting data size and type of – 8, 16, 32, and 64 bit integer and 64 bit floating point. section 2.7 – Support simple instructions: load, store, add, subtract, move register-register, and shift. 2.12 Putting it all together MIPS architecture Section 2.9- Flow control: compare, branch with a PC-relative address at least 8 bit lone, jump, call and return. Section 2.11- At least 16 general purpose registers, operation orthogonal to operands, aim on a minimalist instruction set. Section 2.12 Register for MIPS(MIPS64) 32 X 64 bit General Purpose Registers (GPRs) 32 X 64 bit Floating Point Registers (FPRs) R0, R1, R2,….R31 R0 = 0 to synthesize a variety of useful operation from a simple instruction set. F0, F1, F2, .. , F31 F0, F2, .., F30 or 16 double precision FPRs A few special register : status, control, and etc. MIPS (MIPS64) Register GPR R0 R1 R2 R3 R4 R5 R30 R31 64bits FPR F0 F2 F4 Special F1 F3 F5 Status Control IF 32bits F28 F30 F29 F31 32bits 32bits PC NPC A B 64bits 64bits Section 2.12 Data type for MIPS64 integer floating point 8-bit bytes 16-bits half word 32-bit words 64-bit double word 32-bit single precision 64-bit double precision MIPS64 is a 64 bits machine Section 2.12 Addressing modes for MIPS64 data transfer MIPS64 memory is byte addressable in Big of Little Endian selectable 64-bit addresses memory-register transfer relies solely on load or store operation. All memory access must be aligned Section 2.12 Addressing modes for MIPS64 data transfer Data addressing mode 9 immediate mode 9 Load R4, 100(R1) Regs[R4] ←Regs[R4] +Mem[100+Regs[R1]] register deferred (displacement mode with value 0) Regs[R4] ← Regs[R4]+3 displacement mode Load R4, #3 Only this two are implemented Load R3, (R1) Regs[R4] ←Regs[R4] +Mem[0+Regs[R1]] absolute mode (displacement mode with base register R0, and a 16 bit displacement) Load R1, (1001) Regs[R1] ←Mem[Regs[R0] + 1001] Section 2.12 MIPS64 Instruction Format Since only two addressing mode, they are encoded into the opcode. E_OPERAND=OP_TYPE and ADDR_MODE All instruction are 32 bits with 6-bit primary opcode 16 bits fields for displacement addressing immediate constatn PC-relative brance address Section 2.12 MIPS64 Instruction Format I type load,store,Condition brance, R type register-register ALU operations shamt – shift amount J type jump, trap, Section 2.12 MIPS64 Operation There are 4 types of operation loads and stores (I type) ALU operations branches and jumps floating-point operations (I and R type) (J and I type) Section 2.12 MIPS64 Operation Example of supported loads and stores operations LH R10, (R8) Load Half Word selected bit field replicating 8 times Regs[R10]16..31 ←16(Mem[Regs[R8]]0)8 ## Mem[Regs[R8]] concatenate the content of Mem[Regs[R8]] is sign extended to 16 bits and loaded into lower half of R10, the upper half of R10 is unchanged Section 2.12 MIPS64 Operation (32 bit operation) Example of supported loads and stores operations. See fig 2.28 from Text Version 3. displacement displacement(absolute) concatenate replicating 16 times selected bit field Section 2.12 MIPS64 Operation (32 bit operation) ALU instructions are encoded either R-type or Itype that include Add, Subtract, AND, OR, XOR, and shifts. For example: see fig. 2.29 from text ver. 3 shamt Section 2.12 MIPS64 Operation (32 bit operation) Jump and branch J and I types encoding. See fig. 2.30 of text ver.3. Section 2.12 MIPS64 Operation (32 bit operation) jump PC relatively with 26 bits offset jump with register directly 26 bits Return address signed offset See fig. 2.30 of text ver.3. Section 2.12 MIPS64 Operation (32 bit operation) plain jump 26 bits in R13 jump with return Return address stored address signed offset See fig. 2.30 of text ver.3. Section 2.12 MIPS64 Operation (32 bit operation) All branch are conditional 16 bits signed offset Section 2.12 MIPS64 Operation (32 bit operation) MIPS64 Floating Pointing Skipped Section 2.12 Operation (32 bit MIPS64 operation) MIPS instruction set usage