Chapter 2 - Digital Logic

advertisement

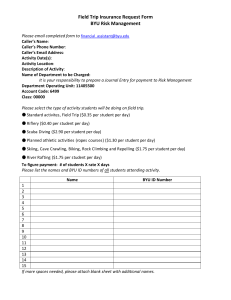

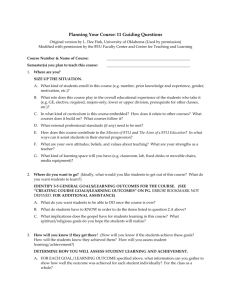

S02 - Digital Logic Required: Recommended: PM: Ch 2, pgs 5-25 Code: Chs 10-16 Wiki: Finite State Machine Transistors and Faucets Gates, Tables, Expressions Combinational Logic Sequential Logic CS 224 Chapter Lab Homework L01: Data Types L02: FSM HW01 HW02 L03: Blinky L04: Microarch L05b: Traffic Light L06a: Morse Code HW03 HW04 HW05 HW06 L07b: Morse II L08a: Life L09b: Snake L10a: Threads HW07 HW08 HW09 HW10 S00: Introduction Unit 1: Digital Logic S01: Data Types S02: Digital Logic Unit 2: ISA S03: ISA S04: Microarchitecture S05: Stacks / Interrupts S06: Assembly Unit 3: C S07: C Language S08: Pointers S09: Structs S10: Threads S11: I/O BYU CS 224 S02 - Digital Logic 2 Learning Outcomes… Learning Outcomes Topics After completing this section, students will be able to: Use transistors to create an invertor, OR, and/or AND gate. Convert a logical equation to a truth table or digital gates. Convert a truth table to digital gates or a logical equation. Convert digital gates to a logical equation or a truth table Use combinational logic to create any logical device (logical completeness). Create computer memory using sequential logic. Use a finite state machine in a practical application. BYU CS 224 S02 - Digital Logic Logical and Arithmetic Operations Digital Logic Devices The Transistor Devices: Inverter, NAND, NOR, Drivers Gates, Truth Tables, and Equations Equations De Morgan’s Law Translations Boolean Algebra Combinational Logic devices Decodes, Multiplexors, Adders, PLAs Logical Completeness Sequential Logic Latches Memory Finite State Machine Turing Machine 3 Solving Problems Problem Solving w/Computers Wordprocessing… Games… Surfing the web… Logic/Circuit Design: gates and low-level circuits to implement components 101011011… Devices BYU CS 224 S02 - Digital Logic 4 Logical and Arithmetic Operations Logical Operations Logical Operations A B NOT A A OR B A NOR B A AND B A NAND B 0 0 1 1 0 1 0 1 1 1 0 0 0 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 A XOR B 0 1 1 0 NOT – Logical complement OR, NOR – Logical disjunction AND, NAND – Logical conjunction XOR – Exclusive OR, A OR B, but not both Bitwise: BYU CS 224 OR 1010 0111 1111 1010 AND 0111 0010 1010 XOR 0111 1101 S02 - Digital Logic 6 Logical/Arithmetic Operations Exercise 2.1 1. What are the results of the following 4-bit logical operations? NOT 10112 10012 OR 10112 10012 NOR 10112 10012 AND 10112 10012 NAND 10112 10012 XOR 10112 2. What are the results of the following 4-bit arithmetic operations (2’s complement)? NEG 10112 10012 ADD 10112 10012 SUB 10112 BYU CS 224 S02 - Digital Logic 7 The Transistor The Transistor Semiconductors A semiconductor is a material which has electrical conductivity properties of a metal (such as copper) and that of an insulator (such as glass). Semiconductors are the foundation of modern solid state electronics. BYU CS 224 S02 - Digital Logic 9 The Transistor History of the Transistor Around 1945, Bell Labs scientists discovered that silicon was comprised of two distinct regions differentiated by the way in which they favored current flow. The area that favored positive current flow they named "p" and the area that favored negative current flow they named "n". The transistor effect describes the change from a condition of conductivity (switched “on”, full current flow) to a condition of insulation (switched “off”, no current flow). BYU CS 224 S02 - Digital Logic 10 The Transistor Digital Logic Circuits Computers = large number of simple structures Intel 4004 = 2,300 transistors Intel Pentium 4 = 42 million transistors Intel Core 2 Duo = 291 million transistors Intel i7 “Bloomfield” = 731 million transistors BYU CS 224 S02 - Digital Logic 11 The Transistor The MOS Transistor A transistor acts like a switch Conducts current when "ON" No current flow when "OFF" N-type Transistor current flow current flow gate P-type Transistor gate Complementary Gate (input) FET (output) Gate (input) FET (output) GND (0) Open GND (0) Closed Vcc (3.3v) Closed Vcc (3.3v) Open MOS = metal-oxide semiconductor CMOS = complementary MOS with both N and P transistors BYU CS 224 S02 - Digital Logic 12 The Transistor CMOS Gates Complementary pull-up / pull-down logic pull-down is " ON" when pull-up is "OFF " and vise versa. 1 Pull-up Structure (P-Type) Output Complementary Pull-down Structure (N-Type) The “C” in CMOS Even in the digital world, "EVERYTHING IS ANALOG"! BYU CS 224 S02 - Digital Logic 0 13 Digital Logic Devices The Inverter 3.3v relative to ground. 1 1 1 on off in out 0 1 1 0 on 0 0 In out 0 1 1 0 BYU CS 224 off 0 Symbols are abstractions! Truth-table lists output for all possible inputs. S02 - Digital Logic 14 Digital Logic Devices The NOR Gate (NOT-OR) 1 1 a 0 b 0 1 a on b on NOR on off 1 0 0 0 a b NOR 0 0 1 0 1 0 1 0 0 1 1 0 BYU CS 224 off off on off 0 0 0 0 S02 - Digital Logic 15 Digital Logic Devices The OR Gate How do you build an OR gate? 1 a 1 a b OR 0 BYU CS 224 0 OR b 0 S02 - Digital Logic a b OR 0 0 0 0 1 1 1 0 1 1 1 1 16 Digital Logic Devices The NAND Gate (NOT-AND) 1 1 1 1 1 1 off off on off NAND b 1 0 1 1 on a 1 0 a b NAND 0 0 1 0 1 1 1 0 1 1 1 0 BYU CS 224 on 0 on off 0 0 S02 - Digital Logic 17 Digital Logic Devices The AND Gate How do you build an AND gate? a AND AND b b a BYU CS 224 S02 - Digital Logic a b AND 0 0 0 0 1 0 1 0 0 1 1 1 18 Digital Logic Devices Drivers Why can’t complementary logic connect to a bus? Bus A 0 and a 1 on the bus would let the magic smoke out! Solution: Tri-state driver: All OFF 1 +3.3v Any ON 0 Bus Select Input BYU CS 224 Pull-up Output S02 - Digital Logic 19 Digital Logic Devices Exercise 2.2 What is the output of the following logic circuit if a=0, b=1, c=0? Draw the corresponding symbol. BYU CS 224 S02 - Digital Logic 20 Solving Problems Problem Solving w/Computers Wordprocessing… Games… Surfing the web… Circuits Logic/Circuit Design: gates and low-level circuits to implement components 101011011… Devices Process Engineering & Fabrication: develop and manufacture lowest-level components BYU CS 224 S02 - Digital Logic 21 Gates, Truth Tables, and Equations BYU CS 224 S02 - Digital Logic 22 Equations Notation and Precedence Logical operator notation (in order of precedence): NOT, bar, circle, ~, ¬ AND, *, , OR, +, Examples: y = NOT(s) AND a AND NOT(b) out s a sb y = (~s a ~b) + (~s a b) A B AB BYU CS 224 ¬(x y) = ¬x ¬y S02 - Digital Logic 23 De Morgan’s Law De Morgan’s Law To distribute the bar, change the operation. A B AB NOR Symbols A B A B NAND Symbols BYU CS 224 S02 - Digital Logic 24 Translations You Should Know How to Translate These are three different ways of representing logical information Logic Equations Logic Gates BYU CS 224 You can convert any one of them to any other Truth Tables S02 - Digital Logic 25 Translations Equations to Gates/Truth Tables out s ab s ab sa b sab s a b s a b s a b s a b BYU CS 224 out S02 - Digital Logic s 0 0 0 0 1 1 1 1 a 0 0 1 1 0 0 1 1 b 0 1 0 1 0 1 0 1 out 0 0 1 1 0 1 0 1 26 Translations Gates to Truth Tables/Equations A 0 0 1 1 BYU CS 224 B 0 1 0 1 AB 0 1 1 0 (NOT(A) AND B) OR (A AND NOT(B)) S02 - Digital Logic 27 Translations Truth Tables to Gates/Equations A 0 0 0 0 1 1 1 1 S 0 0 1 1 0 0 1 1 B 0 1 0 1 0 1 0 1 C 0 0 0 1 1 1 0 1 C = (~A × S × B) + (A × ~S × ~B) + (A × ~S × B) + (A × S × B) BYU CS 224 S02 - Digital Logic 28 Boolean Algebra Manipulating Logic Expressions Laws (basic identities) of Boolean algebra. Law OR AND Identity One/Zero Idempotent Inverse Commutative Associative Distributive DeMorgan’s x0=x x1=x x1=1 x0=0 xx= x xx=x x ¬x = 1 x ¬x = 0 xy=yx xy=yx (x y) z = x (y z) (x y) z = x (y z) x (y z) = (x y) (x z) x (y z) = (x y) (x z) ¬(x y) = ¬x ¬y ¬(x y) = ¬x ¬y BYU CS 224 S02 - Digital Logic 29 Quiz Exercise 2.3 What is the logical equation and truth table for the following circuit? BYU CS 224 S02 - Digital Logic 30 Review CMOS a NOT NAND b NOR OUT b Select a in out 0 1 1 0 BYU CS 224 a b NOR 00 1 01 0 10 0 11 0 Input a b NAND 00 1 01 1 10 1 11 0 S02 - Digital Logic in sel out 0 0 0 1 0 1 0 1 1 - 31 Combinational Logic Devices Circuits Decoders Decode the input and signify its value by raising just one of its outputs. 1A 0B BYU CS 224 0W W 2-to-4 Decoder X 1 Y 1 if A,B = 10 0 Z 1 if A,B = 11 Y Z A B DECODER Symbol 1 if A,B = 00 0 X 1 if A,B = 01 S02 - Digital Logic A 0 0 1 1 B 0 1 0 1 W 1 0 0 0 X 0 1 0 0 Y 0 0 1 0 Z 0 0 0 1 33 Circuits Multiplexors Connect one of its inputs to its output according to select signals A B 1 0 1 1 Useful for selecting one from a collection of data inputs. Usually has 2n inputs and n select lines. BYU CS 224 S02 - Digital Logic B 0 1 S C MULTIPLEXOR Symbol S C A A 0 1 - B 0 1 S 0 0 1 1 C 0 1 0 1 34 Circuits Adders At each digit position add together the 2 operands and the carry-in c 0110 +0101 1011 b3 a3 b2 a2 b1 a1 b0 a0 Full c3 Adder Full c2 Adder Full c1 Adder Full c0 Adder s3 s2 s1 ‘0’ s0 Just like longhand addition except it’s in binary... BYU CS 224 S02 - Digital Logic 35 Circuits Full Adder Module Design a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 c 0 1 0 1 0 1 0 1 BYU CS 224 cyout sum 0 0 0 1 0 1 1 0 0 1 1 0 1 0 1 1 cyout a bc ab c abc abc sum a b c a bc ab c abc abc S02 - Digital Logic 36 PLAs Programmable Logic Arrays Programmable Logic Array (PLA) can be used to implement any logic function ? ? ? Outputs: ? ? Take truth table of any logic function Convert into equation (any truth table can be expressed as set of “and” expressions “or”ed together) PLA programmed by making/breaking wire connections BYU CS 224 Inputs: S02 - Digital Logic ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 37 PLAs PLA Example Out1 = ABC + ABC + ABC Out2 = ABC + ABC + ABC Out3 = ABC + ABC A B C 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 BYU CS 224 ? ? ? Out1 Out2 Out3 0 1 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 0 0 0 0 0 0 1 Out1 Out2 Out3 ? ? ? ? ? ? Outputs Inputs A B C ? S02 - Digital Logic ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 38 PLAs Exercise 2.4 Implement a half adder using a PLA sum = abc + abc + abc + abc = a b c sum ? ? ? ? a b c BYU CS 224 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? S02 - Digital Logic 39 Review Digital Components CMOS Gates Representing Logical Expressions Combinational Circuits BYU CS 224 S02 - Digital Logic 40 Sequential Logic Sequential Logic Storage Elements Everything so far has been combinational logic Computing systems need storage elements the output is strictly a function of the current inputs for holding previously computed values for saving state Two types of locks: 30 4 1 8 4 25 5 20 10 15 Combinational – Success depends only on the values, not the order in which they are set. BYU CS 224 Sequential - Success depends on the sequence of values (e.g, R-13, L-22, R-3). S02 - Digital Logic 42 Sequential Logic Bi-Stability = Key to Memory When there are 2 stable states - a bi-stable circuit 0 1 0 This is a stable state – it will sit like this forever 1 0 1 This is also a stable state – it will sit like this forever RS Latch 1 s 1 BYU CS 224 r 1 s q 0 q 1 1 r S02 - Digital Logic q 1 q 0 43 Sequential Logic RS Latch – Bi-Stable Circuit 1 s 1s q0 q1 1 r 1 r This is a stable state – it will sit like this forever 1 1 BYU CS 224 0 1 0 1 1 0 q1 q0 This is also a stable state – it will sit like this forever 1 1 1 0 S02 - Digital Logic 1 0 0 1 1 0 1 1 44 Latch Gated D Latch Output q gets value from input d only when we is high we stands for write enable, think of it as a load signal d s q we q WE D Q D-Latch r Symbols are abstractions! BYU CS 224 S02 - Digital Logic LATCH Symbol 45 Latch Register A computer register is a place to store a collection of bits we d3 d2 d1 d0 d D-Latch D-Latch D-Latch we D-Latch Register q q3 REGISTER Symbol q2 q1 q0 Very fast memory Numbered right to left (LSB on the right) BYU CS 224 S02 - Digital Logic 46 Memory Memory A collection of addressable locations Address selects which location to read from or write to A memory with n address wires has 2n locations. The number of data wires in is equal the number of data wires out. we address d Memory is changed when we is asserted. n m Memory m q q always reflects the contents stored at the addressed memory location. Memory can be viewed as a large collection of slower registers. BYU CS 224 S02 - Digital Logic 47 Memory Building a Memory From Latches writeEnable 00 2-to-4 Decoder 01 10 11 a1 a0 address n=2 BYU CS 224 we we we we d input Register Register Register Register This is a functional view. The key parts are: address decoder memory cells (registers) output selector (mux) S02 - Digital Logic q0 q1 q output q2 q3 we address d MEMORY Symbol n m Memory m q 48 Latch Exercise 2.5 Fill in the values of S, R, Q, and Q as D and CLK change. BYU CS 224 D CLK 1 0 1 1 0 0 0 1 0 0 S R Q Q 0 S02 - Digital Logic 49 Finite State Machine Turing Machine Computing Devices Alan Turing In 1936 he proposed a way to define the term “computable” The Turing Machine Basic abstract symbol-manipulating devices which can be adapted to simulate the logic of any computer algorithm. Anything that can be computed, can be computed by a TM… The TM is not a real machine, but an abstract machine BYU CS 224 S02 - Digital Logic 51 Turing Machine Turing Machine Details BYU CS 224 S02 - Digital Logic 52 Turing Machine Turing Machine Example “Action Table” Old Read State Sym S1 S2 S2 S3 S3 S4 S4 S5 S5 1 1 0 0 1 1 0 1 0 BYU CS 224 Step Write New Sym Move State 0 1 0 1 1 1 0 1 1 R R R L R L L L R S2 S2 S3 S4 S3 S4 S5 S5 S1 State 1 S1 2 S2 3 S2 4 S3 5 S4 6 S5 7 S5 8 S1 9 S2 10 S3 11 S3 12 S4 13 S4 14 S5 15 S1 --HALT-S02 - Digital Logic Tape …11000… …01000… …01000… …01000… …01010… …01010… …01010… …11010… …10010… …10010… …10010… …10011… …10011… …10011… …11011… Start State (State Register) Tape Read Head 53 Finite State Machine Sequential State Machine Another type of sequential circuit Combines combinational logic with storage “Remembers” state, and changes output (and state) based on inputs and current state State Machine Inputs Combinational Logic Circuit Outputs Storage Elements BYU CS 224 S02 - Digital Logic 54 Finite State Machine State of a System The state of a system is a snapshot of all the relevant elements of the system at the moment the snapshot is taken. Examples: The state of a basketball game can be represented by the scoreboard (ie. number of points, time remaining, possession, etc.) The state of a tic-tac-toe game can be represented by the placement of X’s and O’s on the board. BYU CS 224 S02 - Digital Logic 55 Finite State Machine State Diagram Our lock example has four different states, labeled A-D: A: The lock is not open, and no relevant operations have been performed. B: The lock is not open, and the user has completed the R-13 operation. C: The lock is not open, and the user has completed R-13, followed by L-22. D: The lock is open. 30 25 20 5 15 10 Sequential - Success depends on the sequence of values (e.g, R-13, L-22, R-3). Open = 0 State Diagram shows states and actions that cause a transition between states. Open = 0 Open = 1 BYU CS 224 S02 - Digital Logic Open = 0 56 Finite State Machine Finite State Machine A description of a system with the following components: A finite number of states A finite number of external inputs A finite number of external outputs An explicit specification of all state transitions Often described by a state diagram. Inputs trigger state transitions. Outputs are associated with each state (or with each transition). Frequently, a clock circuit triggers transition from one state to the next. "1" "0" One Cycle time At the beginning of each clock cycle, the state machine makes a transition, based on the current state and the external (or internal) inputs. BYU CS 224 S02 - Digital Logic 57 Finite State Machine FSM Implementation Combinational logic Determine outputs and next state. Storage elements Maintains state representation. State Machine Inputs Clock BYU CS 224 Combinational Logic Circuit Outputs Storage Elements S02 - Digital Logic 58 Finite State Machine Asleep or Awake? What is the output of this circuit? D Master Slave D Q D Q E Q' E Q' Q Clk 0 or 1 ??? Output Awake Asleep Asleep Awake We isolate current state from next state with a Master/Slave flip-flop. State moves thru flip-flop on each clock cycle Master captures input value when clock is LOW Slave stores Master value when clock goes HIGH BYU CS 224 S02 - Digital Logic 59 Finite State Machine Storage: Master-Slave Flipflop “1” “0” time HOLD SET/RESET Captures State Master stores input value when clock is LOW Slave BYU CS 224 Master S02 - Digital Logic 61 Finite State Machine Storage: Master-Slave Flipflop “1” “0” time HOLD SET/RESET Moves State to Slave Slave stores Master value when clock goes HIGH Slave BYU CS 224 Master S02 - Digital Logic 62 Finite State Machine Simple FSM Example Combinational Logic “1” “0” BYU CS 224 time S02 - Digital Logic 63 Finite State Machine Simple FSM Example (Lab 2) Combinational Logic Sequential Logic BYU CS 224 S02 - Digital Logic 64 Finite State Machine Storage Elements Each master-slave flip flop stores one state bit. The number of storage elements (flip flops) needed is determined by the number of states (and the representation of each state). Examples: Sequential lock 4 states – 2 bits Basketball scoreboard 7 bits for each score, 5 bits for minutes, 6 bits for seconds, 1 bit for possession arrow, 1 bit for half, … Blinking traffic sign 4 states – 2 bits BYU CS 224 S02 - Digital Logic 65 Finite State Machine Exercise 2.6 1. Design a State Diagram for a blinking traffic sign as follows: 1 2 Switch OFF 3 4 5 No lights Switch ON, repeat BYU CS 224 No lights on 1 & 2 on 1, 2, 3, & 4 on 1, 2, 3, 4, & 5 on S02 - Digital Logic 66 Finite State Machine Exercise 2.7 2. Create truth table for all values. (X=1,2 Y=3,4 Z=5) Current State Sw S1 S0 0 --- --- Next State S'1 S'0 Lights X Y X1 3 Y4 2 Z 5 1 1 S'1 = 1 S'0 = 1 X= 3. Create equations for next state and output values. BYU CS 224 S02 - Digital Logic Y= Z= 67 Z Finite State Machine Exercise 2.8 4. Implement your state machine with combinational and sequential logic. BYU CS 224 S02 - Digital Logic 68 Finite State Machine From Logic to Data Path The data path of a computer uses logic to process information. Combinational Logic Decoders -- convert instructions into control signals Multiplexers -- select inputs and outputs ALU (Arithmetic and Logic Unit) -- operations on data Sequential Logic State machine -- coordinate control signals and data movement Registers and latches -- storage elements BYU CS 224 S02 - Digital Logic 69 Finite State Machine MSP430 Finite State Machine Current State DECODE:NOCLK:MOV||EVSRC EVDST:CLK1:MOV,Rd|D,ROX=Rd|STORE EVSRC:CLK1:MOV,Rs|S,ROX=Rs|EVDST STORE:CLK1:MOV,Rd|ALU,RWE,RIX=Rd|FETCH STORE:CLK1:MOV,Rd ALU,RWE,RIX=Rd FETCH ... Action BYU CS 224 Next State S02 - Digital Logic 70 BYU CS 224 S02 - Digital Logic 71