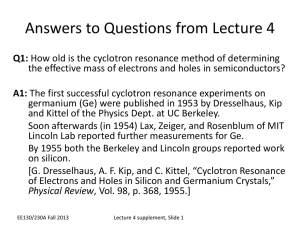

Lecture23marked

advertisement

Lecture 23 OUTLINE The MOSFET (cont’d) • Source/drain structure • CMOS fabrication process • The CMOS power crisis Reading: Pierret 19.2; Hu 6.10 Optional Reading: Pierret 4; Hu 3 Source and Drain (S/D) Structure • To minimize the short channel effect and DIBL, we want shallow (small rj) S/D regions but the parasitic resistance of these regions increases when rj is reduced. Rsource, Rdrain r / Wrj where r = resistivity of the S/D regions • Shallow S/D “extensions” may be used to effectively reduce rj with a relatively small increase in parasitic resistance EE130/230A Fall 2013 Lecture 23, Slide 2 E-Field Distribution Along the Channel • The lateral electric field peaks at the drain end of the channel. Epeak can be as high as 106 V/cm • High E-field causes problems: –Damage to oxide interface & bulk (trapped oxide charge VT shift) –substrate current due to impact ionization: EE130/230A Fall 2013 Lecture 23, Slide 3 Lightly Doped Drain (LDD) Structure • Lower pn junction doping results in lower peak E-field “Hot-carrier” effects are reduced Parasitic resistance is increased R. F. Pierret, Semiconductor Device Fundamentals, Fig. 19.9 EE130/230A Fall 2013 Lecture 23, Slide 4 Parasitic Source-Drain Resistance G RS S RD D • For short-channel MOSFET, IDsat0 VGS – VT , so that I Dsat0 I Dsat I Dsat0 Rs 1 (VGS VT ) IDsat is reduced by ~15% in a 0.1 mm MOSFET. • VDsat is increased to VDsat0 + IDsat (RS + RD) EE130/230A Fall 2013 Lecture 23, Slide 5 C. C. Hu, Modern Semiconductor Devices for Integrated Circuits, Figure 7-10 Summary: MOSFET OFF State vs. ON State • OFF state (VGS < VT): – IDS is limited by the rate at which carriers diffuse across the source pn junction – Minimum subthreshold swing S, and DIBL are issues • ON state (VGS > VT): – IDS is limited by the rate at which carriers drift across the channel – Punchthrough is of concern at high drain bias • IDsat increases rapidly with VDS – Parasitic resistances reduce drive current • source resistance RS reduces effective VGS • source & drain resistances RS & RD reduce effective VDS EE130/230A Fall 2013 Lecture 23, Slide 6 CMOS Technology Need p-type regions (for NMOS) and n-type regions (for PMOS) on the wafer surface, e.g.: (ND) n-well (NA) Single-well technology • n-well must be deep enough to avoid vertical punch-through p-substrate (NA) p-well Twin-well technology • Wells must be deep enough to avoid vertical punch-through (ND) n-well p- or n-substrate (lightly doped) EE130/230A Fall 2013 Lecture 23, Slide 7 Sub-Micron CMOS Fabrication Process p-type Silicon Substrate • A series of lithography, etch, and fill steps are used to create silicon mesas isolated by silicon-dioxide Shallow Trench Isolation (STI) - oxide p-type Silicon Substrate p-type Silicon Substrate EE130/230A Fall 2013 • Lithography and implant steps are used to form the NMOS and PMOS wells and the channel/body doping profiles Lecture 23, Slide 8 • The thin gate dielectric layer is formed p-type Silicon Substrate • Poly-Si is deposited and patterned to form gate electrodes p-type Silicon Substrate p-type Silicon Substrate EE130/230A Fall 2013 • Lithography and implantation are used to form NLDD and PLDD regions Lecture 23, Slide 9 • A series of steps is used to form the deep source / drain regions as well as body contacts p-type Silicon Substrate • A series of steps is used to encapsulate the devices and form metal interconnections between them. p-type Silicon Substrate EE130/230A Fall 2013 Lecture 23, Slide 10 CMOS Technology Advancement XTEM images with the same scale courtesy V. Moroz (Synopsys, Inc.) 90 nm node T. Ghani et al., IEDM 2003 65 nm node (after S. Tyagi et al., IEDM 2005) 45 nm node 32 nm node K. Mistry et al., IEDM 2007 P. Packan et al., IEDM 2009 • Gate length has not scaled proportionately with device pitch (0.7x per generation) in recent generations. – Transistor performance has been boosted by other means. EE130/230A Fall 2013 Lecture 23, Slide 11 Performance Boosters • Strained channel regions meff • High-k gate dielectric and metal gate electrodes Coxe Cross-sectional TEM views of Intel’s 32nm CMOS devices P. Packan et al., IEDM Technical Digest, pp. 659-662, 2009 EE130/230A Fall 2013 Lecture 23, Slide 12 Historical Voltage Scaling • Since VT cannot be scaled down aggressively, the supply voltage (VDD) has not been scaled down in proportion to the MOSFET gate length: VDD VDD – VT Source: P. Packan (Intel), 2007 IEDM Short Course EE130/230A Fall 2013 Lecture 23, Slide 13 Power Density Scaling – NOT! 1E+03 Power Density Prediction circa 2000 Power Density (W/cm2) Power Density (W/cm2) Power Density Trend Active Power Density 1E+02 1E+01 1E+00 1E-01 1E-02 1E-03 1E-04 Passive Power Density 1E-05 0.01 0.1 1 10000 Sun’s Surface 1000 Nuclear Reactor 100 8086 Hot Plate 10 4004 P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 Gate Length (μm) Year Source: S. Borkar (Intel ) Source: B. Meyerson (IBM) Semico Conf., January 2004 EE130/230A Fall 2013 Rocket Nozzle Lecture 23, Slide 14 2010 Parallelism • Computing performance is now limited by power dissipation. This has forced the move to parallelism as the principal means of increasing system performance. Energy vs. Delay per operation 100 1000 single core Sun’s Surface Rocket Nozzle Nuclear Reactor 100 Core 2 8086 Hot Plate 10 4004 P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 2010 Year Source: S. Borkar (Intel ) EE130/230A Fall 2013 Normalized Energy/op Power Density (W/cm2) 10000 80 dual core 60 Operate at a lower energy point (lower VDD) 40 20 Run in parallel to recoup performance 0 0 10 Lecture 23, Slide 15 1 10 2 3 10 10 1/throughput (ps/op) 4 10 Key to VDD Reduction: Gate Control Gate log ID Cox Cdep Source Body ION Ctotal S Cox Drain VDD VGS • The greater the capacitive coupling between Gate and channel, the better control the Gate has over the channel potential. lower VDD to achieve target ION/IOFF reduced short-channel effect (SCE) and drain-induced barrier lowering (DIBL) EE130/230A Fall 2013 Lecture 23, Slide 16 Intel Ivy Bridge Processor EE130/230A Fall 2013 Lecture 23, Slide 17