Lecture 0: Objectives, Scope, and Organization of the Course

advertisement

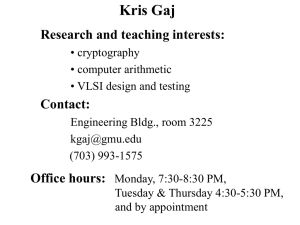

Kris Gaj

Research and teaching interests:

• cryptography

• computer arithmetic

• VLSI design and testing

Contact:

Science & Technology II, room 223

kgaj@gmu.edu

(703) 993-1575

Office hours: Monday, 6:00-7:00 PM

Tuesday, Thursday, 4:30-5:30 PM,

and by appointment

ECE 645

Part of:

MS in CpE

Digital Systems Design – pre-approved course

Other concentration areas – elective course

MS in EE

Certificate in VLSI Design/Manufacturing

PhD in ECE

PhD in IT

MS CpE: DIGITAL SYSTEMS DESIGN

Concentration advisors: Kris Gaj, David Hwang, Ken Hintz

1. ECE 545 Digital System Design with VHDL

– D. Hwang, K. Gaj, project, FPGA design with VHDL,

Aldec/Synplicity/Xilinx

2. ECE 645 Computer Arithmetic

– K. Gaj, D. Hwang, project, FPGA design with VHDL or Verilog,

Aldec/Synplicity/Xilinx

3. ECE 681 VLSI ASIC Design

– N. Klimavicz, project/lab, back-end ASIC design with

Synopsys tools

4. ECE 586 Digital Integrated Circuits

– D. Ioannou, Q. Li

Prerequisites

ECE 545 Introduction to VHDL

or

Permission of the instructor,

granted assuming that you know

VHDL or Verilog,

High level

programming

language

(preferably C)

Prerequisite knowledge

• This class assumes proficiency with the FPGA

CAD tools from ECE 545

• You are expected to be proficient with:

– Synthesizable VHDL coding

– Advanced VHDL testbenches, including file

input/output

– Xilinx FPGA synthesis and post-synthesis simulation

– Xilinx FPGA place-and-route and post-place and route

simulation

– Reading and interpreting all synthesis and

implementation reports

Course web page

ECE web page Courses Course web pages

ECE 645

http://ece.gmu.edu/coursewebpages/ECE/ECE645/S09/

Computer Arithmetic

Lecture

Homework

10 %

Midterm exam (in class)

15 %

Final Exam (in class)

25 %

Project

Project 1

20 %

Project 2

30 %

Advanced digital circuit design course covering

Efficient

• addition and subtraction

• multiplication

• division and modular reduction

• exponentiation

Integers

unsigned and signed

Real numbers

Elements

of the Galois

field GF(2n)

• fixed point

• single and double precision

floating point

• polynomial base

Course Objectives

At the end of this course you should be able to:

• Understand mathematical and gate-level algorithms for computer

addition, subtraction, multiplication, division, and exponentiation

• Understand tradeoffs involved with different arithmetic

architectures between performance, area, latency, scalability, etc.

• Synthesize and implement computer arithmetic blocks on FPGAs

• Be comfortable with different number systems, and have familiarity

with floating-point and Galois field arithmetic for future study

• Understand sources of error in computer arithmetic and basics

of error analysis

This knowledge will come about through homework, projects

and practice exams.

Lecture topics (1)

INTRODUCTION

1. Applications of computer arithmetic algorithms

2. Number representation

• Unsigned Integers

• Signed Integers

• Fixed-point real numbers

• Floating-point real numbers

• Elements of the Galois Field GF(2n)

ADDITION AND SUBTRACTION

1. Basic addition, subtraction, and counting

2. Carry-lookahead, carry-select, and hybrid adders

3. Adders based on Parallel Prefix Networks

MULTIOPERAND ADDITION

1. Carry-save adders

2. Wallace and Dadda Trees

3. Adding multiple signed numbers

MULTIPLICATION

1. Tree and array multipliers

2. Sequential multipliers

3. Multiplication of signed numbers and squaring

DIVISION

1. Basic restoring and non-restoring

sequential dividers

2. SRT and high-radix dividers

3. Array dividers

LONG INTEGER ARITHMETIC

1. Modular Exponentiation

2. Multi-Precision Arithmetic in Software

FLOATING POINT

AND

GALOIS FIELD ARITHMETIC

1. Floating-point units

2. Galois Field GF(2n) units

Possible topics for a

Scholarly Paper or Research Project

for the CpE & EE students

Advanced Computer Arithmetic

Square root

Exponential and logarithmic functions

Trigonometric functions

Hyperbolic functions

Fault-Tolerant Arithmetic

Low-Power Arithmetic

High-Throughput Arithmetic

Literature (1)

Required textbooks:

Behrooz Parhami,

Computer Arithmetic: Algorithms and Hardware Design,

Oxford University Press, 2000.

Jean-Pierre Deschamps, Gery Jean Antoine Bioul,

Gustavo D. Sutter,

Synthesis of Arithmetic Circuits: FPGA, ASIC and

Embedded Systems,

Wiley-Interscience, 2006.

Literature (2)

Recommended textbooks:

Milos D. Ercegovac and Tomas Lang

Digital Arithmetic, Morgan Kaufmann Publishers, 2004.

Isreal Koren, Computer Arithmetic Algorithms, 2nd edition,

A. K. Peters, Natick, MA, 2002.

VHDL books:

1. Volnei A. Pedroni, Circuit Design with VHDL,

The MIT Press, 2004.

2. Sundar Rajan, Essential VHDL: RTL Synthesis Done Right,

S & G Publishing, 1998.

Literature (3)

Supplementary books:

1. E. E. Swartzlander, Jr., Computer Arithmetic,

vols. I and II, IEEE Computer Society Press, 1990.

2. Alfred J. Menezes, Paul C. van Oorschot,

and Scott A. Vanstone,

Handbook of Applied Cryptology,

Chapter 14, Efficient Implementation,

CRC Press, Inc., 1998.

Literature (3)

Proceedings of conferences

ARITH - International Symposium on Computer Arithmetic

ASIL - Asilomar Conference on Signals, Systems, and Computers

ICCD - International Conference on Computer Design

CHES - Workshop on Cryptographic Hardware and

Embedded Systems

Journals and periodicals

IEEE Transactions on Computers,

in particular special issues on computer arithmetic:

8/70, 6/73, 7/77, 4/83, 8/90, 8/92, 8/94, 7/00, 3/05.

IEEE Transactions on Circuits and Systems

IEEE Transactions on Very Large Scale Integration

IEE Proceedings: Computer and Digital Techniques

Journal of VLSI Signal Processing

Homework

• reading assignments

• analysis of computer arithmetic algorithms

and implementations

• design of small hardware units using VHDL or Verilog

Midterm exams

Midterm Exam - 2 hrs 30 minutes, in class

multiple choice + short problems

Final Exam – 2 hrs 45 minutes

comprehensive

conceptual questions,

analysis and design of arithmetic units

Practice exams on the web

Tentative days of exams:

Midterm Exam - Monday, March 23

Final Exam

- Monday, May 11

Project (1)

Project I (20% of grade)

Design and comparative analysis of fast adders

(with various widths)

Optimization criteria:

• minimum latency

• maximum throughput

• minimum area

• minimum product latency · area

• maximum ratio throughput/area

• scalability

Similar for all students

Done individually

Final report due

Monday, March 16

Project (2)

Project II (30% of grade)

Long unsigned or signed integers

or

Fast

•

•

•

•

•

multiplication

squaring

division

modular reduction, or

modular exponentiation

Floating-point numbers

Fast

• addition or

• multiplication

Project II (rules)

• Real life application

• Requirements derived from the analysis of an application

• Software implementation (typically public domain)

used as a source of test vectors and to determine

HW/SW speed ratio

• Several project topics proposed on the web

You can suggest project topic by yourself

Oral presentation: Monday, May 4

Written report: Friday, May 8

Project II (rules)

• Can be done in a group of 1-3 students

• Every team works on a slightly different problem

• Project topics should be more complex for larger teams

• Cooperation (but not exchange of codes)

between teams is encouraged

Degrees of freedom and possible trade-offs

speed

area

ECE 645

power

ECE 586, 681

testability

ECE 682

Degrees of freedom and possible trade-offs

speed

latency

area

throughput

ECE 645 CAD Tool Flows

Environment

Simulation

Synthesis

Implementation

Aldec Active-HDL 7.2

SP2

Aldec Active-HDL 7.2

SP2

Synplicity Synplify Pro

8.6.2

Xilinx ISE Foundation

9.1 SP3

"

"

Xilinx XST 9.1 SP3

"

Xilinx ISE Foundation

9.1 SP3

Mentor Graphics

Modelsim SE 6.3a

Synplicity Synplify Pro

8.6.2

Xilinx ISE Foundation

9.1 SP3

"

"

Xilinx XST 9.1 SP3

"

• The above four design flows are all installed on the lab

computers in ST2 203 and ST2 265

• The two design flows using XST can also be emulated

on your laptop or home computer using the techniques

shown on the web site:

GMU FPGA CAD Tools at School and Home

How to learn VHDL for synthesis

by yourself?

• Lecture slides for ECE 545 from Fall 2005

• Sundar Rajan, Essential VHDL: RTL Synthesis Done Right,

S & G Publishing, 1998.

• Volnei A. Pedroni, Circuit Design with VHDL,

The MIT Press, 2004.

• Individual or small-group hands-on sessions with the TA

• Practice, Practice, Practice!!!

Testbench

Non-synthesizable

testbench

Synthesizable

design entity

Architecture 1

Architecture 2

....

Architecture N

Hardware Design Verification

Testbench

HDL Design

(VHDL or Verilog)

actual results

= ?

Representative

Inputs

Reference Model

(C or MAGMA )

expected results

Primary applications (1)

Execution units of general purpose microprocessors

Integer units

Floating point units

Integers

(8, 16, 32, 64 bits)

Real numbers

(32, 64 bits)

Primary applications (2)

Digital signal and digital image processing

e.g., digital filters

Discrete Fourier Transform

Discrete Hilbert Transform

General purpose

DSP processors

Specialized circuits

Real or complex numbers

(fixed-point or floating point)

Primary applications (3)

Coding

Error detection codes

Error correcting codes

Elements of

the Galois fields GF(2n)

(4-64 bits)

Secret-key (Symmetric) Cryptosystems

key of Alice and Bob - KAB

key of Alice and Bob - KAB

Network

Encryption

Alice

Decryption

Bob

Primary applications (4)

Cryptography

Secret key cryptography

IDEA, RC6, Mars

Twofish, Rijndael

Integers

(16, 32 bits)

Elements of

the Galois field GF(2n)

(4, 8 bits)

Main

operations

RC6

2 x SQR32,

2 x ROL32

MARS

MUL32,

2 x ROL32,

S-box 9x32

Twofish

96 S-box 4x4,

24 MUL GF(28)

Auxiliary

operations

XOR,

ADD/SUB32

XOR,

ADD/SUB32

XOR

ADD32

Rijndael

16 S-box 8x8

24 MUL GF(28)

XOR

Serpent

8 x 32

S-box 4x4

XOR

Public Key (Asymmetric) Cryptosystems

Private key of Bob - kB

Public key of Bob - KB

Network

Encryption

Alice

Decryption

Bob

RSA as a trap-door one-way function

PUBLIC KEY

M

C = f(M) = Me mod N

C

M = f-1(C) = Cd mod N

PRIVATE KEY

N=PQ

P, Q - large prime numbers

e d 1 mod ((P-1)(Q-1))

RSA keys

PUBLIC KEY

PRIVATE KEY

{ e, N }

{ d, P, Q }

N=PQ

P, Q - large prime numbers

e d 1 mod ((P-1)(Q-1))

Primary applications (5)

Cryptography

Public key cryptography

RSA, DSA,

Diffie-Hellman

Long integers

(1000-16,000 bits)

Elliptic Curve Cryptosystems

Elements of

the Galois field GF(2n)

(150-500 bits)

Primary applications (5)

Cipher Breaking

Public key cryptography

RSA PUBLIC KEY

RSA PRIVATE KEY

{ e, N }

{ d, P, Q }

N=PQ

P, Q

e d 1 mod ((P-1)(Q-1))