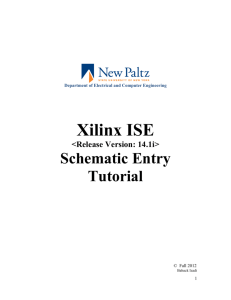

Introduction to Xilinx ISL8&11

advertisement

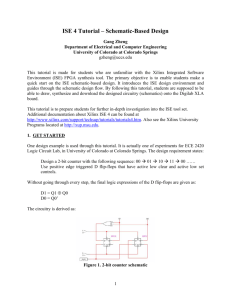

Introduction to Xilinx ISL8.1i & 11.1 Schematic Capture and VHDL 1 Using Xilinx ISE 8.1i 2 Using Xilinx ISE 8.1i 1. 2. Start/All Programs Locate Modelsim / license Wizard(Click) 3 Using Xilinx ISE 8.1i 3. Click Continue 4 Using Xilinx ISE 8.1i 4. Click OK (Window should be as shown) 5 Using Xilinx ISE 8.1i 5. Click Yes 6 Using Xilinx ISE 8.1i 6. Click OK 7 Using Xilinx ISE 8.1i 7. Click OK 8. Repeat steps 1-7 one more time. 8 Using Xilinx ISE 11.1 9 Using Xilinx ISE 11.1 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. Before beginning, license your Xilinx ISE. Double click on Xilinx ISE 11.1. Click oK on “NO license” window. Click on Help. Click on Manage license. In the XILINX_LICENSE_FILE type: 27001@ceng-licmgr.eng.unt.edu Click Set In the LM_ LICENSE_FILE type: 27000@ceng-licmgr.eng.unt.edu Click Set Click Close 10 Schematic Capture 11 New Project 1. Start Xilinx ISE 8.1i project navigator by double clicking the ISE icon on your desktop. 2. Click on File and select New project 12 Project window 3. Name your project and project location, then click next 13 New Project Wizard 4. The Spartan Starter Kit PCB board uses a Xilinx Spartan3 XCS200 FPGA chip which is packaged in a flat thin 256-pin (FT256) ball Grid Array. Set these values the new project Wizard window, 14 Create New Source 5. We will add our sources to this project later, so here we skip the following two steps (create source and add source). Click on Next. 15 Project Summary 6. Check the project summary and click Finish 16 Schematic Capture 1. Now we will create a blank sheet for schematic capture. First, click the project and new Source menu. 17 Schematic Capture 2. Click Schematic and type in the name for your schematic. Select add to project before clicking Next. 18 Schematic Capture 3. Check over the summary and click on Finish 19 Schematic Capture 4. Check over the Design Summary 20 Schematic Capture 5. Double click on CCB(CCB.CH) in the source window. You now have the schematic sheet window. Click on the hammer and the schematic window will appear. 21 Schematic Capture 6. Click on the Hammer again 22 Schematic Capture 7. Select View and click on Processes 23 Schematic Capture 8. Click on Add Symbol and locate a two input and gate (and2) 24 Schematic Capture 9. Drag the and2 gate onto the schematic sheet. Press ESC after each item. 25 Schematic Capture 10. Repeat until you have two and2, one or2 and one inv components on the schematic sheet 26 Schematic Capture 12. Click on the wiring tool and wire the schematic as shown. 27 Schematic Capture 13. Select the Add I/O Marker and connect the I/O markers as shown 28 Schematic Capture 14. Double click on each input and output and name them. 29 Schematic Capture 15. Schematic with names as shown. F8 zooms the circuit in and F7 zooms the circuit out. 30 Design Verification 31 Design Verification 1. Click on Design summary 32 Design Verification 2. Select Behavioral Simulation and double click on CCB1.sch 33 Design Verification 3. Click on Processes 34 Design Verification 4. Expand ModelSim Simulator 35 Design Verification 5. Double click on Simulate Behavioral Model 36 Design Verification 6. This is the window that appears 37 Design Verification 7. At VSIM2> type in force signal-name state-value time as shown. Enter after run will run the simulation. 38 Synthesize the Design 39 Synthesize the Design 1. Click on Xilinx-ISE to get Design Summary and select as shown by the arrows 40 Synthesize the Design 2. Click as shown by the arrow and right click and click on run. A design is produced. 41 Synthesize the Design 3. Select Project/New Source 42 Synthesize the Design 4. Click as shown, type in the File name and click on Next. 43 Synthesize the Design 5. This window appears, click on Next. 44 Synthesize the Design 6. This window appears, click on Finish 45 Synthesize the Design 7. The design summary appears, click as shown by the arrow 46 Synthesize the Design 8. 47 Synthesize the Design 9.After saving the pin arrangement, click on OK 48 Synthesize the Design 10. After the constraints file has been completed, right click on Implement Design and select Run. 49 Synthesize the Design 11. Right click on Generate Programming file and select Run 50 Synthesize the Design 12. Finally, an FPGA configuration data (*.bit) file is generated. 51 Download and Verify The Design This is the last step in the design verification process. This section provides instructions for downloading the MUX design onto the Spartan 3 PCB. 1) Connect the 5V DC power cable to the power input on the demo board (J4). (note: you may see a sequence of numbers begin to flash on the 7segment LEDs, this is just a test configuration stored in the flash memory on the PCB and you can manipulate the various switches and button, except for the PROG button, on the PCB to see the operation of the LEDs and 7-segment displays). 2) Connect the download cable between the PC parallel port and the demo board (J7). 3) Select Synthesis/Implementation from the drop-down list in the Sources window and select Mux_Schematic or Mux_vhdl (or whatever you named you design) in the Sources Window. In the Processes window, expand the Generate Programming File process and double-click the Configure Device (iMPACT) process. 52 Download and Verify The Design 1. Processes window, expand the Generate Programming File process and double-click the Configure Device (iMPACT) process. 53 Download and Verify The Design 2. iMPACT opens and the Configure Devices dialog box is displayed. In the Welcome dialog box, select Configure devices using Boundary-Scan (JTAG). Verify that Automatically connect to a cable and identify Boundary-Scan chain is selected. Click Finish. 54 Download and Verify The Design 3. When programming is complete, the Program Succeeded message is displayed. 55 Download and Verify The Design 4. Close iMPACT without saving. Your design is downloaded into the FPGA and you can begin to verify the design by manipulating swithes/buttons and observing LEDs as specified in your design. 56