LAB 1 - School of Electrical Engineering and Computer Science

advertisement

Design, Implementation, and Analysis of a Uniprocessor Embedded

System

LAB 1

CEG 4136: Computer Architecture III

TA: Daniel Shapiro

Instructor: Prof. Miodrag Bolic

Date: 2009/09/09

School of Information Technology and Engineering (SITE)

University of Ottawa

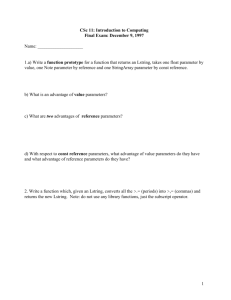

Report Requirements

1) Title Page

2) Title, Authors, Contact, Affiliation (same information as title page; Example:

http://www.doc.ic.ac.uk/~atasu/dac03-atasu.pdf)

3) 2 column format for the rest of the report. No footnotes. Don't use contractions . You

must write clearly and without spelling or grammar errors. Never use a picture from the

lab manual.

4) Abstract (no more than 100 words)

5) Introduction (State the objectives of the lab. What is the lab about (theories)? Why is the

theory needed? What will you learn (theories+practise)? What does the lab

prove(results)? Do not repeat these questions in your report. min 250 words)

6) Procedure (The procedure must be repeatable based upon the reading of your procedure

section. You need not name every menu click and mouse movement. DO NOT copy the

lab manual. Describe all parts/sections of the lab. Reference the lab manual exactly

once.)

7) Results (State the results; What did you observe? use accurate captions; include readable

graphs/charts/images of your data; analyze the results; show all calculations)

8) Discussion (discuss all relevant observations, answer all questions)

9) Conclusions and Future Work (2 paragraphs, min 3 sentences each. Future work

describes how you could expand upon the work that you have done in this lab.)

10) References (min 3 references. Refer to http://www.uottawa.ca/plagiarism.pdf

Reference format: http://www.ewh.ieee.org/reg/7/journal/authorinfo_references.html)

Include all of your code, a soft copy of the report, and readable screenshots in a zip/rar/tar.gz file. Submit

a PRINTED copy of the report to the T.A., along with a CD/usb/email of the zip/rar/tar.gz. One

submission per group.

The submitted code and reports may be subjected to automated analysis to detect plagiarism. See

http://www.uottawa.ca/plagiarism.pdf

Part I: NIOS2 with SDRAM (Based on CEG4131 Lab1)

Instructions

1) Read pages 1-10 to 1-18 of

http://www.altera.com/literature/tt/tt_nios2_hardware_tutorial.pdf

2) Next read pages 128 to 130 of http://www.altera.com/literature/hb/qts/qts_qii5v4.pdf

3) Make sure that you have "NIOS II IDE 9.0 sp2", "SOPC Builder" and "Quartus II 9.0sp2"

installed.

4) You are tired of reading. Let's do something. Specifically we will create a NIOS II

system connected to an onboard SDRAM. Run the Quartus II IDE.

5) Create a new project called "Lab1" and the top level entity called "Lab1". DO NOT

SAVE THE PROJECT TO YOUR NETWORK DRIVE (G:\ or H:\). Instead save your

project (i.e. set the working directory) to "C:\work\". Remember to backup your work

onto another drive or server before restarting or logging off the computer. Press next.

6) Press next again because we have no files to add to the project yet.

7) Set Stratix as the device family. Select the item from the available devices list that

matches the FPGA chip on your FPGA board (this number is printed on the chip and

begins with EP1S10). Press Finish.

8) CRITICAL FIRST STEP: Set the license file to C:\altera\license.dat (you will see this in

tools license setup…)

9) In Assignment SettingsDevice and pin options Unused Pins set the output pins

to “as input tri-stated” instead of “output driving ground”!

10) Create a new Block Diagram/Schematic File. Save the file as Lab1.bdf

11) Add to the design a Phase-Locked Loop component called "altpll" using the MegaWizard

plug-in. When the menu is launched select as the output format "VHDL" and press next.

The menu you see has 4 tabs: "Parameter Settings", "Output Clocks", "EDA", and

"Summary". We want 2 internal output clocks and 1 internal clock, all with an input

clock of 50MHz. Under the "General/Modes" tab of "Parameter Settings" set the inclock0

frequency to 50 MHz.

12) Next under "Scan/Inputs/Lock" uncheck "Create 'areset' input ..." and uncheck "Create

'locked' output".

13) Move to the tab "extclk e0". Check "Use this clock". Set the "Clock Phase Shift" to -3.5

nanoseconds. Press finish and then again press finish. If asked tell quartus to always add

IP files to the project.

14) Now we want to add the processor to the design. Open SOPC builder from the tools

menu. Select VHDL as the target HDL and call the system "PE0" in the system name

field.

15) On

16) the left hand side of the "System Contents" tab expand the PLL menu and double click

the "Avalon ALTPLL" entry. Notice how we could have added the altpll to the processor

block using SOPC builder. Press cancel.

17) Next under "Memories and Memory Controllers" " On-Chip" select "On-Chip

Memory (RAM or ROM)". set the memory size to 64 KBytes. Set the Block type to

MRAM.

18) Double click the "NIOS II Processor component to add it to the design. Select the Nios

II/s. Set the Reset vector and the exception vector to the onchip memory. Change

hardware multiple from “DSP blocks” to “none”. Use 2Kbytes for the instruction cache.

Press finish.

19) Ensure that the CPU is connected to the memory on the instruction bus and the data bus

as follows:

20) Add the "JTAG UART" component without changing the settings.

21) Add the "Interval Timer".

22) Rename the interval timer from timer_0 to sys_clk_timer by right clicking and pressing

rename.

23) Add the "System ID Peripheral", "PIO (Parallel I/O)", "SDRAM controller", and

"Performance Counter" components with no changes to the default settings.

24) Rename "sysid_0" to "sysid" (IMPORTANT)

25) Rename "pio_0" to "led_pio" (IMPORTANT)

26) Rename "performance_counter_0" to "performance_counter" (IMPORTANT)

27) Rename "sdram_0" to "sdram" (IMPORTANT)

28) Add an "SDRAM Controller" and set it to custom.

29) Add another "PIO" component with 4 bit width and "Direction" set as "Input ports only".

For the input options tab check the "Synchronously capture" checkbox and select the

"Either edge" option; also check the "Generate IRQ" checkbox and select the "Edge"

option.

30) Rename "pio_0" to "button_pio" (IMPORTANT)

31) Although base addresses should already be auto-assigned, go to the "System" menu and

click "Auto-Assign Base Addresses" and “auto assign IRQ”

32) Change the IRQ of "JTAG UART" from 0 to 16.

33) Now we are ready to generate the NIOS II system. The design should look as follows:

34) Switch to the "System Generation" tab and press the "Generate" button. If you are

prompted to save PE0 then do so.

35) Once system generation is complete, exit the SOPC Builder back to Quartus II.

36) Add PE0 to the design using the same method as we used to add the PLL. A shortcut is to

double click on an empty space in the drawing area. PE0 will be found in the "Project"

folder.

37) Add a Vcc.

38) Draw a wire from clock c0 to clock clk_0

39) Connect the Vcc to the reset_n port on PE0

40) Create an output pin, name it "PLD_CLKOUT", and connect it to the e0 clock of the

PLL.

41) Create an input pin, name it "PLD_CLOCKINPUT[1]", and connect it to the inclk0 of the

PLL.

42) Create an output pin, name it "LEDG[7...0]", and connect it to the

“out_port_from_led_pio[7..0]” output from the processor.

43) Right click on the PE0 component and click "Generate Pins for Symbol Ports" (AHA!)

44) Now we need to set the pin assignments for the design. either press CTRL+SHIFT+A or

navigate to "Assignments" "Assignment Editor"

45) The pin assignment information for your board can be found on the Altera website. For

example, if you are using a Stratix EP1S10 then navigate to

http://www.altera.com/literature/dp/stratix/ep1s10.pdf

46) Under the "Category" section, select "Pin"

47) Double click <<new>> under "To" to select a pin. Next select an assignment for the pin

under the location column by double clicking <<new>>. You can do this for each pin, or

you can just paste the following table into the editor to speed things up! NOTE: this step

should not take more than 60 seconds!!

For the EP1S10, these are the pin assignments:

BUTTON_PIO_IN[0]

BUTTON_PIO_IN[1]

BUTTON_PIO_IN[2]

BUTTON_PIO_IN[3]

CF_ATASEL_N

CF_CS_N

cf_ide_address[2]

cf_ide_address[3]

cf_ide_address[4]

cf_ide_address[5]

cf_ide_address[6]

cf_ide_csel

cf_ide_data[0]

cf_ide_data[1]

cf_ide_data[2]

cf_ide_data[3]

cf_ide_data[4]

cf_ide_data[5]

cf_ide_data[6]

cf_ide_data[7]

PIN_W5

PIN_W6

PIN_AB2

PIN_AB1

PIN_K7

PIN_K8

PIN_L9

PIN_J3

PIN_L10

PIN_J2

PIN_G1

PIN_K2

PIN_N3

PIN_L2

PIN_N8

PIN_M4

PIN_N6

PIN_N1

PIN_N9

PIN_P3

cf_ide_data[8]

cf_ide_data[9]

cf_ide_data[10]

cf_ide_data[11]

cf_ide_data[12]

cf_ide_data[13]

cf_ide_data[14]

cf_ide_data[15]

cf_ide_dmack_n

cf_ide_read_n

cf_ide_write_n

CF_POWER

CF_PRESENT_N

CTS[1]

CTS[2]

DCD[1]

DCD[2]

Display_7_Segment[0]

Display_7_Segment[1]

Display_7_Segment[2]

Display_7_Segment[3]

Display_7_Segment[4]

Display_7_Segment[5]

Display_7_Segment[6]

Display_7_Segment[7]

Display_7_Segment[8]

Display_7_Segment[9]

Display_7_Segment[10]

Display_7_Segment[11]

Display_7_Segment[12]

Display_7_Segment[13]

Display_7_Segment[14]

Display_7_Segment[15]

DSR[1]

DSR[2]

DTR[1]

DTR[2]

ENET_ADS_N

ENET_AEN

ENET_BE_N[0]

ENET_BE_N[1]

PIN_N10

PIN_M2

PIN_N5

PIN_M3

PIN_N7

PIN_L1

PIN_N4

PIN_L3

PIN_M6

PIN_M9

PIN_M10

PIN_H4

PIN_R3

PIN_Y27

PIN_AA27

PIN_Y25

PIN_AA26

PIN_C21

PIN_B21

PIN_A21

PIN_C20

PIN_A20

PIN_B20

PIN_B18

PIN_D21

PIN_E19

PIN_C19

PIN_B19

PIN_A19

PIN_D18

PIN_C18

PIN_A18

PIN_D19

PIN_Y26

PIN_AA25

PIN_V19

PIN_V22

PIN_V25

PIN_V28

PIN_T22

PIN_U26

ENET_BE_N[2]

ENET_BE_N[3]

ENET_CYCLE_N

ENET_DATACS_N

ENET_INTRQ[0]

ENET_IOCHRDY

ENET_IOR_N

ENET_IOW_N

ENET_LCLK

ENET_LDEV_N

ENET_RDYRTN_N

ENET_SRDY_N

ENET_VLBUS_N

ENET_W_R_N

FLASH_CS_N

FLASH_OE_N

FLASH_RW_N

FLASH_RY_BY_N

in_port_to_the_button_pio[0]

in_port_to_the_button_pio[1]

in_port_to_the_button_pio[2]

in_port_to_the_button_pio[3]

INIT_DONE

LCD[0]

LCD[1]

LCD[2]

LCD[3]

LCD[4]

LCD[5]

LCD[6]

LCD[7]

LCD_E

LCD_RS

LCD_RW

LEDG[0]

LEDG[1]

LEDG[2]

LEDG[3]

LEDG[4]

LEDG[5]

LEDG[6]

PIN_U25

PIN_T19

PIN_U27

PIN_T20

PIN_V27

PIN_V26

PIN_T23

PIN_T24

PIN_R26

PIN_T26

PIN_T28

PIN_T25

PIN_W28

PIN_T21

PIN_K19

PIN_F19

PIN_G19

PIN_L18

PIN_W5

PIN_W6

PIN_AB2

PIN_AB1

PIN_W11

PIN_H3

PIN_L7

PIN_L8

PIN_H2

PIN_H1

PIN_L6

PIN_L5

PIN_J4

PIN_K3

PIN_M7

PIN_M8

PIN_H27

PIN_H28

PIN_L23

PIN_L24

PIN_J25

PIN_J26

PIN_L20

LEDG[7]

MICTOR[0]

MICTOR[1]

MICTOR[2]

MICTOR[3]

MICTOR[4]

MICTOR[5]

MICTOR[6]

MICTOR[7]

MICTOR[8]

MICTOR[9]

MICTOR[10]

MICTOR[11]

MICTOR[12]

MICTOR[13]

MICTOR[14]

MICTOR[15]

MICTOR[16]

MICTOR[17]

MICTOR[18]

MICTOR[19]

MICTOR[20]

MICTOR[21]

MICTOR[22]

MICTOR[23]

MICTOR[24]

PLD_CLEAR_N

PLD_CLKFB

PLD_CLKOUT

PLD_CLOCKINPUT[1]

PLD_CLOCKINPUT[2]

PLD_RECONFIGREQ_N

PROTO1_CLKOUT

PROTO1_IO[16]

PROTO1_IO[19]

PROTO1_IO[22]

PROTO1_IO[23]

PROTO1_IO[28]

PROTO1_IO[40]

PROTO2_CARDSEL_N

PROTO2_CLKOUT

PIN_L19

PIN_N25

PIN_N26

PIN_L26

PIN_L25

PIN_M19

PIN_M20

PIN_K28

PIN_K27

PIN_N21

PIN_N22

PIN_M26

PIN_M25

PIN_N23

PIN_N24

PIN_L28

PIN_L27

PIN_P26

PIN_N19

PIN_N20

PIN_N28

PIN_M27

PIN_G27

PIN_G28

PIN_K21

PIN_K22

PIN_AC9

PIN_R27

PIN_E15

PIN_K17

PIN_AC17

PIN_U2

PIN_P27

PIN_L4

PIN_K1

PIN_M5

PIN_K4

PIN_J1

PIN_G2

PIN_AB18

PIN_R4

PROTO2_IO[0]

PROTO2_IO[1]

PROTO2_IO[2]

PROTO2_IO[3]

PROTO2_IO[4]

PROTO2_IO[5]

PROTO2_IO[6]

PROTO2_IO[7]

PROTO2_IO[8]

PROTO2_IO[9]

PROTO2_IO[10]

PROTO2_IO[11]

PROTO2_IO[12]

PROTO2_IO[13]

PROTO2_IO[14]

PROTO2_IO[15]

PROTO2_IO[16]

PROTO2_IO[17]

PROTO2_IO[18]

PROTO2_IO[19]

PROTO2_IO[20]

PROTO2_IO[21]

PROTO2_IO[22]

PROTO2_IO[23]

PROTO2_IO[24]

PROTO2_IO[25]

PROTO2_IO[26]

PROTO2_IO[27]

PROTO2_IO[28]

PROTO2_IO[29]

PROTO2_IO[30]

PROTO2_IO[31]

PROTO2_IO[32]

PROTO2_IO[33]

PROTO2_IO[34]

PROTO2_IO[35]

PROTO2_IO[36]

PROTO2_IO[37]

PROTO2_IO[38]

PROTO2_IO[39]

PROTO2_IO[40]

PIN_AD19

PIN_AE19

PIN_AF18

PIN_AH20

PIN_AH21

PIN_AF20

PIN_AE20

PIN_AF21

PIN_AG21

PIN_AE21

PIN_AD21

PIN_AG20

PIN_AG22

PIN_AH22

PIN_AF22

PIN_AE22

PIN_AH23

PIN_AF23

PIN_AD23

PIN_AG23

PIN_AE23

PIN_AH24

PIN_AE24

PIN_AG24

PIN_AF25

PIN_AH25

PIN_AG25

PIN_AH26

PIN_AG26

PIN_AF24

PIN_AC21

PIN_AC19

PIN_AA20

PIN_Y19

PIN_W19

PIN_W18

PIN_AA19

PIN_Y17

PIN_AB17

PIN_AB19

PIN_V18

RI[1]

RI[2]

RTS[1]

RTS[2]

RXD[1]

RXD[2]

SDRAM_A[0]

SDRAM_A[1]

SDRAM_A[2]

SDRAM_A[3]

SDRAM_A[4]

SDRAM_A[5]

SDRAM_A[6]

SDRAM_A[7]

SDRAM_A[8]

SDRAM_A[9]

SDRAM_A[10]

SDRAM_A[11]

SDRAM_BA[0]

SDRAM_BA[1]

SDRAM_CAS_N

SDRAM_CKE

SDRAM_CS_N

SDRAM_DQ[0]

SDRAM_DQ[1]

SDRAM_DQ[2]

SDRAM_DQ[3]

SDRAM_DQ[4]

SDRAM_DQ[5]

SDRAM_DQ[6]

SDRAM_DQ[7]

SDRAM_DQ[8]

SDRAM_DQ[9]

SDRAM_DQ[10]

SDRAM_DQ[11]

SDRAM_DQ[12]

SDRAM_DQ[13]

SDRAM_DQ[14]

SDRAM_DQ[15]

SDRAM_DQ[16]

SDRAM_DQ[17]

PIN_U22

PIN_V23

PIN_U23

PIN_V20

PIN_Y28

PIN_AA28

PIN_AE4

PIN_W12

PIN_AC11

PIN_W10

PIN_AA11

PIN_AC10

PIN_AB11

PIN_AC8

PIN_AB10

PIN_V11

PIN_Y11

PIN_AB7

PIN_AG19

PIN_AF19

PIN_AD18

PIN_AE18

PIN_AG18

PIN_AH4

PIN_AE5

PIN_AG3

PIN_AG5

PIN_AG4

PIN_AF4

PIN_AH5

PIN_AF5

PIN_AE6

PIN_AG6

PIN_AH6

PIN_AD6

PIN_AF7

PIN_AH7

PIN_AG7

PIN_AF6

PIN_AG8

PIN_AF8

SDRAM_DQ[18]

SDRAM_DQ[19]

SDRAM_DQ[20]

SDRAM_DQ[21]

SDRAM_DQ[22]

SDRAM_DQ[23]

SDRAM_DQ[24]

SDRAM_DQ[25]

SDRAM_DQ[26]

SDRAM_DQ[27]

SDRAM_DQ[28]

SDRAM_DQ[29]

SDRAM_DQ[30]

SDRAM_DQ[31]

SDRAM_DQM[0]

SDRAM_DQM[1]

SDRAM_DQM[2]

SDRAM_DQM[3]

SDRAM_RAS_N

SDRAM_WE_N

SHARED_A[0]

SHARED_A[1]

SHARED_A[2]

SHARED_A[3]

SHARED_A[4]

SHARED_A[5]

SHARED_A[6]

SHARED_A[7]

SHARED_A[8]

SHARED_A[9]

SHARED_A[10]

SHARED_A[11]

SHARED_A[12]

SHARED_A[13]

SHARED_A[14]

SHARED_A[15]

SHARED_A[16]

SHARED_A[17]

SHARED_A[18]

SHARED_A[19]

SHARED_A[20]

PIN_AD8

PIN_AH9

PIN_AH8

PIN_AE9

PIN_AF9

PIN_AG9

PIN_AD10

PIN_AF10

PIN_AH10

PIN_AE10

PIN_AF11

PIN_AE11

PIN_AH11

PIN_AG11

PIN_AE14

PIN_Y13

PIN_AE7

PIN_AG10

PIN_AH3

PIN_AH19

PIN_A4

PIN_A3

PIN_B3

PIN_B5

PIN_B4

PIN_C4

PIN_A5

PIN_C5

PIN_D5

PIN_E6

PIN_A6

PIN_B7

PIN_D6

PIN_A7

PIN_D7

PIN_C6

PIN_C7

PIN_B6

PIN_D8

PIN_C8

PIN_E8

SHARED_A[21]

SHARED_A[22]

SHARED_D[0]

SHARED_D[1]

SHARED_D[2]

SHARED_D[3]

SHARED_D[4]

SHARED_D[5]

SHARED_D[6]

SHARED_D[7]

SHARED_D[8]

SHARED_D[9]

SHARED_D[10]

SHARED_D[11]

SHARED_D[12]

SHARED_D[13]

SHARED_D[14]

SHARED_D[15]

SHARED_D[16]

SHARED_D[17]

SHARED_D[18]

SHARED_D[19]

SHARED_D[20]

SHARED_D[21]

SHARED_D[22]

SHARED_D[23]

SHARED_D[24]

SHARED_D[25]

SHARED_D[26]

SHARED_D[27]

SHARED_D[28]

SHARED_D[29]

SHARED_D[30]

SHARED_D[31]

SRAM_BE_N[0]

SRAM_BE_N[1]

SRAM_BE_N[2]

SRAM_BE_N[3]

SRAM_CS_N

SRAM_OE_N

SRAM_WE_N

PIN_D9

PIN_B9

PIN_H12

PIN_F12

PIN_J12

PIN_M12

PIN_H17

PIN_K18

PIN_H18

PIN_G18

PIN_B8

PIN_A8

PIN_A9

PIN_C9

PIN_E10

PIN_A10

PIN_C10

PIN_B10

PIN_A11

PIN_C11

PIN_D11

PIN_B11

PIN_D10

PIN_G10

PIN_F10

PIN_H11

PIN_G11

PIN_F8

PIN_J9

PIN_J13

PIN_L13

PIN_M11

PIN_L11

PIN_G7

PIN_M18

PIN_F17

PIN_J18

PIN_L17

PIN_B24

PIN_B26

PIN_C24

TR_CLK

TXD[1]

TXD[2]

USER_PB[0]

USER_PB[1]

USER_PB[2]

USER_PB[3]

zs_addr_from_the_sdram[0]

zs_addr_from_the_sdram[1]

zs_addr_from_the_sdram[2]

zs_addr_from_the_sdram[3]

zs_addr_from_the_sdram[4]

zs_addr_from_the_sdram[5]

zs_addr_from_the_sdram[6]

zs_addr_from_the_sdram[7]

zs_addr_from_the_sdram[8]

zs_addr_from_the_sdram[9]

zs_addr_from_the_sdram[10]

zs_addr_from_the_sdram[11]

zs_ba_from_the_sdram[0]

zs_ba_from_the_sdram[1]

zs_cas_n_from_the_sdram

zs_cke_from_the_sdram

zs_cs_n_from_the_sdram

zs_dq_to_and_from_the_sdram[0]

zs_dq_to_and_from_the_sdram[1]

zs_dq_to_and_from_the_sdram[2]

zs_dq_to_and_from_the_sdram[3]

zs_dq_to_and_from_the_sdram[4]

zs_dq_to_and_from_the_sdram[5]

zs_dq_to_and_from_the_sdram[6]

zs_dq_to_and_from_the_sdram[7]

zs_dq_to_and_from_the_sdram[8]

zs_dq_to_and_from_the_sdram[9]

zs_dq_to_and_from_the_sdram[10]

zs_dq_to_and_from_the_sdram[11]

zs_dq_to_and_from_the_sdram[12]

zs_dq_to_and_from_the_sdram[13]

zs_dq_to_and_from_the_sdram[14]

zs_dq_to_and_from_the_sdram[15]

zs_dq_to_and_from_the_sdram[16]

PIN_H26

PIN_U21

PIN_V24

PIN_W5

PIN_W6

PIN_AB2

PIN_AB1

PIN_AE4

PIN_W12

PIN_AC11

PIN_W10

PIN_AA11

PIN_AC10

PIN_AB11

PIN_AC8

PIN_AB10

PIN_V11

PIN_Y11

PIN_AB7

PIN_AG19

PIN_AF19

PIN_AD18

PIN_AE18

PIN_AG18

PIN_AH4

PIN_AE5

PIN_AG3

PIN_AG5

PIN_AG4

PIN_AF4

PIN_AH5

PIN_AF5

PIN_AE6

PIN_AG6

PIN_AH6

PIN_AD6

PIN_AF7

PIN_AH7

PIN_AG7

PIN_AF6

PIN_AG8

zs_dq_to_and_from_the_sdram[17]

zs_dq_to_and_from_the_sdram[18]

zs_dq_to_and_from_the_sdram[19]

zs_dq_to_and_from_the_sdram[20]

zs_dq_to_and_from_the_sdram[21]

zs_dq_to_and_from_the_sdram[22]

zs_dq_to_and_from_the_sdram[23]

zs_dq_to_and_from_the_sdram[24]

zs_dq_to_and_from_the_sdram[25]

zs_dq_to_and_from_the_sdram[26]

zs_dq_to_and_from_the_sdram[27]

zs_dq_to_and_from_the_sdram[28]

zs_dq_to_and_from_the_sdram[29]

zs_dq_to_and_from_the_sdram[30]

zs_dq_to_and_from_the_sdram[31]

zs_dqm_from_the_sdram[0]

zs_dqm_from_the_sdram[1]

zs_dqm_from_the_sdram[2]

zs_dqm_from_the_sdram[3]

zs_ras_n_from_the_sdram

zs_we_n_from_the_sdram

PIN_AF8

PIN_AD8

PIN_AH9

PIN_AH8

PIN_AE9

PIN_AF9

PIN_AG9

PIN_AD10

PIN_AF10

PIN_AH10

PIN_AE10

PIN_AF11

PIN_AE11

PIN_AH11

PIN_AG11

PIN_AE14

PIN_Y13

PIN_AE7

PIN_AG10

PIN_AH3

PIN_AH19

48) Compile the project by pressing CTRL+L or the purple play button. You may also

navigate to "Processing" and click "Start Compilation"

49) After the compilation completes successfully, we need to put our compiled hardware

design onto the FPGA. For this we use the Programmer tool circled in red below, and the

FPGA board of course.

50) Plug in the power for the FPGA board.

51) Connect the USB blaster cable from the computer to the FPGA. For the popup about

drivers follow the instructions at http://www.altera.com/support/software/drivers/usbblaster/dri-usb-blaster-xp.html

52) Run the Programmer

53) Click the "Hardware Setup" button and select the "USB-Blaster" hardware

54) Check the Program/Configure box

55) Press the "Start" button. Awesome, we programmed the FPGA... Now why is nothing

happening? Simple. We need to specify the software part of the system with the Nios II

IDE.

Questions

1)

2)

3)

4)

5)

6)

In the Pin Mapper GUI, what does it mean when a pin icon is coloured blue?

Why are we using FPGAs to make systems instead of microcontrollers and breadboards?

Why did we need the PLL component?

What are the output clocks of the PLL used for? Did we really need 2 output clocks?

Why is there a phase shift for the e0 clock?

Is it faster to integrate peripherals (such as a PLL) with a NIOS II embedded processor

system using the MegaWizard Plug-In Manager or the SOPC Builder?

7) Go to the menu "Processing" "Compilation Report". How many Logical Cells (LCs)

and memory bits were required to implement your entire design? How many LCs and

memory bits were needed to implement the PE0 processor (called |cpu_0:the_cpu_0|)?

What percentage of the design does the processor use in terms of memory bits and LCs?

8) A) Why does it appear in the Analysis and Synthesis report that the PLL requires 0

resources (LCs, memory bits, etc.) to implement?

B) How many LCs in the FPGA were not used for our project?

9) Open the Timing Analyzer section of the compilation report. Our frequency is currently

50 MHz. What is the execution time of the slowest component (in nanoseconds)? The

processing time required for each component is listed in the Actual Time column. We are

looking here for the bottleneck component.

10) Let us speed up the clock for the design so that the clock period is as close to the answer

from question 9 as possible. Go to "Assignments" "Settings" "Timing Analysis

Settings" "Classic Timing Analyzer Settings" "Individual Clocks" button "..."

button "List" button. Add the clock to the selected nodes list. Press OK. For required

fmax put the frequency that brings the clock period (generated immediately to the right of

the fmax box) closest to the answer from question 9. Is the fmax ≈ 63.5 MHz?

11) Set the minimum fmax to the answer from question 10. Run the classic timing analyzer.

Were there errors due to the faster clock? Hint: look at the warnings about the output

pins.

12) BONUS: If we decrease the period of in_clk (question 11) then the design might run

faster, but then doesn't the PLD_CLKOUT (i.e. e0 from the PLL) fail to control the

memory properly? Why or why not? What is the true fmax of the design? Show a

screenshot for your fmax result.

Demonstration

Show the T.A. that the project compiles without errors.

Part II: Introduction to the NIOS II IDE

Instructions

1) Open SOPC builder

2) Select the System Generator tab

3) Click the "Nios II IDE" button

4) In the Nios II IDE select "File" "New" "Project""C/C++ Application"Next

button.

5) The system description PE0.ptf is automatically filled in. The CPU defaults to cpu_0 (our

processor). Select the "Count Binary" project template and press finish.

6) Read carefully: Right click on the "count_binary_0" project folder at the left of the

screen and select system library properties. The window that opens is in fact the

count_binary_0_syslib System Library window. The System Library page contains the

settings that pertain to the hardware/software interface. The names in this page are the

same as the component names in SOPC builder.

7) There are several things we can do to improve the performance of our code. Namely,

check the boxes "Program never exits" and "Small C library", uncheck "Support C++"

and "Clean exit (flush buffers)". Change all of the memories to onchip_memory instead

of SDRAM. Click OK.

8) Press CTRL+B or click "Project" "Build All"

9) Once compilation is complete without errors, let us make a run configuration for our

system. Click "Run" "Run" "Nios II Hardware" Open the "Target Connection"

tab on the right hand side.

10) Once the hardware has been programmed into the FPGA (Part I of this lab) then right

click on the project "count_binary_0" and click "Run as" "Nios II Hardware"

11) The program is now running on the FPGA and printing to the PC console.

12) Now let us watch the code run using the debug perspective. Click "Window" "Open

Perspective" "Debug"

13) Click the green debug icon

to begin debugging the system. Remember that

you are debugging the hardware and the software at the same time.

14) Put a breakpoint on line 394 by right clicking on the gray bar on the left of the code and

selecting "Toggle Breakpoint". You can double click to get the same toggle behaviour. A

blue circle appears to signify a breakpoint.

15) Click the resume button in the debug menu bar to get the code on the processor running

again. (This is next to the stop and pause buttons)

16) Add the count variable to the list of variable names that we are watching. Change the

format of the VALUE column to decimal for the count variable.

17) Watch the changes in the value of the "count" variable. It will help you to answer

question 1.

18) Remove the breakpoint from line 394 and set a new breakpoint at line 182.

19) Press the resume button. Next press the step into button.

20) In the menus at the top of the IDE click "Window" "Show View""Disassembly"

21) This line of code (line 394) is represented in assembly by two instructions (0x02010358

<count_led+24>: ldbu r2,-32704(gp); 0x0201035c <count_led+28>: stb r2,-12(fp)).

The code clearly assigns a value. Study these assembly instructions carefully. As you step

through the code the register values will change. Looking at the board LEDs and the Nios

II IDE you should see the association between the register values and the LEDs lit up on

the board. Change the value of the registers using the debug tools. You should see the

lights on the board change. Note: make sure you move past the breakpoint using the step

button or the LEDs will not change because you are stuck at a breakpoint.

Questions

1) What is the purpose of the program "count_binary.c"? What are the buttons for, and what

are the switches for? Explain how "count" is incremented. Explain how "count" gets back

to 0x00.

2) In "count_binary.c" why do we need the method "sevenseg_set_hex( int hex )"? How

could you have implemented this functionality in hardware instead?

3) What is a JTAG UART and why do we need it in our system design?

4) What is meaning of the "alt_u8" type used in "count_binary.c" on line 182?

Demonstration

Demonstrate step 21 to the T.A.

Part III: Profiling, Speedup, and Scalability

Instructions

1) You now have the skills to design the hardware and software of an embedded system. Let

us apply your skills to a realistic problem. Create a new C/C++ application in the Nios II

IDE. For the project template select the blank template. Name the project

"performance_analysis".

2) Create a new blank C file called "performance_analysis.c".

3) Include the following libraries: "stdio.h", "string.h", "system.h", "nios2.h", "unistd.h" and

"altera_avalon_performance_counter.h"

4) Create a main function.

5) Declare three volatile integers called "x", "y", and "z"

6) Declare a two dimensional array called "image" representing the following 10 by 10

matrix:

1

2

3

4

5

6

7

8

9 10

2

3

4

5

6

7

8

9 10 9

3

4

5

6

7

8

9 10 9

8

4

5

6

7

8

9 10 9

8

7

5

6

7

8

9 10 9

8

7

6

6

7

8

9 10 9

8

7

6

5

7

8

9 10 9

8

7

6

5

4

8

9 10 9

8

7

6

5

4

3

9 10 9

8

7

6

5

4

3

2

[10 9

8

7

6

5

4

3

2

1]

7) Write a loop to nicely print the contents of the image array.

8) Declare three more two dimensional arrays called "results1", "results2", and "results3"

with sizes appropriate to the pseudocode in the next step.

9) Write a program which performs the following pseudocode program:

filter1[3][3]={ {0,1,0},{0,0,0},{0,0,0}};

filter2[3][3]={ {0,0,0},{0,0,0},{0,1,0}};

for(z = 0 ...127)

for(i=0 ...9)

{

for(j=0 ...9)

{

results1[i][j]=image[i][i]+image[j][j];

if(i>0&&j>0&&i<9&&j<9)

{

results2[i][j]=(image[(i-1)%9][(j-1)%9]*filter1[0][0]+

image[(i-1)][(j-0)]*filter1[0][1]+

image[(i-1)][(j+1)]*filter1[0][2]+

image[(i-0)][(j-1)]*filter1[1][0]+

image[(i-0)][(j-0)]*filter1[1][1]+

image[(i-0)][(j+1)]*filter1[1][2]+

image[(i+1)][(j-1)]*filter1[2][0]+

image[(i+1)][(j-0)]*filter1[2][1]+

image[(i+1)][(j+1)]*filter1[2][2]);

}

results3[i][j]+=image[i][j]&image[j][i];

}

}

10) Add a loop to print the three results matrices

11) Add the appropriate calls to the performance counter code which surround the

computation but not the array initialization or printing. We will use two counters: one to

measure the time required to perform calculations, and one to measure the overhead of

the performance counter. (http://www.altera.com/literature/hb/nios2/qts_qii55001.pdf

read pages 29-4 to 29-11)

12) Don’t forget to set the memory to onchip

13) Run project

14) Report the speed results: How many clock cycles? What is the clock rate? Therefore how

long did it take to run the program?

15) Set the memory to SDRAM in the NIOS-II IDE. SOPC builder instructions from the T.A.

may be needed here.

16) Run project

17) Measure speedup of onchip over SDRAM using execution time.

Questions

1) What is the difference between the declarations "volatile int x, y, z;" and "int x, y, z;"?

Why does this have significance for our lab?

2) What does the program do when you run it in the Nios II IDE?

3) How can we increase the speed of the program?

4) What effect did you observe comparing the initial "image" matrix with the three results

matrices.

5) BONUS: using two real 10 x 10 pixel grayscale images with colours ranging from 0

(black) to 255 (white) design a program for the Nios II which can blend the two images.