ppt - Electrical and Computer Engineering

advertisement

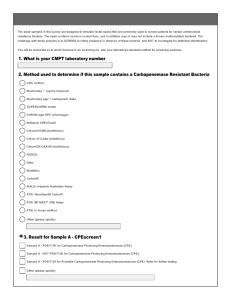

CPE/EE 421 Microcomputers: Introduction Instructor: Dr Aleksandar Milenkovic Lecture Notes CPE/EE 421 Microcomputers Syllabus Prerequisites textbook & other references grading policy important dates course outline memory organization decoding combinatorial and sequential logic important for system architecture Microcomputer Lab (EB 106) Introduction sessions Lab instructor CPE/EE 421/521 Microcomputers 2 CPE/EE 421 Microcomputers LAB Session on-line LAB manual Access cards Accounts Lab Assistant: Joel Wilder Lab sessions Lab session #1: Monday 6:00 – 8:00 PM Lab session #2: Monday 8:00 – 10:00 PM Sign-up sheet - if needed CPE/EE 421/521 Microcomputers 3 Outline Embedded systems: structure and organization Applications Technology Trends Historical perspective CPE/EE 421/521 Microcomputers 4 Microcomputers Stand alone system based on a microprocessor An embedded system – dedicated to a specific application control system/monitoring system optimization for a single function (system resources, extension, …) block diagram inputs processing outputs Number of microprocessors in our environment? CPE/EE 421/521 Microcomputers 5 A Microcontroller-Based System LCD Adj. Vol. Regul. RS232 RS232 controller Analog I/O 2-axes joystick LEDs Thermistor Keypad CPE/EE 421/521 Microcomputers Switches mC 6 Wireless Body Area Network ECG& ens ils t or PPG& m ovem ent ens s or ZigBeeor us c om t wir eles W eles ir gat eway& em t per au tr e/ hum idit ys ens or Em er gencySer v Body Ar ea N et w or k GPRS Int er net M edi cal Ser ver M ( ayoCl ni i c) M ovem ent ens s or s Per sonal Ser ver Physi ca i ns ’ Ser v CPE/EE 421/521 Microcomputers 7 Data Flow t, states A/D mP system D/A Input Processing Output Temperature sensor control signals mP INPUT PROCESSING CPE/EE 421/521 Microcomputers 78 º OUTPUT 8 Microcomputer Block Diagram CPE/EE 421/521 Microcomputers 9 Microprocessor System Architecture System Architecture System bus Single Board Computers (SBC) block diagram (modules, cards) Multibus, VME, ISA, PCI, … Multiple masters CPU Clock and CPU Control Circuits 1 MHz - 1 GHz power-up and reset circuits Address Decoder Address and Data Bus Buffers Bus Arbitration Control Memory management CPE/EE 421/521 Microcomputers 10 Microprocessor System Architecture Memory Module Virtual memory / Physical memory ROM, RAM, video memory static/dynamic Peripheral Module serial interface parallel interface RS232 (CRT, mouse), USB, Firewire (IEEE 1394) printer interface timer time/frequency measurement CPE/EE 421/521 Microcomputers 11 Microprocessor System Architecture PC architecture CPU Memory PCI ISA CPE/EE 421/521 Microcomputers 12 Von Neumann Architecture Processing Elements Read/Write Memory sequential execution linear array of fixed size cells Data and instruction store I/O unit Address/Data/Control bus CPE/EE 421/521 Microcomputers 13 Von Neumann Architecture Memory Von Neumann Architecture W bits 0 PE Read/Write Memory 1 address control data 2 (Processing Element) Control Unit ALU 3 I/O (peripherals) N log2N CPE/EE 421/521 Microcomputers 14 Von Neumann vs. Harvard Von Neumann Architecture Read/Write Memory address data PE (Processing Element) Harvard Architecture Program Memory Data Memory address data address PE (Processing Element) data CPE/EE 421/521 Microcomputers 15 Block Diagram of a Personal Computer CPE/EE 421/521 Microcomputers 16 A Typical Small Embedded System – Digital Thermometer Todd D. Morton Embedded Microcontrollers Copyright ©2001 by Prentice-Hall Inc. CPE/EE 421/521 Microcomputers 17 A Microcontroller-Based System Todd D. Morton Embedded Microcontrollers Copyright ©2001 by Prentice-Hall Inc. CPE/EE 421/521 Microcomputers 18 Computing History Eniac, 1946 PlayStation Portable (PSP) (first stored-program computer) Occupied 50x30 feet room, weighted 30 tonnes, contained 18000 electronic valves, consumed 25KW of electrical power; capable to perform 100K calc. per second Approx. 170 mm (L) x 74 mm (W) x 23 mm (D) Weight: Approx. 260 g (including battery) CPU: PSP CPU (clock frequency 1~333MHz) Main Memory: 32MB Embedded DRAM: 4MB Profile: PSP Game, UMD Audio, UMD Video CPE/EE 421/521 Microcomputers 19 Understanding computers …. User perspective Applications: What do we do with them? Price: How much do they cost? To purchase and to operate Convenience: How difficult is to use them? Designer perspective Size: How large are they? (UP) Speed: How many operations …? (UP) Power: What is energy consumed? (UP) Complexity: How complex are they to build? CPE/EE 421/521 Microcomputers 20 Engineering Computers Market Implementation Complexity Evaluate Existing Systems for Bottlenecks Applications Benchmarks Technology Trends Implement Next Generation System Simulate New Designs and Organizations Workloads CPE/EE 421/521 Microcomputers 21 Intel: First 30+ Years Intel 4004 November 15, 1971 4-bit ALU, 108 KHz, 2,300 transistors, 10-micron technology Intel Pentium 4 August 27, 2001 32-bit architecture, 1.4 GHz (now 3.08), 42M transistors (now 55+M), 0.18-micron technology (now 0.09) CPE/EE 421/521 Microcomputers 22 Technology Directions: SIA Roadmap Year Feature size (nm) Logic trans/cm2 Cost/trans (mc) #pads/chip Clock (MHz) Chip size (mm2) Wiring levels Power supply (V) High-perf pow (W) 1999 2002 2005 2008 2011 2014 180 6.2M 1.735 1867 1250 340 6-7 1.8 90 130 18M .580 2553 2100 430 7 1.5 130 100 39M .255 3492 3500 520 7-8 1.2 160 70 84M .110 4776 6000 620 8-9 0.9 170 CPE/EE 421/521 Microcomputers 50 180M .049 6532 10000 750 9 0.6 175 35 390M .022 8935 16900 900 10 0.5 183 23 Trends & Challenges Processor/memory discrepancy Microprocessor execution Fetch > Decode > Execute System on a chip - Microcontroller Memory hierarchy On-chip/off-chip memory Cost, smaller PCB, reliability, power. Applications Evolution Microprocessor Microprocessor-on-a-chip System-on-a-chip CPE/EE 421/521 Microcomputers Distributed-system-on-a-chip 24 More on Challenges Scalability Availability billions of small devices performance hardware changes system upgrade failures code enhancements Fault tolerance CPE/EE 421/521 Microcomputers 25 Performance Trends Year Proc. 1969 4004 1970’s 808x 1982 286 1985 386 1989 486 1993 Pentium 1996 P II 1999 P III 2000 P 4 MIPS 0.06 0.64 1 5 20 100 250 500 1500 1600 1400 1200 1000 800 600 400 200 0 286 386 486 Pentium P II CPE/EE 421/521 Microcomputers P III P 4 26 Performance Trends Performance 100 Supercomputers 10 Mainframes Microprocessors Minicomputers 1 0.1 1965 1970 1975 1980 1985 CPE/EE 421/521 Microcomputers 1990 1995 27 Clock Frequency Growth Rate P4 Clock rate (MHz) 1,000 100 10 R10000 Pentium100 i80386 i80286 i8086 1 i8080 i8008 i4004 0.1 1970 1980 1990 2000 1975 1985 1995 2005 • 30% per year CPE/EE 421/521 Microcomputers 28 Transistor Count Growth Rate 100,000,000 Transistors 10,000,000 R10000 Pentium i80386 i80286 R3000 R2000 1,000,000 100,000 P4 i8086 10,000 i8080 i8008 i4004 1,000 1970 1980 1990 2000 1975 1985 1995 2005 Moore’s Law CPE/EE 421/521 Microcomputers 29 General Technology Trends • • • • Microprocessor performance increases 50%-100% per year Transistor count doubles every 3 years DRAM size quadruples every 3 years Huge investment per generation is carried by huge commodity market 180 160 140 120 100 80 60 40 20 0 Integer FP Sun 4 MIPS 260 M/120 HP 9000 750 DEC Alpha IBM RS6000 MIPS 540 M2000 1987 1988 1989 1990 1991 1992 CPE/EE 421/521 Microcomputers 30 Storage Divergence between memory capacity and speed more pronounced Capacity increased by 1000x from 1980-95, speed only 2x Gigabit DRAM by c. 2000, but gap with processor speed much greater Larger memories are slower, while processors get faster Need to transfer more data in parallel Need deeper cache hierarchies How to organize caches? Speed Size Registers ns ~KB Cache 10ns ~MB Main memory 100ns ~100MB Hard disk 10ms ~10GB Archive >100ms ~TB CPE/EE 421/521 Microcomputers 31 Instruction Sets Software costs growing faster than hardware costs (1970s) CISC - Complex Instruction Set Architecture Machine language v.s. HLL Support for high-level languages Gap between high level languages and computer hardware - semantic gap Variety of instructions and addressing modes DEC VAX HLLCA - High Level Language Computer Architecture CPE/EE 421/521 Microcomputers 32 RISC Architectures Resolve problems using simpler architecture "The case for the reduced instruction set computers" Patterson & Ditzel [1980] Stanford MIPS (Hennessy, 1981) Commercial processors: MIPS R2000 (1986), IBM RS6000, SPARC, PowerPC, etc. Good design methodology Efficient pipelining and compiler-assisted scheduling of pipeline Make the Common Case Fast favor the frequent case CPE/EE 421/521 Microcomputers 33 Program Execution Time T ni CPI i Tcycle i For all instructions in the instruction set processor cycle time [s] cycles per instruction instruction count CPE/EE 421/521 Microcomputers 34 80x86 Instruction Mix for SPECint92 Programs [PatHen96] Instruction load cond. branch compare store add and sub mov reg-reg or xor, not, etc. uncond. branch call return, jmp indirect shift Frequency (%) 22 20 16 12 8 6 5 4 1 1 1 1 1 1 CPE/EE 421/521 Microcomputers 42% 70% 35 Instruction Execution A=B+C result = op1 OPERATION op2 IF ID OF A+=C ADD R1, M(1000) EX ST IF … Mem PC 1000 When f = 5MHz (’70s) When f = 1000MHz (’90s) 1000 Tcycle = 200ns Tmem = 200ns Tcycle = 1ns Tmem = 50ns … 100ns 100ns 1ns t 1ns CPE/EE 421/521 Microcomputers 3 × 100ns = 300ns 2 × 1ns = 2ns 302ns 36 Pipeline INSTR #1 IF #2 #2 ID OF EX ST IF IF ID OF EX ST IF ID OF EX IF ID OF IF ID #4 #5 program #1 if( ) … #2 #3 #4 time CPI = 1 #100 CPE/EE 421/521 Microcomputers 37