No Slide Title - North Carolina State University

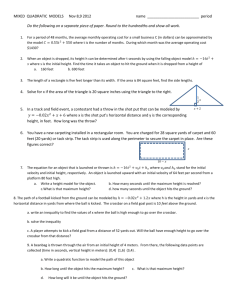

advertisement

A High-Speed & High-Capacity Single-Chip Copper Crossbar John Damiano, Bruce Duewer, Alan Glaser, Toby Schaffer,John Wilson, and Paul Franzon North Carolina State University Crossbars consist of numerous Why a Crossbar for the Copper Challenge? input and output lines with logic that can, upon programming, provide for the arbitrary and simultaneous connection of any input to any output, as shown at right. The crossbar is an essential part of many circuits requiring multi-channel signal switching, such as ATM switches, specialized VLIW video signal processors, and many DSPs. •The need for high-speed switching technology is growing as designs grow faster, especially with the advent of SOC technology. •Crossbar circuits inherently contain long, heavily-loaded interconnects and thus represent a family of designs, such as SRAM, DRAM, and cache memory. •The crossbar is simple and efficient enough to directly demonstrate the advantages offered by advanced interconnect Features of the Copper Crossbar Efficient programming - fully programmable using input / write enable lines, programming performed column-by-column. This crossbar design is non-blocking - any input can be sent to any output, and the crossbar can operate in broadcast mode. Reset - instantly writes a "0" to all cells & clears all outputs. All output lines remain low until programmed. Reset is performed prior to re-programming or pre-configuration. Pre-configure - allows instant programming for any of several common I/O configurations within a single write cycle (<3ns). Our circuit features two built-in configurations: corner turn and broadcast mode (illustrated at right). Pre-configured input/ output mappings improve testability and can be modified to fit the needs of a specific application. Pre-Configurations Cell Schematic Crossbar Cell Design The crossbar cell contains a latch used to store a memory bit (left). An I/O connection is created by writing a '1' to a single memory bit within each output column. A memory bit is programmed by holding the selected input 'high' while strobing the chosen output line's write_enable line (right). The stored memory bit is used as one input to a 2- input AND gate and therefore determines which input is passed to the output line. Crossbar cell AND outputs for a given output column are sent through an OR tree to a single output line. Crossbar Cell Layout The layout of a pair of crossbar cells is shown at right. The output of the two cells is OR'd by the top OR gate, while the bottom OR gate is made available for the OR tree configuration. The individual components of the cell are noted in and can be compared to the schematic above. Within the crossbar cell, all transistors are minimum length. The selective use of minimum-width devices reduces the capacitive load on the long input and output lines. For example, the NAND gate driven by the 2.43mm-long input line uses minimumsize 0.24mm/0.18mm NMOS and 0.36mmv/0.18mm PMOS transistors to reduce the capacitive load on this line. Alternatively, the transistors within the OR gate tree are wider to drive the long interconnect between the final OR stages. Interconnect Strategy Our interconnect strategy is illustrated at right - M3 and M5 layers are of particular interest. M3 pitch is as large as possible given the number of output interconnects required and the cell size Interconnect for the final gates in the OR tree are the longest and therefore present heavy loads. The single input line per cell was placed on M5 to minimize their resistance. Interdigitated ground lines shield the signal lines, reducing the likelihood of crosstalk and delay problems introduced by self-inductance. The capacitive load on M3 and M5 interconnect - the input and output stages respectively limits the maximum input signal frequency and has the most impact on its performance, especially for the M3 lines where line capacitance dominates load capacitance. Full Report available on the web at http://www.ece.ncsu.edu/erl/copper Title: 36pt/rev/bw .eps Creator: FreeHand 7.0 Prev iew : This EPS picture w as not s av ed w ith a preview inc luded in it. Comment: Crossbar programming