슬라이드 1

advertisement

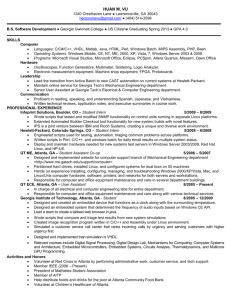

Embedded Linux PXA 255 CPU : XScale - 2-1 - Embedded Linux Target Block Diagram - 2-2 - Embedded Linux Platform Specification (1) items specification CPU Memory Intel XScale PXA255 400Mhz SDRAM Flash Intel strata Flash 32Mbyte LCD LG TFT LCD 6.4” (640×480) Touch Screen Serial 주변장치 Samsung 64Mbyte USB Ethernet ADS7846, 4 wire Touch Interface FF_UART, BT_UART USB 1.1 Slave LAN91C111 (10/100Base-T) JTAG 74LCX245 IrDA ST_UART, HDSL3600 Audio AC97 Stereo Codec, CS4202 - 2-3 - Embedded Linux Platform Specification (2) items 주변장치 specification PCMCIA 1 slot CF 1 slot RTC TEXT LCD Button LED Interface Real Time Clock Module, RTC4513 20×2 TEXT LCD Module Push Button ×8(Bus Control) Discrete LED× 8, 7Segment LED ×4 Extend connector 120 pin LCD Connector 30 pin Inverter connector 5 pin Touch connector 4 pin JTAG connector 20 pin Power connector 4 pin - 2-4 - Embedded Linux PXA 255 Processor CPU Overview • High Performance 32-bit Microprocessor, max 400MHz • Technology – 0.35um, 3 layer metal CMOS, 2.6 Million transistors – 256 PBGA package (17x17mm) • XScale core, ARMv5TE 기반 • Modified-Harvard Architecture 가 적용된 ARM 프로세서 – Separate instruction/data cache : 32Kbytes – 2Kbyte mini data/instruction cache • Instruction & data Memory Management Units (MMU) • Debug capability via JTAG port - 2-5 - Embedded Linux • • • • • • • • • • • • • • • • • • System Integration Feature Memory control Clock an power control USB client interface DMA controller LCD controller AC97(audio codec 97) I2S (Inter-IC Sound Controller) Multimedia Card Controller FIR (Fast Infrared) communication port Synchronous Serial Protocol Port I2C(Inter-Integrated Circuit) Bus Interface Unit General Purpose I/O pins (GPIO) UARTs (Universal Asynchronous Receiver/Transmitter) – Full/Bluetooth/standard/hardware Real-Time clocks OS timers PWM (Pulse Width Modulation) Interrupt Control Network Synchronous Serial Port : other ASIC interface - 2-6 - Embedded Linux Palm Size Device : System Example UART Communications TFT Color LCD Display Intel®XScale PX255 3.686MHz Portable Communications Microprocessor 32.768KHz PCMCIA Interface (Flash, Modem) Tablet/ Serial Keyboard AC97 Speaker Microphone Infrared Communications USB Synchronization Port Glue Logic SRAM Variable Latency I/O SDRAM/DRAM SMROM/ROM Flash ROM - 2-7 - Embedded Linux PXA 255 CPU Functional Block Color or Grayscale LCD Controller RTC OS Timer 0x4400_0000 PWM(2) PCMCIA & CF Control I2C AC97 FF_UART BT_UART Slow lrDA Fast lrDA SSP NSSP USB Client MMC DMA Controller and Bridge I2S Peripheral Bus General Purpose I / O Interrupt Controller Clock & Power Man. Memory Controller Socket 0, 1 System Bus Megacell Core Write Buffer Addr Dcache (32 Kbytes) Minicache IMMU Icache (32 Kbytes) SDRAM/ SMROM 4 banks Variable Latency I/O Control ASIC PC XScale Core Instructions 3.6864 MHz Osc Dynamic Memory Control Read Buffer Load/Store Data DMMU XCVR 32.768 KHz Osc CS #3,4,5 Static Memory Control ROM/ Flash SRAM 4 banks CS #0,1,2 - 2-8 - Embedded Linux Xscale Core Architecture - 2-9 - Embedded Linux ARM Core General Register & PC - 2-10 - Embedded Linux PXA 255 CPU Registers • Xscale Core(ARMv5TE ) Registers – ARM state general registers: 6 groups, 90 registers – ARM state program status registers : 6 groups, 11 registers • System Control Register for Memory Mapped registers Interface – 20 fields about 380 registers - 2-11 - Embedded Linux System Control Register • Example DMA controller - 2-12 - Embedded Linux PXA 255 Micro-Architecture IRQ FIQ CP 14 Performance Monitoring Branch Target Buffer Interrupt Trace Buffer Request CP 15 Config Registers Instruction Execution Coprocessor Interface CP0 Multiplier / Accumulator Core Data Address Data Instruction Cache 32KBytes Mini I-Cache 2 KBytes Data Cache 32 KBytes Core Memory Bus MMU MMU Write Buffer Mini D-Cache 2 KBytes JTAG Debug System Management - 2-13 - Embedded Linux XScale Core Architecture Features Instruction Cache 32 Kbytes 32 Ways Lockable by line Branch Target Buffer 128 entries Performance Monitoring Debug Hardware Breakpoints Branch History Table MicroProcessor 7 Stage pipeline Data Cache Max 32 Kbytes 32 ways WR-Back or WR-Through Hit under miss IMMU Max 28 Kbytes Re-map of data cache DMMU 32 entry TLB Fully associative Lockable by entry Power Mgnt Control Data RAM 32 entry TLB Fully associative Lockable by entry MAC Single cycle Throughput (16*32) 16-bit SIMD 40-bit accumulator Mini-Data Cache 2 Kbytes 2 ways Fill Buffer 4~8 entries Write Buffer 8 entries Full coalescing JTAG - 2-14 - Embedded Linux Arm Instruction Set Format - 2-15 - Embedded Linux PXA 255 Instruction Operation • XScale Core – – – – – 32Bit RISC 32Bit registers 32Bit instructions: Longword aligned 32Bit data paths 7~8 stage pipeline M1 Multiplier Stage1 M2 Multiplier Stage2 Mx Multiplier Stage X MAC pipeline F1 Instruction Fetch1 PC F2 Instruction Fetch2 PC - 4 ID Instruction Decode PC - 8 RF Register File Operand Shifter PC - 12 X1 ALU Execute PC - 16 X2 State Execute D1 Data Cache Access XWB Write Back D2 Data Cache Access DWB Data Cache Writeback Main execution pipeline Memory pipeline - 2-16 - Embedded Linux 0hFFFF FFFF 0hB000 0000 0hAC00 0000 0hA800 0000 0hA400 0000 0hA000 0000 0h4C00 0000 0h4800 0000 0h4400 0000 0h4000 0000 0h3000 0000 0h2000 0000 0h1800 0000 0h1400 0000 0h1000 0000 0h0C00 0000 0h0800 0000 0h0400 0000 0h0000 0000 Memory Map Reserved (1280 Mbytes) SDRAM Bank 3 (64 Mbytes) SDRAM Bank 2 (64 Mbytes) SDRAM Bank 1 (64 Mbytes) Dynamic Memory Interface 256 Mbytes SDRAM Bank 0 (64 Mbytes) Reserved (1344 Mbytes) Memory Mapped registers (Memory Control) Memory Mapped registers (LCD) Memory Mapped registers (Peripherals) PCMCIA/CF - Slot 1 (256 Mbytes) PCMCIA/CF - Slot 0 (256 Mbytes) Memory Mapped registers Interface 192 Mbytes PCMCIA Interface 512 Mbytes Reserved (128 Mbytes) Static Chip Select 5 (64 Mbytes) Static Chip Select 4 (64 Mbytes) Static Chip Select 3 (64 Mbytes) Static Chip Select 2 (64 Mbytes) Static Chip Select 1 (64 Mbytes) Static Memory Interface (ROM, Flash, SRAM) 384 Mbytes Static Chip Select 0 (64 Mbytes) - 2-17 - Embedded Linux • • • • • • • • • • • • • • PXA 255 Internal Register DMA controller UART: Full function, Bluetooth I2C I2S AC97 UDC UART: standard ICP RTC OS timer PWM0, PWM1 Interrupt Control GPIO Power Management & Reset Control • • • • • • • SSP MMC Controller Clocks Manager Network SSP Hardware UART LCD Controller Memory Controller • Total : 21 fields • about 380 registers - 2-18 - Embedded Linux PXA 255 Functional diagram L_DD(15:0) Serial Channel 0 (USB) UDCUDC+ L_FCLK Serial Channel 1 RXD_1 TXD_1 L_LCLK L_PCLK RXD_2 L_BIAS TXD_2 GP(27:0) Serial Channel 2 (IrDA) Serial Channel 3 (UART) Serial Channel 4(CODEC) Power Management TXD_3 nCAS/ DQM(3:0) nRAS/ nSDCS(3:0) TXD_C nOE RXD_C nWE RXD_3 SFRM_C nCS(5:0) SCLK_C RDY BATT_FAULT VDD_FAULT PWR_EN TCK_BYP TESTCLK PEXTAL PXTAL Clocks, Reset and Test TEXTAL TXTAL nRESET nRESET_OUT SMROM_EN ROM_SEL JTAG TCK TDI TDO TMS nTRST Intelⓡ XScale* PXA 250 [256-pins] LCD Control GPIO Ports Memory Control nSDRAS nSDCAS SDCKE<1:0> SDCLK<2:0> RD/nWR nPOE nPWE nPIOR nPIOW nPCE<2:1> PSKTSEL nPREG nPWAIT nIOIS16 A<25:0> D<31:0> VDD VDDX VSS/VSSX Transceiver Control PCMCIA Bus Signals Address Bus Data Bus Supply - 2-19 - Embedded Linux PXA 255: Memory Model MMU On-chip Caches Core Buffers Memory Memory Controller Physical Addresses Virtual Addresses Refer: http://www.intel.com/design/pca/prodbref/252780docs.htm - 2-20 - Embedded Linux PXA 255 BUS Read Operation • Cache line fills read 8 words • Read allocate • Round robin replacement Half Core Clock System Memory Core Clock D[0:31] PXA255 Instruction hit PC 32KB I- Cache Instructions & Data Memory A[0:25] D[0:31] External Bus A[0:31] Memory Controller D[0:31] A[0:31] Read Buffer A[0:31] System Bus miss I-MMU D-MMU 32 bytes 32KB D-Cache D[0:31] VA[0:31] VA[0:31] XScale Core miss Addr hit Data - 2-21 - Embedded Linux • • • • PXA 255 BUS Writes No write to I-Cache Write Back D-Cache Software coherency needed between caches Not write allocate Half Core Clock Core Clock System Memory A[0:31] A[0:25] Data D[0:31] External Bus Memory Controller A[0:31] D[0:31] System Bus PXA255 D-MMU VA[0:31] Dirty Bits Write Buffer (8 entries) XScale Core 32 bytes 32KB D-Cache Addr Data D[0:31] - 2-22 - Embedded Linux PXA 255: Instruction Cache • 32Kbytes Instruction Cache – – – – – 1,024 lines of 32 bytes(8 words) Uses the virtual address 32-way 32-set associative Round-Robin replacement Mapped via MMU page C-bits IMMU 32 Kbyte I-cache Instructions PC Main D-cache DMMU Mini-D-cache XScale Core Address Data • MMU - enable 경우: memory management table의 C-bit에 의해서 제 어 • MMU - disable 경우: 모든 address에 대하여 C=1 • C=1 or MMU - disable 경우: miss – 8word의 line fetch가 수행이 되어 round-robin replacement에 의해 서 cache bank가 대치 • MMU - enable, C=0 경우: virtual address에 해당하는 외부 메모리에서 single word를 읽어오고, cache에 쓰여지지 않음. - 2-23 - Embedded Linux PXA 255 Data Cache • 2 Data Caches: Main Data Cache, Mini Data Cache – Both: write back, read allocate, virtual – Mapped via MMU page B, C-bits • Main Data Cache: 32KB – 32-way 32-set associative – Round-Robin replacement – B=1 & C=1 IMMU 32 Kbyte I-cache Instructions PC Main D-cache DMMU • Mini Data Cache: 2KB Mini-D-cache XScale Core Address Data – 2-way set associative – Least Recently Used (LRU) replacement – B=0 & C=1 - 2-24 - Embedded Linux PXA 255 Read Buffer • PXA 255 Read Buffer Instructions I-cache PC D-cache & mini-D-cache XScale Core Address Data • Data prefetcher – saves processor waiting – load & calculate in parallel – for Read-Only data – supplements the data cache • Under software control – Coprocessor 15, register #9 Write Buffer 128 byte Read Buffer System Bus – 4 entries, 32 bytes each – Loads of 1, 4, 8 words – Replace or invalidate data - 2-25 - Embedded Linux PXA 255 Memory Management Virtual Addresses Space Physical Addresses Space PXA255 MMU System Memory ITLB 32 C A PA VA Instructions I-Cache XScale Core DTLB B C A PA VA D-Cache Data TLB Miss Descriptors Translation Table Base Register - 2-26 - Embedded Linux PXA 255 Coprocessor15 • CP15 Register transfer instructions 31 28 27 cond 2423 21 20 19 1110 000 L 1615 CRn 12 11 Rd 8 7 5 4 3 1 1 1 1 Cop2 1 0 CRm load from coprocessor/store to coprocessor MCR P15, 0, Rd, CRn, CRm, Cop2 - 2-27 - Embedded Linux PXA 255 CP15 Register structure • CP15 Register structure Register 0 1 2 3 5 6 7 8 9 10 13 14 15 4,11~12 Purpose ID Register Control Translation Table Base Domain Access Control Fault Status Fault Address Cache Operations TLB Operations Read Buffer Operations TLB lockdown Process ID Mapping Debug Support Test & Clock Control UNUSED - 2-28 - Embedded Linux PXA 255 CP15 register 31 C0 24 23 implementer 16 15 4 3 000 0000 A part number (BCD) 31 C1 revision 15 1413 12 1110 9 8 7 6 5 4 3 2 1 0 000 000 000 000 000 00 31 C2 0 RRV I Z F R S B L D P W C A M 14 13 trans lation table bas e address 0 000 0000 0000 000 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 C3 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 31 C5 9 8 7 000 0000 0000 0000 0000 000 31 0 domain 0 status 0 C6 fault address 31 C13 4 3 2524 process ID 0 0 000 000 000 000 000 000 000 000 - 2-29 - Embedded Linux Grouping of PXA 255 System Register • • • • • • • • • • • • • • • System Control: clock manager, reset/power manager (CP14) System Integration: GPIO, interrupt, RTC, OS timer, PWM DMA Controller Memory Controller LCD Controller SSPC I2C bus unit UARTs Fast Infrared communication port USB device controller AC’97 I2S Multimedia controller NSSP Hardware UART - 2-30 - Embedded Linux System Control Module of PXA 255 • Power management controller • • • • • – Supporting normal, idle and sleep modes General purpose I/O ports: 80 ports – Generate FIQ, IRQ, “wakeup” interrupts Interrupt controller – Routes all system (GPIOs, LCD, Serial Channel) interrupts to either IRQ or FIQ Multi-channel DMA controller – Software programmable to any serial port and LCD – Supporting External DMA Real time clock and timer – 32 bit counter/comparator – 32.7 kHz crystal: accuracy +/- 5 sec/month OS timer with alarm register – 32 bit counter/comparator – 3.68 MHz crystal: fine grain timing interrupts - 2-31 - Embedded Linux Running mode of PXA 255 Power on, nRESET asserted Hardware Reset nRESET asserted nRESET asserted nRESET negated nRESET asserted RUN Wait for interrupt instruction Force sleep bit set, or VDD or battery fault pins asserted GPIO or RTC System or peripheral unit alarm interrupt interrupt IDLE VDD or battery fault pins asserted CPU clock held low, all other resources active, wait for interrupt SLEEP Wait for wake-up event - 2-32 - Embedded Linux Power and Battery Faults (1) • Battery fault – Battery removed or dangerously low • Power fault – VDD is lost or out of regulation – Caused by shorted PCMCIA card • Intel® PXA255 sleep mode – During wakeup sequence if Batt_Fault or VDD_Fault asserts • Wakeup events ignore – if Batt_Fault asserted when Sleep results from a ‘fault’ state • All wakeup sources are ignored besides GPIO[0,1] - 2-33 - Embedded Linux Power and Battery Faults (2) • Idle: Low Power Modes – – – – CPU halted but MEMC and peripherals running Idle mode wakeup ~150uS Interrupt or timer expiring exit device from Idle If battery fault/power fault occur during Idle, Intel® PXA255 transitions to Sleep – No processor state lost : Program flow resumes where Idle mode was entered • Sleep: Low Power Modes – Power_EN pin negated by Intel® PXA255 to alert system to drive VDD to 0V – Sleep entered when Batt_fault, Power_fault or Sleep bit asserted – CPU, MEMC, peripherals receive no clocks • MEMC puts DRAM in self refresh state before fully entering sleep – Power consumed in Sleep < 50uA • Must disable 3.68MHz oscillator. Wakeup time ~150mS – GPIO, timer expiring, peripheral causing interrupt can start wakeup sequence - 2-34 - Embedded Linux Power and Battery Faults (3) • Sleep : Low Power Modes - 2-35 - Embedded Linux Power Manager Control Register (PMCR) • IDEA<0> (Imprecise Data Abort Enable) • 0 = nVDD_FAULT 또는 nBATT_FAULT가 나타났을 때 Sleep mode에 즉시 들어가는 것을 허용 • 1 = nVDD_FAULT 또는 nBATT_FAULT가 나타났을 때 sleep mode에 들어가는 것을소프트웨어적으로 CPU에 부정 확한 data 정지 시그널을 강제적으로 인가 • PMCR register 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Reserved IDAE - 2-36 - Embedded Linux Power Manager General Configuration Register • PCFR (Power Manager General Configuration Register) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Reserved FS FP OPDE – OPDE – FP – FS [0] [1] [2] 3.6864MHz oscillator power-down enable Float PCMCIA controls during Sleep Mode Float Static Chip Selects during Sleep Mode - 2-37 - Embedded Linux Clock 32.768K 32.768K 3.6864 3.6864 3.6864 3.6864 RTC PWR_MGR PWM SSP GPIO OST CCLKCFG cp14 c6.1 : turbo CPU OSCC, OON 10 32.768 /1 100-400 MHz /112 /N L CORE 1 0 PLL* KHz MEM 147.46 OSC CCCR Controller MHz 3.6864 /4 PLL MHz OSC /M /2 95.846 DMA / LCD MHz Bridge Controller PXbus PLL RETAINS POWER IN SLEEP USB FICP 12C MMC UARTs AC97 12S 47.923 47.923 31.949 19.169 14.746 12.288 5.672 - 2-38 - Embedded Linux L M 27 1 36 1 27 2 36 2 45 2 27 4 Core PLL Output Frequencies Turbo Mode Frequency (MHz) for Values “N” and Core Clock Configuration Register (CCCR[15:0]) Programming for Values of “N”: PXbus Frequency MEM, LCD Frequency (MHz) SDRAM max Freq 1.00 (Run) 99.5 @1.0 V 1.50 2.00 3.00 ㅡ 199.1 @1.0 V 298.6 @1.1 v 50 99.5 99.5 132.7 @1.0 V 199.1 @1.0 V 265.4 @1.1 V 331.8 @1.3 V 398.1 @1.3 V ㅡ ㅡ ㅡ 66 132.7 66 298.6 @1.1 v ㅡ 398.1 @1.3 V ㅡ 99.5 99.5 99.5 ㅡ ㅡ 132.7 132.7 66 ㅡ ㅡ ㅡ 165.9 165.9 83 ㅡ 196 99.5 99.5 ㅡ - 2-39 - Embedded Linux Core Clock Configuration Register(1) • CCCR(Core Clock Configuration Register) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 1 Reserved N M L – N[9:7] Run Mode Frequency 에서 Turbo Mode Frequency 로 변환하기 위해서 곱 하는 수, Turbo Mode Freq. = Run Mode Frequency * N 000 , 001 , 101 , 111 – Reserved 001(Multiplier) = 1 011(Multiplier) = 1.5 100 (Multiplier) = 2 110 (Multiplier) = 3 – Hardware Reset , Watchdog Reset 이 되면 010 값이 default가 된다. – Turbo Mode Freq(398.1MHz) = Run Mode Freq(199.1MHz) * N(2) - 2-40 - Embedded Linux Core Clock Configuration Register(2) • M [6:5]: Memory Frequency에서 Run Mode Frequency로 변환하기 위해서 곱 하는 수Memory Freq = Crystal Frequency * L 00 , 11 – Reserved 01(Multiplier) = 1(Multiplier가 1이면 Run Mode Freq와 Memory Frequency가 같다.) 10(Multiplier) = 2(Multiplier가 2이면 Run Mode Freq가 Memory Frequency의 2배가 된다.) • Hardware Reset , Watchdog Reset 이 되면 10 값이 default가 된다. • Memory Freq(99.5MHz) = Crystal Frequency(3.6864MHz) * L(27) 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 1 Reserved N M L - 2-41 - Embedded Linux Core Clock Configuration Register(3) • L<4:0>: Crystal Frequency에서 Memory Frequency로 변환하기위해서 곱하는 수 (3.6864MHz Crystal을 사용) 00000 , 00110 to 11111 – Reserved 00001(Multiplier) = 27 (Memory Freq는 99.53MHz가된다.) 00010(Multiplier) = 32 (Memory Freq는 117.96MHz가된다.) 00011(Multiplier) = 36 (Memory Freq는 132.71MHz가된다.) 00100(Multiplier) = 40 (Memory Freq는 147.46MHz가된다.) 00101(Multiplier) = 45 (Memory Freq는 165.89MHz가된다.) • Hardware Reset , Watchdog Reset 이 되면 00001 값이 default가 된다. 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 1 Reserved N M L - 2-42 - Embedded Linux • • • • • • • • • • • • • • • Clock Enable Register: CKEN CKEN0 [PWM0] CKEN1[PWM1] CKEN2[AC97] CKEN3[SSP] CKEN4[HWUART] CKEN5[STUART] CKEN6[FFUART] CKEN7[BTUART] CKEN8[I2S] CKEN9[NSSP] CKEN11 [USB] CKEN12 [MMC] CKEN13 [FICP] CKEN14 [I2C] CKEN15 [LCD] 31 30 29 28 27 26 25 24 23 22 21 20 * All Unit Clock Enable Bit; 0 – Clock disable 1 – Clock enable 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 111 11 0 1 111 0 1 1 1 1 Reserved C K E N 16 r e s e r v e d C C C C K K K K E E E E N N N N 14 13 12 11 r e s e r v e d C K E N 8 C K E N 7 C K E N 6 C K E N 5 r e s e r v e d C K E N 3 C K E N 2 C K E N 1 C K E N 0 - 2-43 - Embedded Linux Oscillator Configuration Register: OSCC 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 OOK • • OON Reserved OSCC는 32.768MHz Oscillator의 Configuration을 Control하는 Register이다. Oscillator가 동작되었을때 안정화가 되는데는 10초가 걸린다. Oscillator가 안정화 되면 OOK bit가 1로 set된다. OON [1] Write-once only bit 0 = 32.768MHz Oscillator 사용불가능 이때 RTC 와 Power Manager 의 Clock은3.6863MHz Oscillator의 값이 공급된다.(112로 나누어진 값) ☞ Page 3-3 의 Figure 3-1 Clocks Manager Block Diagram 참고 1 = 32.768KHz Oscillator 사용가능 이 비트는 Hardware Reset으로만 Clear가 된다. OOK [0] Read-only bit 0 = OON bit가 0 이거나 Oscillator가 안정화 되지 않았을 경우 1 = OON bit가 1 로 set 되고 Oscillator가 안정화 되었을 경우 RTC 와 Power Manager의 Clock은 32.768KHz Oscillator의 Clock을 사용 이 비트는 Hardware Reset으로만 Clear가 된다. - 2-44 - Embedded Linux General Purpose I/O • GPIO[58:73] = dual panel color or 16 bit parallel input on LCD • GPIO[23:27] = SPI if both synchronous serial protocols are required in a single system • Modem control signals for UART (CTS, RTS, CD, etc) implemented via GPIO signals • 4-5 GPIOs required for full PCMCIA support • 3 GPIOs required for Intel® SA-1111 Interface - 2-45 - Embedded Linux General Purpose I/O Block Diagram 2 GPDR 1 : 출력 0 : 입력 0 1 2 3 Alternate Function (Output) 3 2 1 0 0x40E0_000C/10/14 Alternate Function Register(GAFR) 0x40E0_0054/58/5C 0x40E0_0060/64/68 Pin Set Registers(GPSR) 0x40E0_0060/64/68 Pin Clear Registers(GPCR) 0x40E0_0060/64/68 Alternate Function (Input) Edge Detect Power Manager Sleep Wake-up logic Pin Direction Register(GPDR) Edge Detect Status Register(GEDR) Base Address 0x40E0_0000 0x40E0_0048/4C/50 Rising Edge Detect 0x40E0_0030/34/38 Enable Register(GRER) Falling Edge Detect Enable Register(GFER) 0x40E0_003C/40/44 Pin-Level Register(GPLR) 0x40E0_0000/04/08 - 2-46 - Embedded Linux Interrupt Controller Interrupt Controller 40D0 0008 40D0 0004 Level Register(ICLR) CCR[DIM]=0 & IDLE mode=‘1’ Interrupt Controller 0 : IRQ 1 : FIQ 40D0 000C 23 XScale CORE FIQ CPSR.6(F) Interrupt Controller IRQ Pending Register (ICPR) Interrupt Controller 40D0 0000 23 Mask Register (ICMR) Interrupt Source Bit 40D0 0010 All Other Qualified interrupt Bits CPSR.7(I) IRQ Pending Register (ICIP) Interrupt Controller FIQ Pending Register (ICFP) 40D0 0014 : Interrupt controller control register (ICCR) ICCR.0 : disable idle mask(DIM) - 2-47 - Embedded Linux Fault Switches • Sleep Mode Test • External Voltage Regulator Requirements PWR_EN PXA255 VDD_FAULT BATT_FAULT - 2-48 - Embedded Linux • • • • • Target Board: RESET Processor Reset Circuit MAX811T Voltage Monitor (3V~3.15 ) Manual Reset Input (Push button – “Low”) Multi-ICE Reset Reset Output to Flash JTAG PORT J20 1 3 5 7 JTAG_RST PXA255 MAX811T MR RESET_IN RESET RESET_OUT RESET RESET - 2-49 - Embedded Linux • • • • • Target Board: Flash Memory 3Volt Intel Strata Flash - 28F128 32Bit Data Bus Size : 32MByte -128Mbit (16Mbyte) * 2 EA MSC0 : Static Chip Select 0 (Bank 0) Base Address = 0x0000_0000 ADDR [10..23] DATA [0..32] D[0..15] Flash 16Bit Low PXA255 Memory Controller Interface D[16..31] OE CS0 Flash 16Bit High RESET - 2-50 - Embedded Linux • • • • • Target Board: Static RAM Samsung K6R4016V1C 3Volt High-Speed CMOS Static RAM 32Bit Data Bus / 1Mbyte MSC1: Static Chip Select 3 (Bank 3) Base Address = 0x0C00_0000 ADDR [10..23] DATA [0..32] DQM[0..1] DQM[2..3] D[0..15] SRAM 16Bit Low PXA255 Memory Controller Interface D[16..31] OE WE CS3 SRAM 16Bit High - 2-51 - Embedded Linux • • • • • • Target Board: SDRAM Samsung Synchronous DRAM - K4S561632 32Bit Data Bus 256Mbit - 4M x 16Bit x 4 Bank Size : 64MByte -256Mbit (32Mbyte) * 2 EA SDRAM Bank 0 - Dynamic Memory Base Address = 0xA000_0000 ADDR [10..24] DATA [0..32] D[0..15] DQM[0..1] DQM[2..3] SDRAM 16Bit Low PXA255 Memory Controller Interface D[16..31] RAS/CAS WE nSDCS0 SRAM 16Bit High SDCLK1/SDCKE1 - 2-52 - Embedded Linux Target Board Circuit(1) Dynamic Memory Controller PXA255 PXA250 Core SDCKE[1] SDCLK[1] SDCS[0]# SDRAS# SDCAS# WE# DQM[3:0] MDCNF MDCAS00 G MDREFR MMU TFT LCD & Touch screen D[31:0] A[31:0] LCD oller LCD Control Registers FIQ, IRQ Contr LCD CON LDD[15:0] L-FCLK L-LCLK L-PCLK L-BIAS DMA Interrupt Controller ICIP ICCR ICMR ICFP ICLR DMA Registers Bridge GPIO GPIO Registers E-PORT0 7 E-PORT0[7:0] GP[27:0] GP[27:0] GP23 E-PORT GP25 GP4 GP26 GP5 Inverter Power DCLK ADS 7 CS# DIN 843 BUSY DOUT PENIRQ# X+ XY+ Y- - 2-53 - Embedded Linux Target Board Circuit(2) PXA255 SOCKET 0 D[15:0] PCMCIA / CF D[15:0] DIR OE# SOCKET 1 D[15:0] nPOE DIR OE# nPIOR GPIO(7) CD1# CD2# CD1# CD2# GPIO(12) GPIO(11) RDY/BSY# RDY/BSY# GPIO(10) PSKTSEL MA(25:0) nPOE nPWE nPIOR nPIOW nPREG nPCE(1:2) A(25:0) OE# WE# IOR# IOW# REG# CE(1:2)# A(25:0) OE# WE# IOR# IOW# REG# CE(1:2)# nPWAIT nPIOS16 WAIT# WAIT# IOIS16# IOIS16# - 2-54 - Embedded Linux Target Board: PS2 interface • PS2 Keyboard / Mouse – – – – Holtek HT6542B 8Bit Data Bus 8MHz Operating Support PS/2 compatible mouse HT6542B PXA255 MD(31:0) D(7:0) DIR OE# DIR OE# KBCO KBCI RD_nWR KBDO KBDI HT6542_CS nCS1 nCS2 Address Decoder CS# nCS3 nCS4 MSCO MSCI DQ MA(25:0) nOE nPWE KEYBOARD RESET# A0 RD# WR# GPIO(19) KB_INT GPIO(9) MS_INT MSDO MSDI MOUSE - 2-55 - Embedded Linux Target Board: Audio Codec • Audio Codec – Cirrus Logic CS4202 – – – – AC’97 2.2 Compliant 20-bit Stereo D/A Converters 18-bit Stereo A/D Converters MIC Input / Headphone Output AC’97 Primary CODEC nACRESET PXA255 AC’97 Controller Unit (ACUNIT) SDATA_OUT SYNC(48 kHz) SDATA_IN_0 CS4202 BITCLK(12.288MHz - 2-56 - Embedded Linux Hardware overview Serial / USB Port PXA255 PXA255 Core MMU RS-232 FTUART,BTUART D[31:0] A[31:0] Bridge UTCR0 DTDR UTCR1 UTSR0 UTCR2 UTSR1 UTCR3 TX1 RX1 DB9 TX3 RX3 DMA DMA Registers FIQ, IRQ Interrupt Controller FIQ, IRQ ICIP ICCR ICMR ICFP ICLR Memory Controller Memory Control Registers USB UDCCR UDCCS2 UDCAR UDCD0 UDCOMPUDCWC UDCIMP UDCD UDCCS0 R UDCSR UDCCS1 D+ D- 27.4 R 1.5K R 473K R R R USB CON - 2-57 - Embedded Linux • • • • • • Target Board: Ethernet LAN SMSC 10/100 Ethernet Single Chip LAN91C111 Internal 32bit Wide Data Path 8Kbytes Internal Memory (Receive and Transmit FIFO Buffers) External 25MHz-output pin for an external PHY and MAC MSC0, 1 : Static Chip Select 1,2 (Bank 1,2) Base Address = 0x04000_0000 (primary) 0x0800_0000(secondary) PXA255 Primary Ethernet Secondary Ethernet MD(31:0) nCS1 nCS2 nCS3 nCS4 RD_nWR nPWE nOE MA(25:0) nDQM(3:0) GPIO(0) GPIO(1) D(31:0) D(31:0) DIR OE# T/F Logic nCS1 nCS2 ADDR (15:2) WE# OE# A(15:2) DQM(3:0)# WE# OE# A(15:2) DQM(3:0)# INTR0 T/F INTR0 - 2-58 - Embedded Linux Target Board: Push Switch • 8bit Read [D0~D7] • Base Address = 0x1050_0000 +3.3V PXA255 MD(7:0) Memory Controller Address Decoder B U F F E R G MA(22:20) CS4 - 2-59 - Embedded Linux Target Board: Discrete LED • 8Bit Write [ D0~D7 ] • Base Address = 0x1060_0000 PXA255 MD(7:0) Memory Controller B U F F E R Address Decoder CK MA(22:20) CS4 - 2-60 - Embedded Linux Target Board: 7 Segment LED • 16Bit Write [ D0~D7 ] • Base Address = 0x1030_0000 [ Low 2 Segment ] 0x1040_0000 [ High 2 Segment ] PXA255 MD(15:0) CK Memory Controller Address Decoder L A T C H DQ(7:0) L A T C H DQ(7:0) DQ(15:8) DQ(15:8) CK MA(22:20) CS4 - 2-61 - Embedded Linux • • • • Target Board: Text LCD 8Bit Data Write [ D0~D7 ] 3Bit Control Write [ D8~D10] Base Address = 0x1060_0000 20 Characters x 2 Lines / Backlight Type +5V Character LCD Module VD PXA255 L A T C H MD(15:0) Memory Controller L A T C H Address Decoder DQ(7:0) DQ(8) DQ(9) DQ(10) D(7:0) RS RW E CK MA(22:20) CS4 - 2-62 -