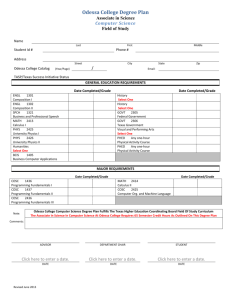

Input/ Output

advertisement

COSC 3P92 Cosc 3P92 Week 11 Lecture slides Violence is the last refuge of the incompetent. Isaac Asimov, Salvor Hardin in "Foundation" 1 COSC 3P92 Input/ Output • There are two general types of I/O devices: 1. physical I/O devices eg. output port to printer 2. virtual (logical) I/O devices: operating system abstractions eg. spooled print file, files vs. sectors on disk » Telephony Application Programmed Interface (TAPI) » Telephony Service Provider Programming Interface (TSPI) Physical I/O • To transfer information between CPU and physical I/O devices, one may use the following techniques: 1. programmed I/O 2. interrupt (-driven) I/O 3. direct memory access (DMA) 2 COSC 3P92 1. Programmed I/O • I/O ports may be addressed using: 1. standard (isolated) I/O address space – eg. Intel – In and OUT instructions – pin on CPU chip indicates whether IO or memory address space being used. [See next slide] 2. memory-mapped I/O address space – eg. Motorola – devices reside at specific memory locations. 3 COSC 3P92 8088 i/o port control 4 COSC 3P92 1. Programmed I/O • Advantages Memory-mapped I/O: – – – – no special I/O opcodes all instns that reference memory can access IO # I/O ports is unlimited hardware bus simplified • Disadvantages: – I/O interfaces may need more circuitry to recognize larger addresses. – possible slow down in bus performance. 5 COSC 3P92 • An I/O operation may be performed: 1. unconditionally – CPU sends data to device at any time 2. conditionally – checking the status of the device before the operation (i.e. handshaking). – CPU may have to poll and wait for device -> inefficient • The CPU communicates with an I/O devices via one or more registers called I/O ports. – Bit-serial ports » Every bit in the port may be configured as either input or output. Data-direction register 0 1 1 0 0 1 1 0 1=output 0=input I/O port 6 COSC 3P92 – Parallel ports » Each I/O port (as a whole) may be configured as either input or output. Command register 0 1 1 0 0 Other control signals 1 1 B 0 A 1=output 0=input I/O port A (output) I/O port B (input) 7 COSC 3P92 Interrupt I/O • When an I/O device is ready to send (receive) data to (from) the CPU, it signals (or interrupts) the CPU for its attention. – No need to poll device status. – As soon as the CPU finishes the current instruction, it transfers its execution to an interrupt-service routine which responds to the external interrupt. Current execution path Interrupted Interrupt occurs Interrupt-service routine perform I/O transfer Resume Return from interrupt • Q. How does the CPU know which one of the ISRs to execute when there is more than one? – Interrupt Service Vectors: address of interrupt service routines, commonly kept in special jump table. 8 COSC 3P92 Interrupt I/O example code: Setting up interrupt I/O... move.b move.b move.b move.b #$81, #$00, #$81, #$01, DDRA DDRB PORTA PORTA ; data direction ; registers ; start pulse ; to device ... Device will cause interrupt when ready/done, and an interrupt routine will complete transaction... move.b PORTB, D1 ; interrupt service rtn. rte 9 COSC 3P92 Interrupt I/O (continued) • Polled • Daisy-chain 10 COSC 3P92 Direct Memory Access (DMA) • It is a technique of transferring data between memory and I/O devices without CPU intervention. – CPU sets up transfer with DMA controller; then transaction occurs without CPU 11 COSC 3P92 Direct Memory Access (DMA) 12 COSC 3P92 DMA 3 techniques: 1. Block transfer - whole data block transferred - CPU can do non-related bus activities in the meanwhile 2. Cycle stealing - DMA controller freezes the CPU, and then does a DMA while CPU frozen - word-by-word transfer 3. Interleaved - DMA controller uses CPU cycles that aren't using the bus, letting DMA xfers and CPU alternate use of the bus 13 COSC 3P92 I/O Processor (data channel) • Independent dedicated I/O processors (smart DMA controllers) are used in mainframe computer systems to communicate with I/O devices. 14 COSC 3P92 I/O processors • Each IOP uses DMA to communicate with devices • Some considerations: – priority system for IOP's sharing system bus – priority system for devices on one IO bus – IOP requires software or hardware to manage different devices 15 COSC 3P92 IO example: LED • Encoder, part of kbd. – Converts key press into ASCII encoded byte. – Bus Interface communicates data to I/O bus. 16 COSC 3P92 8086 Programmed IO 17 COSC 3P92 8086 Programmed IO 18 COSC 3P92 68000 IO 20 COSC 3P92 68000 IO 21 COSC 3P92 68000 memory 22 COSC 3P92 The end 26