Synchronisation Primitives

advertisement

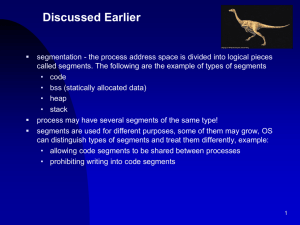

Operating Systems: Paging/2 Examples of Paging Architectures • Manchester University/Ferranti ATLAS (1962) – concept of Virtual Memory invented in Manchester for the Atlas » first paging hardware and demand paging operating system » 20 bit virtual address : 11 bits 9 bits – virtual address space 1M 48-bit words » 2048 pages each of 512 words » much larger than available magnetic core memory sizes of the day » typical machine had 32k words » only a handful built – very expensive! – first computing done by Edinburgh University used Manchester Atlas » via punched paper tape and GPO land line » Flexowriter to prepare tapes and print results - three for the whole university! » remote multi-programming batch system - before the days of interactive computing 1 Operating Systems: Paging/2 • Digital Equipment Corp. VAX 11/780 – one of the first 32-bit mini-computers – based on PDP-11 but with a novel two-level paging scheme – DCS had one all through 1980s – Virtual address : 2 21 9 virtual page number – 221 512 byte pages in each region offset 00 : User program and data (P0) 01 : User stack (P1) 10 : System space 11 : Reserved » too small in practice – grouped together to form larger contiguous clumps – Virtual space : P0 Region grows P1 Region grows System Region grows unused – stacks grow downwards 2 Operating Systems: Paging/2 – one system area shared between all virtual spaces Process A P0 P1 Process B P0 P1 System Process C P0 P1 Process D P0 P1 – the same page table used for all pages in the system area – system calls fast and efficient » no context switching between virtual spaces required – User space page tables held in System Virtual Space » separate page tables for P0 and P1 » paged in and out of physical memory by demand paging in system space 3 Operating Systems: Paging/2 – page table entry format : 31 30 P prot 27 26 D 20 0 page-frame number – protection field » K : Kernel : memory management, scheduling, I/O drivers etc. » E : Executive : system calls e.g. to file system » S : Supervisor : command interpreter etc. » U : User : editors, compilers user programs etc. – not enough bits in prot field for all combinations of rings of protection – no referenced bit – problem for page replacement? - use guard pages! 4 Operating Systems: Paging/2 – Translation of System Space Addresses : – uses conventional single level page table in physical memory » using a System Base Register (SBR) for page table base address » and a System Length Register (SLR) for page table length 5 Operating Systems: Paging/2 – Translation of P0 region - two level page table : » P0 Base Register (P0BR) contains base address of P0 page table in system space – first level translation produces a virtual address of the desired page table entry – second level translation uses system space translation mechanism – page containing this address i.e. P0 page table, may need to be demand paged 6 Operating Systems: Paging/2 – Translation of P1 addresses – almost same as P0 addresses : » P1 Base Register (P1BR) contains base address of P1 page table – P1 space used for stack and grows downwards from top » P1 page table used from top down also + length check from top end » P1BR contents could just be in P1 space, as long as part of page table in use is still in System space 7 Operating Systems: Paging/2 • Sun SPARC – 32 bit virtual address translated to 36 bit physical address – three level page tables – additional prior context table indexed by process ID : – page tables are 256, 64 and 64 entries long – 4Kb pages 8 Operating Systems: Paging/2 – page table entry for intermediate page tables : page table pointer ET = 1 – page table entry for final page table : PPN C M R ACC ET = 2 » PPN : physical page-frame number » C : cacheable » M : modified » R : referenced » ACC : access protection – chain of page tables terminates when ET = 2 » not all levels need to be used – ET = 0 : not present 9 Operating Systems: Paging/2 • Motorola 68030 – up to four levels of page tables, each size programmable – page size also programmable from 256 bytes to 32Kb – top n bits of virtual address can be ignored – Virtual address : – partition sizes (and page table sizes) controlled by translation control register : 10 Operating Systems: Paging/2 – subject to the constraints : – e.g. 11 Operating Systems: Paging/2 12 Operating Systems: Paging/2 – an escape mechanism included for specified virtual addresses » to inhibit any translation to physical addresses » useful for memory-mapped I/O devices - or anything else that needs physical addresses 13 Operating Systems: Paging/2 • IBM System 38 and Power PC – inverted page tables – 39 bit page address – 9 bit offset 14 Operating Systems: Paging/2 • MIPS – Zero level paging – TLB large enough to hold all (or most) translations a process will need – page tables just used by software » rarely need to be consulted if TLB large enough – a TLB miss causes an interrupt to kernel » equivalent to a page-fault interrupt » kernel consults page tables and inserts the translation into the TLB – very effective if TLB large enough to have a very high hit ratio – e.g. MIPS model R2000 had an associative TLB with 64 entries : 15 Operating Systems: Paging/2 • Zero level paging with LRU – an unimplemented variant of MIPS which helps with page replacement – an Associative Stack TLB » when a match is made in a position, that entry goes to the top of the TLB » everything above it shifted down one place to make room virtual page number page-frame number matching entry » in effect a cyclic shift down as far as the matching entry – new entries in the TLB are pushed down on the top » least recently used entry is pushed out of the bottom » kernel can remove this LRU page in its page replacement scheme 16 Operating Systems: Paging/2 Comparison : Segmentation versus Paging Segmentation Paging logical division of address space for purposes of program modularity physical division of address space for efficiency of memory usage and to implement a 1-level store i.e. demand paging variable size, depending on the size of module fixed size, though may selected by the OS in some architectures address calculations should ideally not overflow from the end of one segment to the beginning of the next address calculations should overflow from the end of a page to the beginning of the next 17 Operating Systems: Paging/2 Combined Segmentation and Paging – complementary schemes, many architectures have both – virtual address partitioned : segment number page number within segment page offset 18 Operating Systems: Paging/2 • Benefits : – best of both worlds? – segments give modularity, variable size (in pages), separate protection – pages give memory efficiency and ease of memory management – address overflow: » segments may or may not overflow, depending on architecture » pages do overflow, as desired – segments can easily be shared » segment table entries in different processes point to same page table » shared segments can be in different segments in each process • Disadvantage of sharing segments by using common page tables: – page usage information (referenced bits) recorded in page table entries – therefore cannot tell which process accessed which pages – cannot use a process local page replacement scheme » EMAS had to use separate page tables for shared modules » page tables mapped into each process virtual space and swapped in and out with the process (entries updated with new page-frame numbers as necessary) 19 Operating Systems: Paging/2 Examples of Segmented and Paged Architectures • English Electric Computers (later ICL) System 4-75 – clone of IBM 360 – first version of EMAS implemented : 2Mhz + 1Mb = 50 simultaneous users! – 24 bit virtual address : 8 4 12 segment page offset – 256 segments of 16 pages, each 4Kb – addresses overflowed between segments and between pages • IBM 370 – 32 bit virtual address : 12 or 16 segment 11 or 12 page offset – various combinations used in different OSes : » VM370 : 64Kb segments + 4Kb pages » DOS/VS : 64Kb segments + 2K pages » TSS : 1Mb segments + 4Kb pages 20 Operating Systems: Paging/2 • ICL 2900 – architecture developed in Manchester University – commercialised by ICL – 32 bit virtual address : 1 13 segment 8 10 page offset – top bit selects user space or system space » system space common to all virtual spaces » like DEC VAX – each page table entry 4 bytes, so a page table occupied one page – 1Kb pages too small, so (soft) grouped into contiguous 4Kb groups for paging – address overflow between segments still – Access Protection Field (APF) of a segments table entry : 1 4 4 E W R » 16 levels of Read and Write plus 1 of Execute » rings of protection using Access Control Register (ACR) » access to segment only allowed if ACR APF.W or R » E bit set together with R to allow execution 21 Operating Systems: Paging/2 • Intel Pentium – in addition to segmentation, Pentium has the option of paging – the 32 bit linear address produced from segmentation translation is further translated to a physical address using page tables – various different modes of operation available : » 32 bit physical addresses with 4Kb or 4Mb pages » 36 bit physical addresses with 4Kb or 2Mb pages (Pentium Pro onwards) – for 32 bit physical addresses & 4Kb pages – two level page tables : 22 Operating Systems: Paging/2 23 Operating Systems: Paging/2 – for 32 bit physical addresses & 4Mb pages – one level page table : 24 Operating Systems: Paging/2 – for 36 bit physical addresses & 4Kb pages – three level page tables : 25 Operating Systems: Paging/2 – 36 physical addresses and 2Mb pages – two-level page tables : 26 Operating Systems: Paging/2 – overall segmentation and paging scheme : 27