Analog to Digital Conversion

advertisement

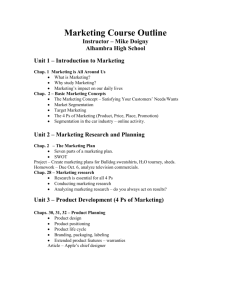

Analog to Digital Conversion ADC Essentials A/D Conversion Techniques Interfacing the ADC to the IBM PC DAS (Data Acquisition Systems) How to select and use an ADC A low cost DAS for the IBM PC 1 Why ADC ? Digital Signal Processing is more popular Easy to implement, modify, … Low cost Data from real world are typically Analog Needs conversion system from raw measurements to digital data Consists of Amplifier, Filters Sample and Hold Circuit, Multiplexer ADC Chap 0 2 ADC Essentials Basic I/O Relationship ADC is Rationing System x = Analog input / Reference n bits ADC Number of discrete output level : 2n Quantum LSB size Q = LSB = FS / 2n Quantization Error 1/2 LSB Reduced by increasing n • Fraction: 0 ~ 1 Chap 0 3 Converter Errors Offset Error Integral Linearity Error Gain Error Differential Linearity Error Can be eliminated by initial adjustments Nonlinear Error Chap 0 Hard to remove 4 Terminologies Chap 0 Converter Resolution The smallest change required in the analog input of an ADC to change its output code by one level Converter Accuracy The difference between the actual input voltage and the full-scale weighted equivalent of the binary output code Maximum sum of all converter errors including quantization error Conversion Time Required time (tc) before the converter can provide valid output data Converter Throughput Rate The number of times the input signal can be sampled maintaining full accuracy Inverse of the total time required for one successful conversion Inverse of Conversion time if No S/H(Sample and Hold) circuit is used 5 More on Conversion Time Input voltage change during the conversion process introduces an undesirable uncertainty Full conversion accuracy is realized only if this uncertainty is kept low below the converter’s resolution Example 8-bit ADC Conversion Time: 100sec Sinusoidal input vi A sin(2 ft ) dvi 2 fA cos(2 ft ) 2 fA dt of Change x tc resolution f 2A 2 n tc 1 2 tc n 12.4 Hz Limited to Low frequency of 12.4 Hz Chap 0 Let FS = 2A 2 fA Rate dV FS ( ) max dt 2 n tc Rate of change Few Applications 6 S/H increase Performance S/H (Sample and Hold) Analog circuits that quickly samples the input signal on command and then holds it relatively constant while the ADC performs conversion Aperture time (ta) Chap 0 Time delay occurs in S/H circuits between the time the hold command is received and the instant the actual transition to the hold mode takes Example 20 nsec aperture time f 1 2 ta n 62.17 KHz Reasonably good for 100sec converter 7 Analog Input Signal Typically, Differential or Single-ended input signal of a single polarity Typical Input Range 0 ~ 10V and 0 ~ 5V Actual input signal does not span Full Input range Matching input signal and input range Prescaling input signal using OP Amp If Chap 0 Some of the converter output code never used Waste of converter dynamic range Greater relative effects of the converter errors on output In a final stage of preconditioning circuit By proportionally scaling down the reference signal If reference signal is adjustable 8 Converting bipolar to unipolar Using unipolar converter when input signal is bipolar Scaling down the input Adding an offset Input signal is scaled and an offset is added Add offset scaled Bipolar Converter If polarity information in output is desired Bipolar input range Chap 0 Typically, 0 ~ 5V Bipolar Output 2’s Complement Offset Binary Sign Magnitude 9 Outputs and Analog Reference Signal I/O of typical ADC Errors in reference signal From Initial Adjustment Drift with time and temperature Cause Gain error in Transfer characteristics ADC output Number of bits 8 and 12 bits are typical 10, 14, 16 bits also available Typically natural binary Chap 0 BCD (3½ BCD) • For digital panel meter, To realize full accuracy of ADC Precise and stable reference is crucial Typically, precision IC voltage reference is used • 5ppm/C ~ 100ppm/C 10 Control Signals Start From CPU Initiate the conversion process HBE / LBE From CPU To read Output word after EOC • High Byte Enable BUSY / EOC To CPU Conversion is in progress HBE LBE • Low Byte Enable 0=Busy: In progress 1=EOC: End of Conversion Chap 0 11 A/D Conversion Techniques Counter or Tracking ADC Successive Approximation ADC Most Dual Slop Integrating ADC Voltage to Frequency ADC Parallel or Flash ADC Fast Chap 0 Commonly Used Conversion Software Implementation Shaft Encoder 12 Counter Type ADC Block diagram Operation Reset and Start Counter DAC convert Digital output of Counter to Analog signal Compare Analog input and Output of DAC Vi < VDAC • Continue counting • Stop counting Waveform Digital Output = Output of Counter Disadvantage Conversion time is varied Chap 0 Vi = VDAC 2n Clock Period for Full Scale input 13 Tracking Type ADC Tracking or Servo Type Using Up/Down Counter to track input signal continuously Chap 0 For slow varying input Can be used as S/H circuit By stopping desired instant Digital Output Long Hold Time Disabling UP (Down) control, Converter generate Minimum (Maximum) value reached by input signal over a given period 14 Successive Approximation ADC Chap 0 Most Commonly used in medium to high speed Converters Based on approximating the input signal with binary code and then successively revising this approximation until best approximation is achieved SAR(Successive Approximation Register) holds the current binary value Block Diagram 15 Successive Approximation ADC Circuit waveform Conversion Time n clock for n-bit ADC Fixed conversion time Serial Output is easily generated Chap 0 Logic Flow Bit decision are made in serial order 16 Dual Slope Integrating ADC Operation T1 Integrate 0 vi dt Reset and integrate Thus T1vi ( AVG ) t2Vr t2 v V i ( AVG ) r Applications T1 Chap 0 t2 0 Vr dt DPM(Digital Panel Meter), DMM(Digital Multimeter), … Excellent Noise Rejection High frequency noise cancelled out by integration Proper T1 eliminates line noise Easy to obtain good resolution Low Speed If T1 = 60Hz, converter throughput rate < 30 samples/s 17 Voltage to Frequency ADC VFC (Voltage to Frequency Converter) Convert analog input voltage to train of pulses Counter Generates Digital output by counting pulses over a fixed interval of time Low Speed Good Noise Immunity High resolution For slow varying signal With long conversion time Applicable to remote data sensing in noisy environments Chap 0 Digital transmission over a long distance 18 Parallel or Flash ADC Chap 0 Very High speed conversion Up to 100MHz for 8 bit resolution Video, Radar, Digital Oscilloscope Single Step Conversion 2n –1 comparator Precision Resistive Network Encoder Resolution is limited Large number of comparator in IC Homework #5-1 어떻게 동시에 비교가 되는지를 설명하라. 19 Software Implementation Implementation with software using microprocessor Counting Shifting Inverting Code Conversion … Chap 0 Limited Practical Use Availability of Good performance with very reasonable Cost 20 Shaft Encoder Chap 0 Elctromechanical ADC Convert shaft angle to digital output Encoding Optical or Magnetic Sensor Applications Machine tools, Industrial robotics, Numerical control Binary Encoder Misalignment of mechanism causes large error Ex: 011 111 (180deg) Gray Encoder Misalignment causes 1 LSB error 21 Interfacing the ADC to the IBM PC Interface Operations Most-recent-data Scheme At end of conversion it updates an output FIFO Automatically start new conversion CPU read FIFO to acquire most recent data CPU initiate conversion every time it needs new data CPU check EOC until conversion is finished Using CPU Interrupt Start-and-wait Scheme Chap 0 CPU initiate conversion every time it needs new data CPU can proceed to do other thing ADC interrupt CPU when conversion is complete CPU goes to ISR See Chapter 3, For more information about 8259A 22 Interface Software Memory Mapped Transfers ADC is assigned in Memory Space MRD, MWR signal MOV instruction More complex decoding logic I/O Mapped Transfers ADC is in I/O Space IOR, IOW signal IN, OUT instruction More Simple decoding logic DMA (Direct Memory Access) CPU release system bus by the request of DMA DMA controller carried out data transfer by generating the required addresses and control signals The system bus control reverts back to CPU when data transfer is finished DMA is useful High Speed High volume data transfer Chap 0 Disk Drive interface 23 Interface Hardware Parallel Data Format Three state output buffer in ADC To Interface ADC CPU + Decoding logic • To generate Chip Select signal • To generate Start Signal • To Check EOC signal Chap 0 Serial Data Format Asynchronous Serial transmission to send data over long distance to a monitoring station UART is commonly used Interfacing 10 or 12 bit ADC Transfer data in chunks of 8 bits one after another 24 DAS (Data Acquisition System) Chap 0 DAS performs the complete function of converting the raw outputs from one or more sensors into equivalent digital signals usable for further processing, control, or displaying applications Applications Simple monitoring of a single analog variable Control and Monitoring of hundreds of parameters in a nuclear plant 25 Single Channel System Transducer Generate signal of low amplitude, mixed with undesirable noise Amplifier, Filters Amplify Remove noise Linearize S/H (Sample and Hold) Reduce uncertainty error in the converted output when input changes are fast compared to the conversion time In Multi-channel system Chap 0 To hold a sample from one channel while multiplexer proceed to sample next one Simultaneous sampling of two signal 26 Sample and Hold Circuits Care in selecting hold capacitor Ch Low Value High Value Chap 0 Reduces acquisition time Increase Droop Minimize Droop Increase acquisition time Choose capacitor to get a best acquisition time while keeping the droop per conversion below 1 LSB 27 Commercially Available S/H Chap 0 28 Multi-channel System Analog multiplexer and a ADC Chap 0 Low cost Local ADCs and digital multiplexer Higher sampling rate 29 How to select and use an ADC Range of commercially available ADCs Guidelines for using ADCs Use the full input range of the ADC Use a good source of reference signal Look out for fast input signal changes Keep analog and digital grounds separate Minimize interference and loading problem Chap 0 30 Commercially available monolithic ADCs Chap 0 31 Commercially available hybrid ADCs Chap 0 32 A low cost DAS for the IBM PC Multi-channel system Less than $100 ADC0816 from National Semiconductor Constant, repetitive rate Chap 0 1000 samples/s Generating clock For starting ADC conversion For causing interrupt Make a pulse stream from TCLK with short pulses of duration = ½ x BCLK/4 TCLK from 8253 Timer/Counter • Wide pulse 33 ADC circuit for PC prototype board SCSLCT (Start Conversion SeLeCT) : Latched trough port 30CH SCSLCT = H Selection of 30AH (/E10) start conversion SCSLCT = L TCLK’ start conversion INTSLCT (INTerrupt SeLeCT) : Latched trough port 30CH INTSLCT = H EOC cause IRQ2 INTSLCT = L No Interrupt CPU read Status register (Port 309H) to check EOC Chap 0 34 Status Register Chap 0 For polling TCLK and EOC signal Port 309H (/E9) Polling of EOC results in a low level after the data from ADC have been read 35 Throughput rate calculation 4.77MHz / 8 = 596KHz Chap 0 36 Accuracy Calculation Chap 0 Better than 1% accuracy is ensured Actual accuracy with smooth input signal at room temperature will be better than 0.5% 37 Basic Program for Controlling ADC Sampling rate < 200 samples/s Because OUT and IN instruction in Basic takes 5ms Chap 0 38 C Programming for Controlling ADC Chap 0 Sampling from ADC channel 1 at 5ms interval and sending each sampled data point to the DAC 39 Homework #5-2 Prototype board의 회로 도를 참고하여 앞의 C program이 수행되는 과정을 해석하라 예를 들면 Outp(CNTRL,5)가 수행되면 회로도 에서 어떤 신호가 구동되는지 등…. Chap 0 40