SPD3

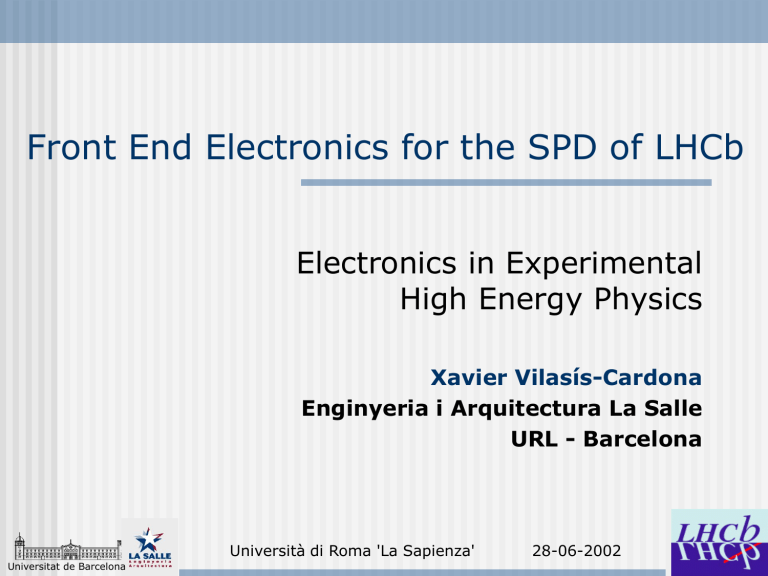

Front End Electronics for the SPD of LHCb

Electronics in Experimental

High Energy Physics

Xavier Vilasís-Cardona

Enginyeria i Arquitectura La Salle

URL - Barcelona

Università di Roma 'La Sapienza' 28-06-2002

Universitat de Barcelona

The collaboration in Barcelona

Universitat de

Barcelona

Lluis Garrido

Ricardo Graciani

David Gascón

Ernest Aguiló

Miriam Calvo

Sergio Gómez

Sebastià Bota

Atilà Herms

Angel Diéguez

Xavier Cano

Enginyeria i

Arquitectura La Salle

Rafael Ballabriga

Sonia Luengo

Mar Roselló

Jordi Riera

Xvc

Outlook

What is LHC ?

What is LHCb ?

The SPD

Photomultipliers

Very Front End Electronics

The ASIC

Front End Electronics

LHC : the future collider at CERN

Proton-Proton

Starting 2007

Find the Higgs

Find new physics

4 detectors

Alice

Atlas

CMS

LHCb

LHC : some data

Energy at collision: 7 TeV (1700 TeV for ions)

Dipole field at 7 TeV: 8.3 T

Bunch spacing: 7.5 m

Bunch separation: 24.95 ns

Particles per bunch: 10^11

Current: 0.56 A

Luminosity: 10^34 cm^2 s

Energy per beam up to 0.35 GJ

Stored magnetic energy up to 1.29 GJ per sector

TOTAL STORED ENERGY = 11 GJ

LHCb

A single-arm spectrometer covering

min ~15 mrad

(beam pipe and radiation)

max ~300 mrad

(cost optimisation)

Precise measurements of

CP violation

B mesons

CKM matrix elements

LHCb : what is CP violation ?

CPT is an exact symmetry

• C charge conjugation

• P parity

• T time reversal

CP is almost exact

CP violation explains matter-antimatter asymmetry

LHCb : the trigger

LHCb = 1000k channels : too much data

The multi-level trigger chain

Input rate Latency

Level 0

Level 1

Level 2

Level 3

40 MHz

1 MHz

40 kHz

5 kHz

3.2 μs

256 μs

10 ms

200 ms

Logging rate 200 Hz (20 MB/s) 200 TB/year

All LHC experiments: 5-8 PB/year

B/s

1 TB/s

4 GB/s

SPD

Scintillator Pad Detector

In front of the calorimeter

Discriminates photons from electrons at level

0 of trigger

spd ps e spd ps ecal ecal

SPD structure

6000 Scintillator Pads

Helicoidal WLS optic fibers

64 channel PMT (Hamamatsu)

1 bit per channel at 40 MHz

Synchronisation issues

Send bit to

PreShower

Compare to a variable threshold

Radiation hard

SPD signal shape

Few photoelectrons

Irregular signal shape

Extended over 25 ns

Non-uniform PMT gain

SPD electronics design

ASIC : why an ASIC ?

6000 channels : minimal area /ch

Processing speed 40 MHz

Power consumption < 2 W / 64 channels

Analog Processing + Digital Control

Signal range. 0 to 5 MIP (0 to 650 mV)

Electronics resolution 5% of 1 MIP

Dynamic range: 40 dB (7 bits)

ASIC Structure

Bunch crossing clock (40 MHz)

Clock frequency division by 2

Clock delay

(about 2 ns)

Single to differential Integrator

Track & Hold

Pile-up subtract Comparator

+

Digital multiplexer

PMT chan. 1

- 17 %

+

ECL internal CLock

(20 MHz)

Channel clocks generation

(CMOS & ECL)

A

D

PMT chan. 2

+

- 17 %

- 17 %

+

A

D

PMT chan. n

Vref (or DAC range) m bits

Serial interface for threshold programing

Digital differential link to PS FE n/2 links

SPD VFE control unit

ASIC characteristics

Programmable

Thresholds per sub-channel

Subtraction: from 0% up to 40% of the signal

T0: done externally with a delay unit (LAL design)

0.8 m AMS BiCMOS Technology

Dual channel

Fully differential

Working at 3.3V

SEU and SEL protection

Triple voting

Guard rings

Review of ASIC runs

RUN1 (Sep 2000)

Test separate blocs

1 full channel

RUN2 (Jun 2001)

4 full channels

ECL vs CMOS output

RUN3 (Jan 2002)

New tunnable substractor

1 full channel with digital control

On-chip DAC to program thresholds

RUN4 (Sep 2002)

1 Complete processing channel

Separate blocs + digital control

Works at 3.3

V to reduce power consumption

Fully differential preamplifier added before the integration stage to meet PMT DC current limit requirements

ASIC : RUN 4 layout

ASIC : integrator

ASIC : Track and Hold

ASIC : substractor

ASIC : latched comparator

ASIC : integrator measurements

10 circuits

Offset ( Output Zero Error ): <OZE> = + 38.6 mV io

Gain: <Vo/Vi> = 16.51 (for a typical input pulse) io

Noise E

E no no

= 70 mV r.m.s.

= 0.091 r.m.s.

(0,55%)

Treset = 5.5 ns (for 1 V output)

< 2 mV r.m.s

(Using scope, C.F. 6)

< 1 mV r.m.s

(Discriminator sweep of thresholds)

B'

1000

800

600

400

Data: Data1_B'

Model: Gauss

Chi^2= 2081.19889

R^2 = 0.98682

y0 51.68159

±23.05052

xc -61.70164

±0.05011

w 1.62784

±0.11995

A 1609.67905

±130.96337

200

0

-66 -64 -62 -60 -58

Threshold [mV]

-56 -54

ASIC : integrator linearity

2500,00

2000,00

1500,00

1000,00

500,00

0,00

-500,00

-1000,00

-1500,00

-2000,00

-2500,00

-4000,00 -3000,00 -2000,00 -1000,00 0,00 1000,00

Input Signal [m V]

2000,00 3000,00

R2B02

R2B04

R2B05

R2B06

R2B07

R2B08

R2B09

R2B01

R2B10

4000,00

ASIC : programmable substractor

Gain of the controlable block of the subtractor = f(Vb) (10 samples)

0,5

0,4

0,3

0,2

0,1

0

3,5

1

0,9

0,8

0,7

0,6

3,7 3,9 4,1 4,3 4,5 4,7

01

02

03

04

05

06

07

08

09

10

01_soldat

4,9

VFE Board description

100 boards

7x12 cm

Multiplexed

LVDS

Very Front End Board

Test beam boards

Sep 2001: RUN 2, 4 full channels/ 4-layer board

•ECL vs CMOS output

•Clock signal distribution

•Power Supply distribution

June 2002: RUN 2, 4 full channels / 4-layer board

•Improvements in board design

•Signals distribution

June 2002: RUN 3, 1 full channel and digital control/ 6-layer board

•Digital signal distribution vs analog signal distribution

•Noise effect vs number of layers

Front End Board

Control Unit :

•Bus Bridge

•Programmable Delays

1 Control Unit every 4 VFE Boards

5 Control Units in a Front End Board

6 Front End Boards

Conclusions