C54x USB from SIEMENS

advertisement

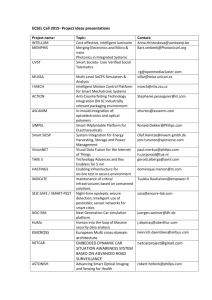

System-On-a-Chip: A case study based on the ELIET Chip Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 1 Contents ELIET Architecture SoC trade-offs Design methodology Specification Problem General information about ELIET Designed to last System Integration Verification Conclusion References Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 2 ELIET Architecture ELIET stands for Electronic ISDN Echo Canceller Transceiver Mixed analog/digital chip integrating all the functions required to implement an LT (line termination) system ELIET building blocks are: custom DSP 8 bit harvard micro-controller embedded memories (ROMs and SRAMs) different internal and external bus protocols A/D and D/A converters PLL ... - Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 3 ELIET Architecture D/A micro code ROMs echo canceller DSP ISDN protocol controller iom/pcm arbiter A/D Coefficients RAMs filter line controller framer deframer filter universal external bus interface Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 4 SoC trade-offs ADVANTAGES: Cost reduction Shortening time to market attack productivity bottlenecks (verification) good design methodology - DISADVANTAGES: Increase of complexity Design methodology and the right verification strategy become critical Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 5 Design Methodology State of the art tools robust and proven design flow rigorous project management definition phase - - guidelines - checklists - design specification - design phase - VHDL coding, DFT, synthesis, floorplan, wireload model generation, P&R - verification phase - behavioural models, RTL simulation, code coverage, GL simulation, formal verification - documentation phase - functional doc. - implementaion doc. - verification doc. Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 6 The Specification Problem specification detailed enough to allow RTL coding save time and unpleasant surprises on silicon serve as feasability study functionality, timing, performance, interfaces, physical issues (area, power, …) continuously updated paper specification formal specification executable specification (C, C++, matlab, Cossap, …) Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 7 The Specification Problem - Overview - Functional requirements - Physical requirements - Verification requirements - Design guidelines - Block diagram - Interfaces - signal names and meanings - transaction protocols (timing diagram) - timing specifications - set-up and hold time on inputs - clock to Q time for outputs - special signals (test, analog, …) - asynchronous signals - clocks, resets, interrupts and their timing - legal values for input and output datas - checklists (paper, scripts, …) Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 8 General information about ELIET Block name Analog Macro PLLs Microprocessor DSP Line controller Interface Microprocessor Memories DSP Memories Total (ELIET) Cell Area (mm2) 2.00 1.10 6.09 3.07 1.60 1.60 1.76 1.75 Infineon Technologies, Sophia-Antipolis, FRANCE Count 4 1 1 1 1 1 1 1 11 Area (mm2) 8.00 1.10 6.09 3.07 1.60 1.60 1.76 1.75 24.97 claudio.talarico@infineon.com % 32.04 4.41 24.39 12.29 6.41 6.41 7.05 7.01 100 9 Some number about ELIET ELIET AREA DISTRIBUTION Microprocessor Memories Interface Analog Macro Line controller PLLs DSP Microprocessor Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 10 Designed to last Chip design constrained by what can be verified, rather than by the functions design style driven by verification (clock synchronous synthesizable RTL) As the complexity of the chip increases “Pray to God approach” is not an option No magic rule to getting first-time-right silicon maximum level of quality in each step of the development process no separation between front end and back end too many macros with the wrong aspect ratio can make the chip unroutable or too big or can create unacceptable delays on critical nets accurate wire load models for DSM bottom up synthesis approach recommended - - Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 11 Designed to last clock distribution accurately studied balanced clock tree with low skews test strategy decided at an early stage of the design BIST for memories full scan flops max 1000 flops per scan chain boundary scan insulation and ad hoc testing for analog macros Guidelines and Checklists RTL coding guidelines coding for portability (ieee standard types, too many subtypes, …) guidelines for clock and reset coding for synthesis check code quality (profiling tools, synthesis results, ...) no unexplained warning - Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 12 System Integration Reduce the number of new gates introduced Massive reuse of existing proven designs reused parts need to be pre-verified with high degree of quality to allow SOC verification to complete within a reasonable time frame not all core configurations have been tested together Focus of system level simulation is on errors at macro interconnections level misunderstanding of the bus protocols different bridges to communicate between the different busses standardize on a single common bus architecture - Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 13 Verification Main bottleneck of the development process Right verification strategy at each step of the design It is verification that drives the selection of tools and design style Define the verification plan as soon as possible a list of all test bench components a list of required verification tools a list of specific tests what functionality will be verified target code coverage description of the regression test environment and regression procedures Test bench design takes more time than the circuit design The entire set of test benches and test suites must be reusable (different design teams) and portable (different simulators) - Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 14 Verification Test bench must be one of the deliverables Bus functional models & bus monitors single test bench command file VHDL test bench guidelines use a clock to synchronize stimuli generation use built in textio packages partition the test bench code in synthesizable and behavioural do not generate data , clocks and resets from the same process common strategy for the test bench for both sub-modules and top level the test bench has to be self-checking (no waveform inspection required) and issue a clear error message in case of failure (what occured, at what time, what was the expectation, what is the result, …) - Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 15 Verification Toggle coverage greater than 98% Timing analysis static timing analysis and formal verification gate level simulation in case of asynchronous parts - Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 16 Conclusion Mixed analog/digital 4 channel ASIC for ISDN 0.35 mm, 3.3 V technology 4 analog macros (about 2 mm2 each) 2 PLLs (about 1.10 mm2 ) microprogrammed 8 bit Harvard processor for the ISDN data processing control (about 6.09 mm2 ) custom DSP implementing the echo cancellation algorithm (about 3.07 mm2 ) line controller (about 1.60 mm2 ) universal external interface and iom/PCM interface (about 1.60 mm2 ) 6 ROMs for the microprogrammed processor (about 1.76 mm2 ) 1 ROM and 4 SRAMs for the DSP (about 1.75 mm2 ) Total Area of the chip ~ 51 mm2 Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 17 Conclusion ELIET AREA DISTRIBUTION M em o. .. In te rfa ce op ro ce ss or M icr DS P co nt ro lle r Li ne icr op ro ce ss or PL Ls M An al og M ac ro 35.00 30.00 25.00 20.00 15.00 10.00 5.00 0.00 Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 18 Conclusion Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 19 References M.Keating, P. Bricaud Reuse methodology manual for system-on-a-chip Designs Kluwer Academic Publishers, 1998 A.M. Rincon, W.R. Lee, M. Slattery The Changing Landscape of System-on-a-Chip Design Custom Integrated Circuits Conference, 1999 R.D. Adams System on a chip Testing Custom Integrated Circuits Conference Educational Sessions, 1999 D.D. Warmke Four white papers on VHDL design Integrated System Design, 1993 Infineon Technologies, Sophia-Antipolis, FRANCE claudio.talarico@infineon.com 20