CPS 5401 Intro to Computational Science Name Fall 2012 Shirley

advertisement

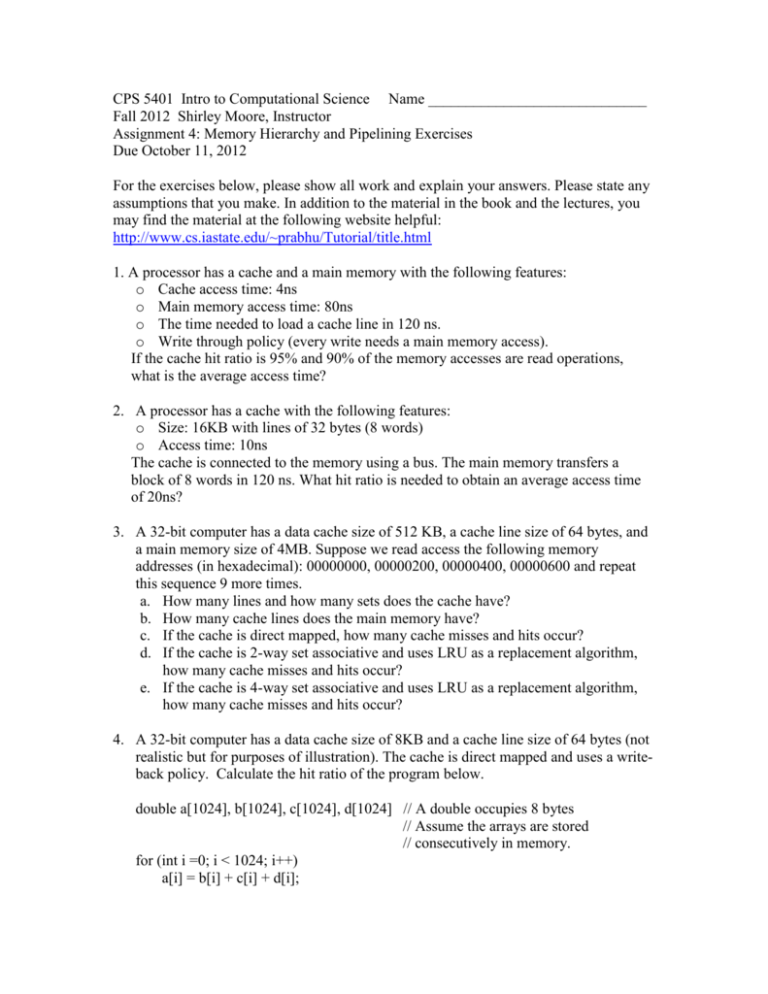

CPS 5401 Intro to Computational Science Name _____________________________ Fall 2012 Shirley Moore, Instructor Assignment 4: Memory Hierarchy and Pipelining Exercises Due October 11, 2012 For the exercises below, please show all work and explain your answers. Please state any assumptions that you make. In addition to the material in the book and the lectures, you may find the material at the following website helpful: http://www.cs.iastate.edu/~prabhu/Tutorial/title.html 1. A processor has a cache and a main memory with the following features: o Cache access time: 4ns o Main memory access time: 80ns o The time needed to load a cache line in 120 ns. o Write through policy (every write needs a main memory access). If the cache hit ratio is 95% and 90% of the memory accesses are read operations, what is the average access time? 2. A processor has a cache with the following features: o Size: 16KB with lines of 32 bytes (8 words) o Access time: 10ns The cache is connected to the memory using a bus. The main memory transfers a block of 8 words in 120 ns. What hit ratio is needed to obtain an average access time of 20ns? 3. A 32-bit computer has a data cache size of 512 KB, a cache line size of 64 bytes, and a main memory size of 4MB. Suppose we read access the following memory addresses (in hexadecimal): 00000000, 00000200, 00000400, 00000600 and repeat this sequence 9 more times. a. How many lines and how many sets does the cache have? b. How many cache lines does the main memory have? c. If the cache is direct mapped, how many cache misses and hits occur? d. If the cache is 2-way set associative and uses LRU as a replacement algorithm, how many cache misses and hits occur? e. If the cache is 4-way set associative and uses LRU as a replacement algorithm, how many cache misses and hits occur? 4. A 32-bit computer has a data cache size of 8KB and a cache line size of 64 bytes (not realistic but for purposes of illustration). The cache is direct mapped and uses a writeback policy. Calculate the hit ratio of the program below. double a[1024], b[1024], c[1024], d[1024] // A double occupies 8 bytes // Assume the arrays are stored // consecutively in memory. for (int i =0; i < 1024; i++) a[i] = b[i] + c[i] + d[i]; 5. Repeat exercise 4 assuming a fully associative cache with LRU as the replacement algorithm. 6. Repeat exercise 4 assuming a 2-way associative cache with LRU as the replacement algorithm. 7. Repeat exercise 4 assuming a 4-way associative cache with LRU as the replacement algorithm. 8. A 32-bit computer has a data cache of 32KB with lines of 64 bytes. The cache is 2way set associative. Consider the following code fragment: int m[512][512]; sum = 0; for (i = 0; i < 512; i++) for (j = 0; j < 512; j++) sum = sum + m[i][j]; Assuming that the sum variable is stored in a register, calculate the hit ratio for the above fragment. Recall that in C, arrays are stored in row-major order. 9. Repeat exercise 8 for the following code fragment: int m[512][512]; sum = 0; for (i = 0; i < 512; i++) for (j = 0; j < 512; j++) sum = sum + m[j][i]; 9. Assume a task can be broken in to k equal operations and executed in a pipeline with k equal stages and an execution time of T per stage. a. Give a formula for the execution time T1 of a single task. b. Give a formula for the execution time Tseq(n) for the execution time of n tasks with no pipelining. c. Give a formula for the execution time Tpipe(n) for the execution time of n tasks with perfect pipelining (i.e., assuming no pipeline bubbles). d. Give a formula for the speedup for n tasks due to pipelining. 10. How many stages does a pipeline have if it achieves a speedup of 9.9 for 90 operations? 11. How much time is required to execute 1000 operations in a pipeline with 7 equal stages and an execution time of 2 ns per stage?