One - personal.stevens.edu

advertisement

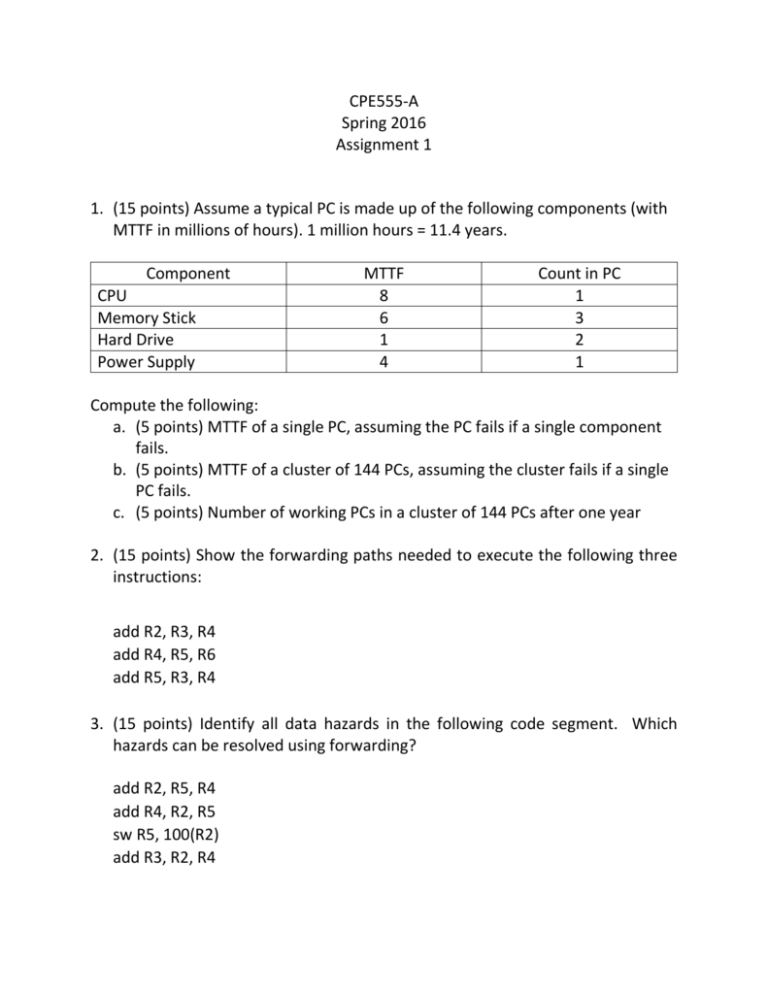

CPE555-A Spring 2016 Assignment 1 1. (15 points) Assume a typical PC is made up of the following components (with MTTF in millions of hours). 1 million hours = 11.4 years. Component CPU Memory Stick Hard Drive Power Supply MTTF 8 6 1 4 Count in PC 1 3 2 1 Compute the following: a. (5 points) MTTF of a single PC, assuming the PC fails if a single component fails. b. (5 points) MTTF of a cluster of 144 PCs, assuming the cluster fails if a single PC fails. c. (5 points) Number of working PCs in a cluster of 144 PCs after one year 2. (15 points) Show the forwarding paths needed to execute the following three instructions: add R2, R3, R4 add R4, R5, R6 add R5, R3, R4 3. (15 points) Identify all data hazards in the following code segment. Which hazards can be resolved using forwarding? add R2, R5, R4 add R4, R2, R5 sw R5, 100(R2) add R3, R2, R4 4. (15 points) Considering that designing a cache controller that can handle nonexistent addresses is complex, can you make a fully-associative cache containing exactly 3K words of data? How about a set-associative cache or direct-mapped cache containing exactly 3K words of data? For each describe why or why not. Use the approximation 1000 2 10 . 5. (15 points) A cache has 64 KB capacity, 128-byte lines and is 4-way setassociative. The processor using the cache is a 32-bit processor (i.e., the addresses are 32-bits wide). a. How many lines and sets does the cache have? (5 points) b. How many entries are required in the Tag array? (5 points) c. How many bits of Tag are required in each entry in the Tag array? (5 points) 6. (25 points) Consider the code fragment shown below: int M[16]; for(int i=1; i<=2; i++) for(int j=1; j<16; j=j+3) x = M[j] + 1; Assume the following: Memory is arranged in bytes, with one word = 4 bytes. Array M[] starts at memory address 0, i.e., M[0] is at address 0, M[1] at address 4, etc. The program is run on a machine with a direct-mapped cache that has 2 word (8 byte) blocks, and holds 32 total bytes (4 blocks) of data. References to i, j and x don’t touch the cache (e.g., these variables use fixed registers allocated to them); we only care about array M[]. Assume the cache starts empty. Answer the following: a. What is the miss rate in this cache for this code? (15 points) b. How many of the misses are conflict misses? Which ones are they? (10 points)