Module-2/MCS-51 microcontroller

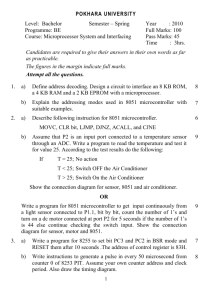

advertisement

Applications of Microcontroller-I Prof. Ramakant Patil TE SEM-V Instrumentation Engineering Module-2/MCS-51 microcontroller 2.1 What is 8051 Microcontroller? 8051 is an 8-bit family of microcontroller developed by Intel in the year 1981. This is one of the most popular families of microcontroller being used all across the world. This microcontroller was also referred as “system on a chip” because it has 128 bytes of RAM, 4Kbytes of ROM, 2 Timers, 1 Serial port, and four ports on a single chip. The CPU can work for only 8bits of data at a time because 8051 is an 8-bit processor. In case the data is larger than 8 bits then it has to be broken into parts so that the CPU can process conveniently. Most manufacturers have put 4Kbytes of ROM even though the quantity of ROM can be exceeded up to 64 K bytes. The 8051 has been in use in a wide number of devices, mainly because it is easy to integrate into a project or build a device around. The following are the main areas of focus: i. Energy Management: Efficient metering systems help in controlling energy usage in homes and industrial applications. These metering systems are made capable by incorporating microcontrollers. ii. Touch screens: A high number of microcontroller providers incorporate touch-sensing capabilities in their designs. Portable electronics such as cell phones, media players and gaming devices are examples of microcontroller-based touch screens. iii. Automobiles: The 8051 finds wide acceptance in providing automobile solutions. They are widely used in hybrid vehicles to manage engine variants. Additionally, functions such as cruise control and anti-brake system have been made more efficient with the use of microcontrollers. iv. Medical Devices: Portable medical devices such as blood pressure and glucose monitors use microcontrollers will to display data, thus providing higher reliability in providing medical results. 2.2 Features of Microcontroller 8051: Following are the main features of Micro controller 8051 which makes it most efficient Microcontroller chip: 1) It Includes Boolean Processing Engine. Thus internal registers and RAM can carry Boolean logic operations directly and efficiently. 2) It gives us many functions in a single chip. (e.g. CPU,RAM,ROM,I/O, Interrupt, Timer etc) 3) It has 8 bit Data bus. 4) It have 8 bit Stack Pointer 5) It have 16 bit Program Counter. 6) It has 16 bit address bus which can access almost 65,536 memory locations. 7) Data memory or RAM of 128 bytes. (On-Chip). 1 8) Program Memory or ROM of 4 KB. (On-Chip). 9) Bi-Directional I/O port of 4 bytes. 10) It has 4 separate Register Sets. 11) Serial Port or UART. 12) It features Power Saving Mode which saves power. 13) Two Timers/Counters each of 16 bit. 14) Internal and External Interrupt Sources. 15) 2 levels interrupt priority. 2.3 Comparison between Microprocessor and Microcontroller: Sr.No. Microprocessor Microcontroller 1 The architecture uses data lines more than The architecture uses control lines more control lines. that data lines. 2 No RAM and ROM on the chip RAM and ROM along with processor are present 3 It has single or dual bit instructions It has multi bit instructions 4 Access time to memory and I/O devices is Access time to memory and I/O devices is high less 5 Less number of pins are multiplexed More number of pins are multiplexed 6 Consists of single memory map for data Consists of separate memory map for data and code and code 7 High clock frequency Low clock frequency 8 External peripheral are to interfaced to These are application specific and so no enhance functionality need of external peripherals 9 Can perform all the computation in any Can perform only a specific task field 10 Cost is high Cost is low 11 I/O communication needs external I/O communication ports are inbuilt peripherals 12 Serial communication is not possible Serial communication ports are inbuilt 13 Boolean operations cannot be performed Boolean operations can be performed directly directly 2.4 Comparison between Microcontroller Families: Features 8051 8031 8032 8052 4K 0 0 8K ROM 128 128 256 256 RAM 2 2 3 3 Timers I/O pins Serial Port Interrupt Sources 32 1 6 32 1 6 32 1 5 32 1 8 2 8751 4KEPROM 128 2 8752 8KEPROM 256 3 32 1 5 32 1 6 89XX ROM RAM TIMER Interrupt Sources I/O pins Other 8951 4k 128 2 6 8952 8k 256 3 8 8953 12k 256 3 9 8955 20k 256 3 8 898252 8k 256 3 9 32 - 32 - 32 Watch Dog Timer 32 Watch Dog Timer 32 In System Programmable 891051 1k 64 1 3 892051 2k 128 2 6 16 16 Analog Analog Comparator Comparator 2.5 Block diagram of 8051 microcontroller: Following is the block diagram of Microcontroller 8051. Microcontroller 8051 - Block Diagram Explanation: Central Processor Unit(CPU): It monitors and controls all operations that are performed in the Microcontroller. User has no control over the work of CPU. It reads program written in ROM memory and executes them and do the expected task. Interrupts: As its name suggests, Interrupt is a subroutine call that interrupts Microcontroller's main operation or work and causes it to execute some another program which is more important at that time. The feature of Interrupt is very useful as it helps in cases of emergency. Interrupts gives us a mechanism to put on hold the ongoing operation, execute a subroutine and then again resumes normal program execution. The Microcontroller 8051 can be configured in such a way that it temporarily terminates or pause the main program at the occurrence of interrupt. When subroutine is completed then the execution of main program starts as usual. There are five interrupt sources in 8051 Microcontroller. 2 of them are external interrupts, 2 timer interrupts and one serial port interrupt. Memory: Microcontroller requires a program which is a collection of instructions. This program tells Microcontroller to do specific tasks. These programs require a memory on which these can be saved and read by Microcontroller to perform specific operation. The memory which is used 3 to store the program of Microcontroller is known as code memory or Program memory. It is known as 'ROM'(Read Only Memory). Microcontroller also requires a memory to store data or operands temporarily. The memory which is used to temporarily store data for operation is known as Data Memory and we uses 'RAM'(Random Access Memory) for this purpose. Microcontroller 8051 has 4K of Code Memory or Program memory that is it has 4KB Rom and it also have 128 bytes of data memory i.e. RAM. Bus: Basically Bus is a collection of wires which work as a communication channel or medium for transfer of Data. These buses consist of 8, 16 or more wires. Thus these can carry 8 bits, 16 bits simultaneously. Buses are of two types: Address Bus Data Bus Address Bus: Microcontroller 8051 has a 16 bit address bus. It used to address memory locations. It is used to transfer the address from CPU to Memory. Data Bus: Microcontroller 8051 has 8 bits data bus. It is used to carry data. Oscillator: As we know Microcontroller is a digital circuit device, therefore it requires clock for its operation. For this purpose, Microcontroller 8051 has an on-chip oscillator which works as a clock source for Central Processing Unit. As the output pulses of oscillator are stable therefore it enables synchronized work of all parts of 8051 Microcontroller. Input/output Port: As we know that Microcontroller is used in embedded systems to control the operation of machines. Therefore to connect it to other machines, devices or peripherals we require I/O interfacing ports in Microcontroller. For this purpose Microcontroller 8051 has 4 input output ports to connect it to other peripherals. Timers/Counters: Microcontroller 8051 has 2 16 bit timers and counters. The counters are divided into 8 bit registers. The timers are used for measurement of intervals, to determine pulse width etc. 4 2.6 PIN Diagram of the 8051: 5 Port 0(p0.0 to p0.7): It is 8-bit bi-directional I/O port. It is bit/ byte addressable. During external memory access, it functions as multiplexed data and low-order address bus AD0-AD7. Port 1 (p1.0 to p1.7): It is 8-bit bi-directional I/O port. It is bit/ byte addressable. When logic '1' is written into port latch then it works as input mode. It functions as simply I/O port and it does not have any alternative function. Port 2 (p2.0 to p2.7): It is 8-bit bi-directional I/O port. It is bit/ byte addressable. During external memory access it functions as higher order address bus (A8-A15). Port 3(p3.0 to port 3.7): It is 8-bit I/O port. In an alternating function each pins can be used as a special function I/O pin. P3.0-RxD: It is an Input signal. Through this I/P signal microcontroller receives serial data of serial communication circuit. P3.1-TxD: It is O/P signal of serial port. Through this signal data is transmitted. P3.2- (INT0): It is external hardware interrupt I/P signal. Through this user, programmer or peripheral interrupts to microcontroller. P3.3-(INT1): It is external hardware interrupt I/P signal. Through this user, programmer or peripheral interrupts to microcontroller. P3.4- T0: It is I/P signal to internal timer-0 circuit. External clock pulses can connects to timer-0 through this I/P signal. P3.5-T1: It is I/P signal to internal timer-1 circuit. External clock pulses can connects to timer-1 through this I/P signal. 6 P3.6-[WR(bar)]: It is active low write O/P control signal. During External RAM (Data memory) access it is generated by microcontroller. when [WR(bar)]=0, then performs write operation. P3.7-[RD(bar)]: It is active low read O/P control signal. During External RAM (Data memory) access it is generated by microcontroller. when [RD(bar)]=0, then performs read operation from external RAM. XTAL1 and XTAL2: These are two I/P line for on-chip oscillator and clock generator circuit. A resonant network as quartz crystal is connected between these two pin. 8051 microcontroller also drives from external clock, then XTAL2 is used to drive 8051 from external clock and XTAL1 should be grounded. [EA(bar)]/VPP: It is and active low I/P to 8051 microcontroller. when (EA)= 0, then 8051 microcontroller access from external program memory (ROM) only. When (EA) = 1, then it access internal and external program memories (ROMs). [PSEN(bar)]: It is active low O/P signal. It is used to enable external program memory (ROM). When [PSEN(bar)]= 0, then external program memory becomes enabled and microcontroller read content of external memory location. Therefore it is connected to (OE) of external ROM. It is activated twice every external ROM memory cycle. ALE: Address latch enable: It is active high O/P signal. When it goes high, external address latch becomes enabling and lower address of external memory (RAM or ROM) latched into it. Thus it separates A0-A7 address from AD0-AD7. It provides properly timed signal to latch lower byte address. The ALE is activated twice in every machine cycle. If external RAM & ROM is not accessed, then ALE is activated at constant rate of 1/6 oscillator frequency, which can be used as a clock pulses for driving external devices. RESET: It is active high I/P signal. It should be maintained high for at least two machine cycle while oscillator is running then 8051 microcontroller resets. 7 2.7 Architecture of 8051 Microcontroller: 8 An 8051 microcontroller has the following 12 major components: 1. ALU (Arithmetic and Logic Unit) 2. PC (Program Counter) 3. Registers 4. Timers and Counters 5. Internal RAM and ROM 6. Four general purpose parallel input/output ports 7. Interrupt control logic with five sources of interrupt 8. Serial data communication 9. PSW (Program Status Word) 10. Data Pointer (DPTR) 11. Stack Pointer (SP) 12. Data and Address bus. 9 1. ALU- All arithmetic and logical functions are carried out by the ALU. Addition, subtraction with carry, and multiplication come under arithmetic operations. Logical AND, OR and exclusive OR (XOR) come under logical operations. 2. Program Counter (PC)- A program counter is a 16-bit register and it has no internal address. The basic function of program counter is to fetch from memory the address of the next instruction to be executed. The PC holds the address of the next instruction residing in memory and when a command is encountered, it produces that instruction. This way the PC increments automatically, holding the address of the next instruction. 3. Registers- Registers are usually known as data storage devices. 8051 microcontroller has 2 registers, namely Register A and Register B. Register A serves as an accumulator while Register B functions as a general purpose register. These registers are used to store the output of mathematical and logical instructions. The operations of addition, subtraction, multiplication and division are carried out by Register A. Register B is usually unused and comes into picture only when multiplication and division functions are carried out by Register A. Register A also involved in data transfers between the microcontroller and external memory. 8051 microcontroller also has 7 Special Function Registers (SFRs). They are: i. Serial Port Data Buffer (SBUF) ii. Timer/Counter Control (TCON) iii. Timer/Counter Mode Control (TMOD) iv. Serial Port Control (SCON) v. Power Control (PCON) vi. Interrupt Priority (IP) vii. Interrupt Enable Control (IE) 4. Timers and Counters- Synchronization among internal operations can be achieved with the help of clock circuits which are responsible for generating clock pulses. During each clock pulse a particular operation will be carried out, thereby, assuring synchronization among operations. For the formation of an oscillator, we are provided with two pins XTAL1 and XTAL2 which are used for connecting a resonant network in 8051 microcontroller device. In addition to this, circuit also consists of four more pins. They are, i. EA: External enables ii. ALE: Address latch enable iii. PSEN: Program store enable and iv. RST: Reset. Internal operations can be synchronized using clock circuits which produce clock pulses. With each clock pulse, a particular function will be accomplished and hence synchronization is achieved. There are two pins XTAL1 and XTAL2 which form an oscillator circuit which connect to a resonant network in the microcontroller. Quartz crystal is used to generate periodic clock pulses. 5. Internal RAM and ROM ROM A code of 4K memory is incorporated as on-chip ROM in 8051. The 8051 ROM is a nonvolatile memory meaning that its contents cannot be altered and hence has a similar range of data and program memory, i.e, they can address program memory as well as a 64K separate block of data memory. 10 RAM The 8051 microcontroller is composed of 128 bytes of internal RAM. This is a volatile memory since its contents will be lost if power is switched off. These 128 bytes of internal RAM are divided into 32 working registers which in turn constitute 4 register banks (Bank 0-Bank 3) with each bank consisting of 8 registers (R0 - R7). There are 128 addressable bits in the internal RAM. 6. Four General Purpose Parallel Input/output Ports The 8051 microcontroller has four 8-bit input/output ports. These are: PORT P0: When there is no external memory present, this port acts as a general purpose input/output port. In the presence of external memory, it functions as a multiplexed address and data bus. It performs a dual role. PORT P1: This port is used for various interfacing activities. This 8-bit port is a normal I/O port i.e. it does not perform dual functions. PORT P2: Similar to PORT P0, this port can be used as a general purpose port when there is no external memory but when external memory is present it works in conjunction with PORT PO as an address bus. This is an 8-bit port and performs dual functions. PORT P3: PORT P3 behaves as a dedicated I/O port 7. Interrupt Control An event which is used to suspend or halt the normal program execution for a temporary period of time in order to serve the request of another program or hardware device is called an interrupt. An interrupt can either be an internal or external event which suspends the microcontroller for a while and thereby obstructs the sequential flow of a program. 11 There are two ways of giving interrupts to a microcontroller – one is by sending software instructions and the other is by sending hardware signals. The interrupt mechanism keeps the normal program execution in a "put on hold" mode and executes a subroutine program and after the subroutine is executed, it gets back to its normal program execution. This subroutine program is also called an interrupt handler. A subroutine is executed when a certain event occurs. In 8051, 5 sources of interrupts are provided. They are: a) 2 external interrupt sources connected through INT0 and INT1 b) 3 external interrupt sources- serial port interrupt, Timer Flag 0 and Timer Flag 1. The pins connected are as follows: i. ALE (Address Latch Enable) - Latches the address signals on Port P0 ii. EA (External Address) - Holds the 4K bytes of program memory iii. PSEN (Program Store Enable) - Reads external program memory iv. RST (Reset) - Reset the ports and internal registers upon start up 8. Serial Data Communication A method of establishing communication among computers is by transmitting and receiving data bits is a serial connection network. In 8051, the SBUF (Serial Port Data Buffer) register holds the data; the SCON (Serial Control) register manages the data communication and the PCON (Power Control) register manages the data transfer rates. Further, two pins - RXD and TXD, establish the serial network. The SBUF register has 2 parts – one for storing the data to be transmitted and another for receiving data from outer sources. The first function is done using TXD pin and the second function is done using RXD pin. There are 4 programmable modes in serial data communication. They are: i. Serial Data mode 0 (shift register mode) ii. Serial Data mode 1 (standard UART) iii. Serial Data mode 2 (multiprocessor mode) iv. Serial Data mode 3 9. PSW (Program Status Word) 12 Program Status Word or PSW is a hardware register which is a memory location which holds a program's information and also monitors the status of the program this is currently being executed. PSW also has a pointer which points towards the address of the next instruction to be executed. PSW register has 3 fields namely are instruction address field, condition code field and error status field. We can say that PSW is an internal register that keeps track of the computer at every instant. Generally, the instruction of the result of a program is stored in a single bit register called a 'flag'. The are7 flags in the PSW of 8051. Among these 7 flags, 4 are math flags and 3 are general purpose or user flags. The 4 Math flags are: • Carry (c) • Auxiliary carry (AC) • Overflow (OV) • Parity (P) The 3 General purpose flags or User flags are: • FO • GFO • GF 1 10. Data Pointer (DPTR) The data pointer or DPTR is a 16-bit register. It is made up of two 8-bit registers called DPH and DPL. Separate addresses are assigned to each of DPH and DPL. These 8-bit registers are used for the storing the memory addresses that can be used to access internal and external data/code. 11. Stack Pointer (SP) The stack pointer (SP) in 8051 is an 8-bit register. The main purpose of SP is to access the stack. As it has 8-bits it can take values in the range 00 H to FF H. Stack is a special area of data in memory. The SP acts as a pointer for an address those points to the top of the stack. 12. Data and Address Bus A bus is group of wires using which data transfer takes place from one location to another within a system. Buses reduce the number of paths or cables needed to set up connection between components. There are mainly two kinds of buses - Data Bus and Address Bus Data Bus: The purpose of data bus is to transfer data. It acts as an electronic channel using which data travels. Wider the width of the bus, greater will be the transmission of data. Address Bus: The purpose of address bus is to transfer information but not data. The information tells from where within the components, the data should be sent to or received from. The capacity or memory of the address bus depends on the number of wires that transmit a single address bit. 13 2.8 Port Structure I/O Ports Microcontroller 8051: All 8051 microcontrollers have 4 I/O ports each comprising 8 bits which can be configured as inputs or outputs. Accordingly, in total of 32 input/output pins enabling the microcontroller to be connected to peripheral devices are available for use. Input/output (I/O) pin Figure below illustrates a simplified schematic of all circuits within the microcontroller connected to one of its pins. It refers to all the pins except those of the P0 port which do not have pull-up resistors built-in. Output pin A logic zero (0) is applied to a bit of the P register. The output FE transistor is turned on, thus connecting the appropriate pin to ground. Input pin A logic one (1) is applied to a bit of the P register. The output FE transistor is turned off and the 14 appropriate pin remains connected to the power supply voltage over a pull-up resistor of high resistance. PORT 0: The structure of a Port-0 pin is shown in fig 6.It has 8 pins (P0.0-P0.7). Port-0 can be used as a normal bidirectional I/O port or it can be used for address/data interfacing for accessing external memory. When control is '1', the port is used for address/data interfacing. When the control is '0', the port can be used as a bidirectional I/O port. PORT 0 as an Input Port Let us assume that control is '0'. When the port is used as an input port, '1' is written to the latch. In this situation both the output MOSFETs are 'off'. Hence the output pins have floats hence whatever data written on pin is directly read by read pin. 15 PORT 0 as an Output Port Suppose we want to write 1 on pin of Port 0, a '1' written to the latch which turns 'off' the lower FET while due to '0' control signal upper FET also turns off as shown in fig. above. Here we wants logic '1' on pin but we getting floating value so to convert that floating value into logic '1' we need to connect the pull up resistor parallel to upper FET . This is the reason why we needed to connect pull up resistor to port 0 when we want to initialize port 0 as an output port. If we want to write '0' on pin of port 0, when '0' is written to the latch, the pin is pulled down by the lower FET. Hence the output becomes zero. 16 When the control is '1', address/data bus controls the output driver FETs. If the address/data bus (internal) is '0', the upper FET is 'off' and the lower FET is 'on'. The output becomes '0'. If the address/data bus is '1', the upper FET is 'on' and the lower FET is 'off'. Hence the output is '1'. Hence for normal address/data interfacing (for external memory access) no pull-up resistors are required.Port-0 latch is written to with 1's when used for external memory access. PORT 1: The structure of a port-1 pin is shown in fig below. It has 8 pins (P1.1-P1.7). Port-1 dedicated only for I/O interfacing. When used as output port, not needed to connect additional pull-up resistor like port 0. It have provided internally pull-up resistor as shown in fig. The pin is pulled up or down through internal pull-up when we want to initialize as an output port. To use port-1 as input port, '1' has to be written to the latch. In this input mode when '1' is written to the pin by the external device then it read fine. But when '0' is written to the pin by the external device then the external source must sink current due to internal pull-up. If the external 17 device is not able to sink the current the pin voltage may rise, leading to a possible wrong reading. PORT 2: The structure of a port-2 pin is shown in fig. below. It has 8-pins (P2.0-P2.7). Port-2 we use for higher external address byte or a normal input/output port. The I/O operation is similar to Port-1. Port-2 latch remains stable when Port-2 pin are used for external memory access. Here again due to internal pull-up there is limited current driving capability. PORT 3: Port-3 (P3.0-P3.7) having an alternate function to each pin, the internal structure of a port-3 pin is shown in fig below. 18 Following are the alternate functions of port 3: It works as an IO port same like Port 2. Only alternate function of port 3 makes its architecture different than other ports. 2.9 Memory Organization: The 8051 has two types of memory and these are Program Memory and Data Memory. Program Memory (ROM) is used to permanently save the program being executed, while Data Memory (RAM) is used for temporarily storing data and intermediate results created and used during the operation of the microcontroller. Depending on the model in use (we are still talking about the 8051 microcontroller family in general) at most a few Kb of ROM and 128 or 256 bytes of RAM is used. All 8051 microcontrollers have a 16-bit addressing bus and are capable of addressing 64 kb memory. 19 Program Memory The first models of the 8051 microcontroller family did not have internal program memory. It was added as an external separate chip. These models are recognizable by their label beginning with 803 (for example 8031 or 8032). All later models have a few Kbyte ROM embedded. Even though such an amount of memory is sufficient for writing most of the programs, there are situations when it is necessary to use additional memory as well. A typical example is so called lookup tables. They are used in cases when equations describing some processes are too complicated or when there is no time for solving them. In such cases all necessary estimates and approximates are executed in advance and the final results are put in the tables (similar to logarithmic tables). How does the microcontroller handle external memory depend on the EA pin logic state? EA=0 In this case, the microcontroller completely ignores internal program memory and executes only the program stored in external memory. EA=1 In this case, the microcontroller executes first the program from built-in ROM, then the program stored in external memory. 20 In both cases, P0 and P2 are not available for use since being used for data and address transmission. Besides, the ALE and PSEN pins are also used. Data Memory As already mentioned, Data Memory is used for temporarily storing data and intermediate results created and used during the operation of the microcontroller. Besides, RAM memory built in the 8051 family includes many registers such as hardware counters and timers, input/output ports, serial data buffers etc. The previous models had 256 RAM locations, while for the later models this number was incremented by additional 128 registers. However, the first 256 memory locations (addresses 0-FFh) are the heart of memory common to all the models belonging to the 8051 family. Locations available to the user occupy memory space with addresses 0-7Fh, i.e. first 128 registers. This part of RAM is divided in several blocks. The first block consists of 4 banks each including 8 registers denoted by R0-R7. Prior to accessing any of these registers, it is necessary to select the bank containing it. The next memory block (address 20h-2Fh) is bit- addressable, which means that each bit has its own address (07Fh). Since there are 16 such registers, this block contains in total of 128 bits with separate addresses (address of bit 0 of the 20h byte is 0, while address of bit 7 of the 2Fh byte is 7Fh). The third group of registers occupies addresses 2Fh-7Fh, i.e. 80 locations, and does not have any special functions or features. Additional RAM In order to satisfy the programmers’ constant hunger for Data Memory, the manufacturers decided to embed an additional memory block of 128 locations into the latest versions of the 8051 microcontrollers. However, it’s not as simple as it seems to be… The problem is that electronics performing addressing has 1 byte (8 bits) on disposal and is capable of reaching only the first 256 locations, therefore. In order to keep already existing 8-bit architecture and compatibility with other existing models a small trick was done. What does it mean? It means that additional memory block shares the same addresses with locations intended for the SFRs (80h- FFh). In order to differentiate between these two physically separated memory spaces, different ways of addressing are used. The SFRs memory locations are accessed by direct addressing, while additional RAM memory locations are accessed by indirect addressing. 21 22 Memory expansion In case memory (RAM or ROM) built in the microcontroller is not sufficient, it is possible to add two external memory chips with capacity of 64Kb each. P2 and P3 I/O ports are used for their addressing and data transmission. From the user’s point of view, everything works quite simply when properly connected because most operations are performed by the microcontroller itself. The 8051 microcontroller has two pins for data read RD and PSEN. The first one is used for reading data from external data memory (RAM), while the other is used for reading data from external program memory (ROM). Both pins are active low. A typical example of memory expansion by adding RAM and ROM chips (Hardward architecture), is shown in figure above. 23 Even though additional memory is rarely used with the latest versions of the microcontrollers, we will describe in short what happens when memory chips are connected according to the previous schematic. The whole process described below is performed automatically. When the program during execution encounters an instruction which resides in external memory (ROM), the microcontroller will activate its control output ALE and set the first 8 bits of address (A0-A7) on P0. IC circuit 74HCT573 passes the first 8 bits to memory address pins. A signal on the ALE pin latches the IC circuit 74HCT573 and immediately afterwards 8 higher bits of address (A8-A15) appear on the port. In this way, a desired location of additional program memory is addressed. It is left over to read its content. Port P0 pins are configured as inputs, the PSEN pin is activated and the microcontroller reads from memory chip. Similar occurs when it is necessary to read location from external RAM. Addressing is performed in the same way, while read and write are performed via signals appearing on the control outputs RD (is short for read) or WR (is short for write). 2.10 Addressing in 8051: An "addressing mode" refers to how you are addressing a given memory location. In summary, the addressing modes are as follows, with an example of each: Immediate Addressing MOV A,#20h MOV A,30h Direct Addressing Indirect Addressing MOV A,@R0 MOVX A,@DPTR External Direct MOVC A,@A+DPTR Code Indirect Each of these addressing modes provides important flexibility. 1. Immediate Addressing Immediate addressing is so-named because the value to be stored in memory immediately follows the operation code in memory. That is to say, the instruction itself dictates what value will be stored in memory. For example, the instruction: MOV A,#20h This instruction uses Immediate Addressing because the Accumulator will be loaded with the value that immediately follows; in this case 20 (hexadecimal). 24 Immediate addressing is very fast since the value to be loaded is included in the instruction. However, since the value to be loaded is fixed at compile-time it is not very flexible. 2. Direct Addressing Direct addressing is so-named because the value to be stored in memory is obtained by directly retrieving it from another memory location. For example: MOV A,30h This instruction will read the data out of Internal RAM address 30 (hexadecimal) and store it in the Accumulator. Direct addressing is generally fast since, although the value to be loaded isn’t included in the instruction, it is quickly accessible since it is stored in the 8051s Internal RAM. It is also much more flexible than Immediate Addressing since the value to be loaded is whatever is found at the given address--which may be variable. Also, it is important to note that when using direct addressing any instruction which refers to an address between 00h and 7Fh is referring to Internal Memory. Any instruction which refers to an address between 80h and FFh is referring to the SFR control registers that control the 8051 microcontroller itself. The obvious question that may arise is, "If direct addressing an address from 80h through FFh refers to SFRs, how can I access the upper 128 bytes of Internal RAM that are available on the 8052?" The answer is: You can’t access them using direct addressing. As stated, if you directly refer to an address of 80h through FFh you will be referring to an SFR. However, you may access the 8052s upper 128 bytes of RAM by using the next addressing mode, "indirect addressing." 3. Indirect Addressing Indirect addressing is a very powerful addressing mode which in many cases provides an exceptional level of flexibility. Indirect addressing is also the only way to access the extra 128 bytes of Internal RAM found on an 8052. Indirect addressing appears as follows: MOV A,@R0 This instruction causes the 8051 to analyze the value of the R0 register. The 8051 will then load the accumulator with the value from Internal RAM which is found at the address indicated by R0. For example, lets say R0 holds the value 40h and Internal RAM address 40h holds the value 67h. When the above instruction is executed the 8051 will check the value of R0. Since R0 holds 40h 25 the 8051 will get the value out of Internal RAM address 40h (which holds 67h) and store it in the Accumulator. Thus, the Accumulator ends up holding 67h. Indirect addressing always refers to Internal RAM; it never refers to an SFR. Thus, in a prior example we mentioned that SFR 99h can be used to write a value to the serial port. Thus one may think that the following would be a valid solution to write the value 1 to the serial port: MOV R0,#99h ;Load the address of the serial port MOV @R0,#01h ;Send 01 to the serial port -- WRONG!! This is not valid. Since indirect addressing always refers to Internal RAM these two instructions would write the value 01h to Internal RAM address 99h on an 8052. On an 8051 these two instructions would produce an undefined result since the 8051 only has 128 bytes of Internal RAM. 4. External Direct External Memory is accessed using a suite of instructions which use what I call "External Direct" addressing. I call it this because it appears to be direct addressing, but it is used to access external memory rather than internal memory. There are only two commands that use External Direct addressing mode: MOVX A,@DPTR MOVX @DPTR,A As you can see, both commands utilize DPTR. In these instructions, DPTR must first be loaded with the address of external memory that you wish to read or write. Once DPTR holds the correct external memory address, the first command will move the contents of that external memory address into the Accumulator. The second command will do the opposite: it will allow you to write the value of the Accumulator to the external memory address pointed to by DPTR. 5. External Indirect External memory can also be accessed using a form of indirect addressing which I call External Indirect addressing. This form of addressing is usually only used in relatively small projects that have a very small amount of external RAM. An example of this addressing mode is: MOVX @R0,A Once again, the value of R0 is first read and the value of the Accumulator is written to that address in External RAM. Since the value of @R0 can only be 00h through FFh the project would effectively be limited to 256 bytes of External RAM. There are relatively simple hardware/software tricks that can be implemented to access more than 256 bytes of memory using External Indirect addressing; however, it is usually easier to use External Direct addressing if your project has more than 256 bytes of External RAM. 26 2.11 Special Function Registers (SFRs): Special Function Registers (SFRs) are a sort of control table used for running and monitoring the operation of the microcontroller. Each of these registers as well as each bit they include, has its name, address in the scope of RAM and precisely defined purpose such as timer control, interrupt control, serial communication control etc. Even though there are 128 memory locations intended to be occupied by them, the basic core, shared by all types of 8051 microcontrollers, has only 21 such registers. Rest of locations are intensionally left unoccupied in order to enable the manufacturers to further develop microcontrollers keeping them compatible with the previous versions. It also enables programs written a long time ago for microcontrollers which are out of production now to be used today. 27 A Register (Accumulator) A register is a general-purpose register used for storing intermediate results obtained during operation. Prior to executing an instruction upon any number or operand it is necessary to store it in the accumulator first. All results obtained from arithmetical operations performed by the ALU are stored in the accumulator. Data to be moved from one register to another must go through the accumulator. In other words, the A register is the most commonly used register and it is impossible to imagine a microcontroller without it. More than half instructions used by the 8051 microcontroller use somehow the accumulator. B Register Multiplication and division can be performed only upon numbers stored in the A and B registers. All other instructions in the program can use this register as a spare accumulator (A). + R Registers (R0-R7) 28 This is a common name for 8 general-purpose registers (R0, R1, R2 ...R7). Even though they are not true SFRs, they deserve to be discussed here because of their purpose. They occupy 4 banks within RAM. Similar to the accumulator, they are used for temporary storing variables and intermediate results during operation. Which one of these banks is to be active depends on two bits of the PSW Register. Active bank is a bank the registers of which are currently used. The following example best illustrates the purpose of these registers. Suppose it is necessary to perform some arithmetical operations upon numbers previously stored in the R registers: (R1+R2) - (R3+R4). Obviously, a register for temporary storing results of addition is needed. This is how it looks in the program: MOV A,R3; Means: move number from R3 into accumulator ADD A,R4; Means: add number from R4 to accumulator (result remains in accumulator) MOV R5,A; Means: temporarily move the result from accumulator into R5 MOV A,R1; Means: move number from R1 to accumulator ADD A,R2; Means: add number from R2 to accumulator SUBB A,R5; Means: subtract number from R5 (there are R3+R4) Program Status Word (PSW) Register PSW register is one of the most important SFRs. It contains several status bits that reflect the current state of the CPU. Besides, this register contains Carry bit, Auxiliary Carry, two register bank select bits, Overflow flag, parity bit and user-definable status flag. P - Parity bit. If a number stored in the accumulator is even then this bit will be automatically set (1), otherwise it will be cleared (0). It is mainly used during data transmit and receive via serial communication. - Bit 1. This bit is intended to be used in the future versions of microcontrollers. OV Overflow occurs when the result of an arithmetical operation is larger than 255 and cannot be stored in one register. Overflow condition causes the OV bit to be set (1). Otherwise, it will be cleared (0). 29 RS0, RS1 - Register bank select bits. These two bits are used to select one of four register banks of RAM. By setting and clearing these bits, registers R0-R7 are stored in one of four banks of RAM. RS1 RS2 Space in RAM 0 0 Bank0 00h-07h 0 1 Bank1 08h-0Fh 1 0 Bank2 10h-17h 1 1 Bank3 18h-1Fh F0 - Flag 0. This is a general-purpose bit available for use. AC - Auxiliary Carry Flag is used for BCD operations only. CY - Carry Flag is the (ninth) auxiliary bit used for all arithmetical operations and shift instructions. Data Pointer Register (DPTR) DPTR register is not a true one because it doesn't physically exist. It consists of two separate registers: DPH (Data Pointer High) and (Data Pointer Low). For this reason it may be treated as a 16-bit register or as two independent 8-bit registers. Their 16 bits are primarly used for external memory addressing. Besides, the DPTR Register is usually used for storing data and intermediate results. 30 Stack Pointer (SP) Register A value stored in the Stack Pointer points to the first free stack address and permits stack availability. Stack pushes increment the value in the Stack Pointer by 1. Likewise, stack pops decrement its value by 1. Upon any reset and power-on, the value 7 is stored in the Stack Pointer, which means that the space of RAM reserved for the stack starts at this location. If another value is written to this register, the entire Stack is moved to the new memory location. P0, P1, P2, P3 - Input/output Registers If neither external memory nor serial communication system are used then 4 ports with in total of 32 input/output pins are available for connection to peripheral environment. Each bit within these 31 ports affects the state and performance of appropriate pin of the microcontroller. Thus, bit logic state is reflected on appropriate pin as a voltage (0 or 5 V) and vice versa, voltage on a pin reflects the state of appropriate port bit. As mentioned, port bit state affects performance of port pins, i.e. whether they will be configured as inputs or outputs. If a bit is cleared (0), the appropriate pin will be configured as an output, while if it is set (1), the appropriate pin will be configured as an input. Upon reset and power-on, all port bits are set (1), which means that all appropriate pins will be configured as inputs. 2.12 Counters and Timers: As you already know, the microcontroller oscillator uses quartz crystal for its operation. As the frequency of this oscillator is precisely defined and very stable, pulses it generates are always of the same width, which makes them ideal for time measurement. Such crystals are also used in quartz watches. In order to measure time between two events it is sufficient to count up pulses coming from this oscillator. That is exactly what the timer does. If the timer is properly programmed, the value stored in its register will be incremented (or decremented) with each coming pulse, i.e. once per each machine cycle. A single machine-cycle instruction lasts for 12 quartz oscillator periods, which means that by embedding quartz with oscillator frequency of 12MHz, a number stored in the timer register will be changed million times per second, i.e. each microsecond. The 8051 microcontroller has 2 timers/counters called T0 and T1. As their names suggest, their main purpose is to measure time and count external events. Besides, they can be used for generating clock pulses to be used in serial communication, so called Baud Rate. Timer T0 As seen in figure below, the timer T0 consists of two registers – TH0 and TL0 representing a low and a high byte of one 16-digit binary number. Accordingly, if the content of the timer T0 is equal to 0 (T0=0) then both registers it consists of will contain 0. If the timer contains for example number 1000 (decimal), then the TH0 register 32 (high byte) will contain the number 3, while the TL0 register (low byte) will contain decimal number 232. Formula used to calculate values in these two registers is very simple: TH0 × 256 + TL0 = T Matching the previous example it would be as follows: 3 × 256 + 232 = 1000 Since the timer T0 is virtually 16-bit register, the largest value it can store is 65 535. In case of exceeding this value, the timer will be automatically cleared and counting starts from 0. This condition is called an overflow. Two registers TMOD and TCON are closely connected to this timer and control its operation. TMOD Register (Timer Mode) The TMOD register selects the operational mode of the timers T0 and T1. As seen in figure below, the low 4 bits (bit0 - bit3) refer to the timer 0, while the high 4 bits (bit4 - bit7) refer to the timer 1. There are 4 operational modes and each of them is described herein. 33 Bits of this register have the following function: GATE1 enables and disables Timer 1 by means of a signal brought to the INT1 pin (P3.3): 1 - Timer 1 operates only if the INT1 bit is set. 0 - Timer 1 operates regardless of the logic state of the INT1 bit. C/T1 selects pulses to be counted up by the timer/counter 1: 1 - Timer counts pulses brought to the T1 pin (P3.5). 0 - Timer counts pulses from internal oscillator. T1M1,T1M0 These two bits select the operational mode of the Timer 1. T1M1 T1M0 Mode Description 0 0 0 13-bit timer 0 1 1 16-bit timer 1 0 2 8-bit auto-reload 1 1 3 Split mode GATE0 enables and disables Timer 1 using a signal brought to the INT0 pin (P3.2): 1 - Timer 0 operates only if the INT0 bit is set. 0 - Timer 0 operates regardless of the logic state of the INT0 bit. C/T0 selects pulses to be counted up by the timer/counter 0: 1 - Timer counts pulses brought to the T0 pin (P3.4). 0 - Timer counts pulses from internal oscillator. T0M1,T0M0 These two bits select the oprtaional mode of the Timer 0. 34 T0M1 T0M0 Mode Description 0 0 0 13-bit timer 0 1 1 16-bit timer 1 0 2 8-bit auto-reload 1 1 3 Split mode Timer 0 in mode 0 (13-bit timer) This is one of the rarities being kept only for the purpose of compatibility with the previuos versions of microcontrollers. This mode configures timer 0 as a 13-bit timer which consists of all 8 bits of TH0 and the lower 5 bits of TL0. As a result, the Timer 0 uses only 13 of 16 bits. How does it operate? Each coming pulse causes the lower register bits to change their states. After receiving 32 pulses, this register is loaded and automatically cleared, while the higher byte (TH0) is incremented by 1. This process is repeated until registers count up 8192 pulses. After that, both registers are cleared and counting starts from 0. Timer 0 in mode 1 (16-bit timer) Mode 1 configures timer 0 as a 16-bit timer comprising all the bits of both registers TH0 and TL0. That's why this is one of the most commonly used modes. Timer operates in the same way as in mode 0, with difference that the registers count up to 65 536 as allowable by the 16 bits. 35 Timer 0 in mode 2 (Auto-Reload Timer) Mode 2 configures timer 0 as an 8-bit timer. Actually, timer 0 uses only one 8-bit register for counting and never counts from 0, but from an arbitrary value (0-255) stored in another (TH0) register. The following example shows the advantages of this mode. Suppose it is necessary to constantly count up 55 pulses generated by the clock. If mode 1 or mode 0 is used, It is necessary to write the number 200 to the timer registers and constantly check whether an overflow has occured, i.e. whether they reached the value 255. When it happens, it is necessary to rewrite the number 200 and repeat the whole procedure. The same procedure is automatically performed by the microcontroller if set in mode 2. In fact, only the TL0 register operates as a timer, while another (TH0) register stores the value from which the counting starts. When the TL0 register is loaded, instead of being cleared, the contents of TH0 will be reloaded to it. Referring to the previous example, in order to register each 55th pulse, the best solution is to write the number 200 to the TH0 register and configure the timer to operate in mode 2. 36 Timer 0 in Mode 3 (Split Timer) Mode 3 configures timer 0 so that registers TL0 and TH0 operate as separate 8-bit timers. In other words, the 16-bit timer consisting of two registers TH0 and TL0 is split into two independent 8-bit timers. This mode is provided for applications requiring an additional 8-bit timer or counter. The TL0 timer turns into timer 0, while the TH0 timer turns into timer 1. In addition, all the control bits of 16-bit Timer 1 (consisting of the TH1 and TL1 register), now control the 8-bit Timer 1. Even though the 16-bit Timer 1 can still be configured to operate in any of modes (mode 1, 2 or 3), it is no longer possible to disable it as there is no control bit to do it. Thus, its operation is restricted when timer 0 is in mode 3. The only application of this mode is when two timers are used and the 16-bit Timer 1 the operation of which is out of control is used as a baud rate generator. Timer Control (TCON) Register TCON register is also one of the registers whose bits are directly in control of timer operation. Only 4 bits of this register are used for this purpose, while rest of them is used for interrupt control to be discussed later. TF1 bit is automatically set on the Timer 1 overflow. TR1 bit enables the Timer 1. 1 - Timer 1 is enabled. 37 0 - Timer 1 is disabled. TF0 bit is automatically set on the Timer 0 overflow. TR0 bit enables the timer 0. 1 - Timer 0 is enabled. 0 - Timer 0 is disabled. How to use the Timer 0 ? In order to use timer 0, it is first necessary to select it and configure the mode of its operation. Bits of the TMOD register are in control of it: Referring to figure above, the timer 0 operates in mode 1 and counts pulses generated by internal clock the frequency of which is equal to 1/12 the quartz frequency. Turn on the timer: The TR0 bit is set and the timer starts operation. If the quartz crystal with frequency of 12MHz is embedded then its contents will be incremented every microsecond. After 65.536 microseconds, the both registers the timer consists of will be loaded. The microcontroller automatically clears them and the timer keeps on repeating procedure from the beginning until the TR0 bit value is logic zero (0). 38 How to 'read' a timer? Depending on application, it is necessary either to read a number stored in the timer registers or to register the moment they have been cleared. - It is extremely simple to read a timer by using only one register configured in mode 2 or 3. It is sufficient to read its state at any moment. That's all! - It is somehow complicated to read a timer configured to operate in mode 2. Suppose the lower byte is read first (TL0), then the higher byte (TH0). The result is: TH0 = 15 TL0 = 255 Everything seems to be ok, but the current state of the register at the moment of reading was: TH0 = 14 TL0 = 255 In case of negligence, such an error in counting (255 pulses) may occur for not so obvious but quite logical reason. The lower byte is correctly read (255), but at the moment the program counter was about to read the higher byte TH0, an overflow occurred and the contents of both registers have been changed (TH0: 14→15, TL0: 255→0). This problem has a simple solution. The higher byte should be read first, then the lower byte and once again the higher byte. If the number stored in the higher byte is different then this sequence should be repeated. It's about a short loop consisting of only 3 instructions in the program. There is another solution as well. It is sufficient to simply turn the timer off while reading is going on (the TR0 bit of the TCON register should be cleared), and turn it on again after reading is finished. Timer 0 Overflow Detection Usually, there is no need to constantly read timer registers. It is sufficient to register the moment they are cleared, i.e. when counting starts from 0. This condition is called an overflow. When it occurrs, the TF0 bit of the TCON register will be automatically set. The state of this bit can be constantly checked from within the program or by enabling an interrupt which will stop the main program execution when this bit is set. Suppose it is necessary to provide a program delay of 0.05 seconds (50 000 machine cycles), i.e. time when the program seems to be stopped: First a number to be written to the timer registers should be calculated: 39 Then it should be written to the timer registers TH0 and TL0: When enabled, the timer will resume counting from this number. The state of the TF0 bit, i.e. whether it is set, is checked from within the program. It happens at the moment of overflow, i.e. after exactly 50.000 machine cycles or 0.05 seconds. How to measure pulse duration? Suppose it is necessary to measure the duration of an operation, for example how long a device has been turned on? Look again at the figure illustrating the timer and pay attention to the function of the GATE0 bit of the TMOD register. If it is cleared then the state of the P3.2 pin doesn't affect timer operation. If GATE0 = 1 the timer will operate until the pin P3.2 is cleared. Accordingly, if this pin is supplied with 5V through some external switch at the moment the 40 device is being turned on, the timer will measure duration of its operation, which actually was the objective. How to count up pulses? Similarly to the previous example, the answer to this question again lies in the TCON register. This time it's about the C/T0 bit. If the bit is cleared the timer counts pulses generated by the internal oscillator, i.e. measures the time passed. If the bit is set, the timer input is provided with pulses from the P3.4 pin (T0). Since these pulses are not always of the same width, the timer cannot be used for time measurement and is turned into a counter, therefore. The highest frequency that could be measured by such a counter is 1/24 frequency of used quartz-crystal. Timer 1 Timer 1 is identical to timer 0, except for mode 3 which is a hold-count mode. It means that they have the same function, their operation is controlled by the same registers TMOD and TCON and both of them can operate in one out of 4 different modes. 2.13 UART (Universal Asynchronous Receiver and Transmitter) One of the microcontroller features making it so powerful is an integrated UART, better known as a serial port. It is a full-duplex port, thus being able to transmit and receive data simultaneously and at different baud rates. Without it, serial data send and receive would be an enormously complicated part of the program in which the pin state is constantly changed and checked at regular intervals. When using UART, all the programmer has to do is to simply select serial port mode and baud rate. When it's done, serial data transmit is nothing but writing to the SBUF register, while data receive represents reading the same register. The microcontroller takes care of not making any error during data transmission. 41 Serial port must be configured prior to being used. In other words, it is necessary to determine how many bits is contained in one serial “word”, baud rate and synchronization clock source. The whole process is in control of the bits of the SCON register (Serial Control). Serial Port Control (SCON) Register SM0 - Serial port mode bit 0 is used for serial port mode selection. SM1 - Serial port mode bit 1. SM2 - Serial port mode 2 bit, also known as multiprocessor communication enable bit. When set, it enables multiprocessor communication in mode 2 and 3, and eventually mode 1. It should be cleared in mode 0. REN - Reception Enable bit enables serial reception when set. When cleared, serial reception is disabled. TB8 - Transmitter bit 8. Since all registers are 8-bit wide, this bit solves the problem of transmiting the 9th bit in modes 2 and 3. It is set to transmit a logic 1 in the 9th bit. RB8 - Receiver bit 8 or the 9th bit received in modes 2 and 3. Cleared by hardware if 9th bit received is a logic 0. Set by hardware if 9th bit received is a logic 1. TI - Transmit Interrupt flag is automatically set at the moment the last bit of one byte is sent. It's a signal to the processor that the line is available for a new byte transmite. It must be cleared from within the software. RI - Receive Interrupt flag is automatically set upon one byte receive. It signals that byte is received and should be read quickly prior to being replaced by a new data. This bit is also cleared from within the software. As seen, serial port mode is selected by combining the SM0 and SM2 bits: 42 SM0 SM1 Mode Description Baud Rate 0 0 0 8-bit Shift Register 1/12 the quartz frequency 0 1 1 8-bit UART Determined by the timer 1 1 0 2 9-bit UART 1/32 the quartz frequency (1/64 the quartz frequency) 1 1 3 9-bit UART Determined by the timer 1 In mode 0, serial data are transmitted and received through the RXD pin, while the TXD pin output clocks. The bout rate is fixed at 1/12 the oscillator frequency. On transmit, the least significant bit (LSB bit) is sent/received first. TRANSMIT - Data transmit is initiated by writing data to the SBUF register. In fact, this process starts after any instruction being performed upon this register. When all 8 bits have been sent, the TI bit of the SCON register is automatically set. 43 RECEIVE - Data receive through the RXD pin starts upon the two following conditions are met: bit REN=1 and RI=0 (both of them are stored in the SCON register). When all 8 bits have been received, the RI bit of the SCON register is automatically set indicating that one byte receive is complete. Since there are no START and STOP bits or any other bit except data sent from the SBUF register in the pulse sequence, this mode is mainly used when the distance between devices is short, noise is minimized and operating speed is of importance. A typical example is I/O port expansion by adding a cheap IC (shift registers 74HC595, 74HC597 and similar). Mode 1 In mode 1, 10 bits are transmitted through the TXD pin or received through the RXD pin in the following manner: a START bit (always 0), 8 data bits (LSB first) and a STOP bit (always 1). The START bit is only used to initiate data receive, while the STOP bit is automatically written to the RB8 bit of the SCON register. TRANSMIT - Data transmit is initiated by writing data to the SBUF register. End of data transmission is indicated by setting the TI bit of the SCON register. 44 RECEIVE - The START bit (logic zero (0)) on the RXD pin initiates data receive. The following two conditions must be met: bit REN=1 and bit RI=0. Both of them are stored in the SCON register. The RI bit is automatically set upon data reception is complete. The Baud rate in this mode is determined by the timer 1 overflow. Mode 2 In mode 2, 11 bits are transmitted through the TXD pin or received through the RXD pin: a START bit (always 0), 8 data bits (LSB first), a programmable 9th data bit and a STOP bit (always 1). On transmit, the 9th data bit is actually the TB8 bit of the SCON register. This bit usually has a function of parity bit. On receive, the 9th data bit goes into the RB8 bit of the same register (SCON).The baud rate is either 1/32 or 1/64 the oscillator frequency. TRANSMIT - Data transmit is initiated by writing data to the SBUF register. End of data transmission is indicated by setting the TI bit of the SCON register. RECEIVE - The START bit (logic zero (0)) on the RXD pin initiates data receive. The following two conditions must be met: bit REN=1 and bit RI=0. Both of them are stored in the SCON register. The RI bit is automatically set upon data reception is complete. 45 Mode 3 Mode 3 is the same as Mode 2 in all respects except the baud rate. The baud rate in Mode 3 is variable. Baud Rate Baud Rate is a number of sent/received bits per second. In case the UART is used, baud rate depends on: selected mode, oscillator frequency and in some cases on the state of the SMOD bit of the SCON register. All the necessary formulas are specified in the table: Baud Rate BitSMOD Mode 0 Fosc. / 12 Mode 1 1 Fosc. 16 12 (256-TH1) BitSMOD Mode 2 Fosc. / 32 Fosc. / 64 1 0 Mode 3 1 Fosc. 16 12 (256-TH1) Timer 1 as a clock generator Timer 1 is usually used as a clock generator as it enables various baud rates to be easily set. The whole procedure is simple and is as follows: First, enable Timer 1 overflow interrupt. Configure Timer T1 to operate in auto-reload mode. Depending on needs, select one of the standard values from the table and write it to the TH1 register. That's all. 46 Fosc. (MHz) Baud Rate Bit SMOD 11.0592 12 14.7456 150 40 h 30 h 00 h 300 A0 h 98 h 80 h 75 h 52 h 0 600 D0 h CC h C0 h BB h A9 h 0 1200 E8 h E6 h E0 h DE h D5 h 0 2400 F4 h F3 h F0 h EF h EA h 0 F3 h EF h EF h 4800 4800 FA h F8 h 9600 FD h FC h 20 0 1 F5 h F5 h FD h 0 0 9600 19200 16 1 FC h 1 38400 FE h 1 76800 FF h 1 2.14 8051 Microcontroller Interrupts: There are five interrupt sources for the 8051, which means that they can recognize 5 different events that can interrupt regular program execution. Each interrupt can be enabled or disabled by setting bits of the IE register. Likewise, the whole interrupt system can be disabled by clearing the EA bit of the same register. Refer to figure below. Now, it is necessary to explain a few details referring to external interrupts- INT0 and INT1. If the IT0 and IT1 bits of the TCON register are set, an interrupt will be generated on high to low 47 transition, i.e. on the falling pulse edge (only in that moment). If these bits are cleared, an interrupt will be continuously executed as far as the pins are held low. IE Register (Interrupt Enable) EA - global interrupt enable/disable: 0 - disables all interrupt requests. 1 - enables all individual interrupt requests. ES - enables or disables serial interrupt: 0 - UART system cannot generate an interrupt. 1 - UART system enables an interrupt. ET1 - bit enables or disables Timer 1 interrupt: 0 - Timer 1 cannot generate an interrupt. 1 - Timer 1 enables an interrupt. 48 EX1 - bit enables or disables external 1 interrupt: 0 - change of the pin INT0 logic state cannot generate an interrupt. 1 - enables an external interrupt on the pin INT0 state change. ET0 - bit enables or disables timer 0 interrupt: 0 - Timer 0 cannot generate an interrupt. 1 - enables timer 0 interrupt. EX0 - bit enables or disables external 0 interrupt: 0 - change of the INT1 pin logic state cannot generate an interrupt. 1 - enables an external interrupt on the pin INT1 state change. Interrupt Priorities It is not possible to foreseen when an interrupt request will arrive. If several interrupts are enabled, it may happen that while one of them is in progress, another one is requested. In order that the microcontroller knows whether to continue operation or meet a new interrupt request, there is a priority list instructing it what to do. The priority list offers 3 levels of interrupt priority: Reset! The absolute master. When a reset request arrives, everything is stopped and the microcontroller restarts. Interrupt priority 1 can be disabled by Reset only. Interrupt priority 0 can be disabled by both Reset and interrupt priority 1. The IP Register (Interrupt Priority Register) specifies which one of existing interrupt sources have higher and which one has lower priority. Interrupt priority is usually specified at the beginning of the program. According to that, there are several possibilities: If an interrupt of higher priority arrives while an interrupt is in progress, it will be immediately stopped and the higher priority interrupt will be executed first. If two interrupt requests, at different priority levels, arrive at the same time then the higher priority interrupt is serviced first. If the both interrupt requests, at the same priority level, occur one after another, the one which came later has to wait until routine being in progress ends. 49 If two interrupt requests of equal priority arrive at the same time then the interrupt to be serviced is selected according to the following priority list: External interrupt INT0 Timer 0 interrupt External Interrupt INT1 Timer 1 interrupt Serial Communication Interrupt IP Register (Interrupt Priority) The IP register bits specify the priority level of each interrupt (high or low priority). PS - Serial Port Interrupt priority bit Priority 0 Priority 1 PT1 - Timer 1 interrupt priority Priority 0 Priority 1 PX1 - External Interrupt INT1 priority Priority 0 Priority 1 PT0 - Timer 0 Interrupt Priority Priority 0 Priority 1 PX0 - External Interrupt INT0 Priority 50 Priority 0 Priority 1 Handling Interrupt When an interrupt request arrives the following occurs: Instruction in progress is ended. The address of the next instruction to execute is pushed on the stack. Depending on which interrupt is requested, one of 5 vectors (addresses) is written to the program counter in accordance to the table below: Interrupt Source Vector (address) IE0 3h TF0 Bh TF1 1B h RI, TI 23 h All addresses are in hexadecimal format These addresses store appropriate subroutines processing interrupts. Instead of them, there are usually jump instructions specifying locations on which these subroutines reside. When an interrupt routine is executed, the address of the next instruction to execute is poped from the stack to the program counter and interrupted program resumes operation from where it left off. Reset Reset occurs when the RS pin is supplied with a positive pulse in duration of at least 2 machine cycles (24 clock cycles of crystal oscillator). After that, the microcontroller generates an internal reset signal which clears all SFRs, except SBUF registers, Stack Pointer and ports (the state of the first two ports is not defined, while FF value is written to the ports configuring all their pins as inputs). Depending on surrounding and purpose of device, the RS pin is usually connected to a 51 power-on reset push button or circuit or to both of them. Figure below illustrates one of the simplest circuits providing safe power-on reset. Basically, everything is very simple: after turning the power on, electrical capacitor is being charged for several milliseconds through a resistor connected to the ground. The pin is driven high during this process. When the capacitor is charged, power supply voltage is already stable and the pin remains connected to the ground, thus providing normal operation of the microcontroller. Pressing the reset button causes the capacitor to be temporarily discharged and the microcontroller is reset. When released, the whole process is repeated… 2.15 8051 Microcontroller Power Consumption Control: Generally speaking, the microcontroller is inactive for the most part and just waits for some external signal in order to takes its role in a show. This can cause some problems in case batteries are used for power supply. In extreme cases, the only solution is to set the whole electronics in sleep mode in order to minimize consumption. A typical example is a TV remote controller: it can be out of use for months but when used again it takes less than a second to send a command to TV receiver. The AT89S53 uses approximately 25mA for regular operation, which doesn't make it a pover-saving microcontroller. Anyway, it doesn’t have to be always like that, it can easily switch the operating mode in order to reduce its total consumption to approximately 40uA. Actually, there are two power-saving modes of operation: Idle and Power Down. 52 Idle mode Upon the IDL bit of the PCON register is set, the microcontroller turns off the greatest power consumer- CPU unit while peripheral units such as serial port, timers and interrupt system continue operating normally consuming 6.5mA. In Idle mode, the state of all registers and I/O ports remains unchanged. In order to exit the Idle mode and make the microcontroller operate normally, it is necessary to enable and execute any interrupt or reset. It will cause the IDL bit to be automatically cleared and the program resumes operation from instruction having set the IDL bit. It is recommended that first three instructions to execute now are NOP instructions. They don't perform any operation but provide some time for the microcontroller to stabilize and prevents undesired changes on the I/O ports. Power Down mode By setting the PD bit of the PCON register from within the program, the microcontroller is set to Power down mode, thus turning off its internal oscillator and reduces power consumption enormously. The microcontroller can operate using only 2V power supply in power- down mode, 53 while a total power consumption is less than 40uA. The only way to get the microcontroller back to normal mode is by reset. While the microcontroller is in Power Down mode, the state of all SFR registers and I/O ports remains unchanged. By setting it back into the normal mode, the contents of the SFR register is lost, but the content of internal RAM is saved. Reset signal must be long enough, approximately 10mS, to enable stable operation of the quartz oscillator. PCON register The purpose of the Register PCON bits is: SMOD Baud rate is twice as much higher by setting this bit. GF1 General-purpose bit (available for use). GF1 General-purpose bit (available for use). GF0 General-purpose bit (available for use). PD By setting this bit the microcontroller enters the Power Down mode. IDL By setting this bit the microcontroller enters the Idle mode. 54 Model Questions Q.1 Compare between microprocessor and microcontroller. (Dec’2014, 4M) Q.2 Give comparison between 8051 microcontroller family. (Dec’2014, 5M) Q.3 Draw complete architecture of 8051 microcontroller and explain the use of all ports. (Dec’2014, 10M) Q.4 Draw format for following registers and explain the function of each bit. (any 2) (i) TCON Register (ii) SCON Register (iii) CCON Register (Dec’2014, 10M) Q.5 Draw the diagram to interface external RAM and ROM with 8051 microcontroller. Mention the pins during interfacing and describe in brief. (Dec’2014, 5M) Q.6 Differentiate between Timer and Counter operation of 8051. (May’2015, 4M) Q.7 Write features of 8051 Microcontroller. (May’2015, 4M) Q.8 Explain the memory organization in MCS-51 microcontroller. Describe TCON & SCON SFR’s. (May’2015, 10M) Q.9 Draw and explain addressing modes of 8051 with instruction example. (May’2015, 10M) Q.10 Explain the power saving and power down mode of 8051 in details. (May’2015, 10M) Q.11 Port structure of 8051. (May’2015, 10M) 55