DSP Files - Cognitive Radio Technologies

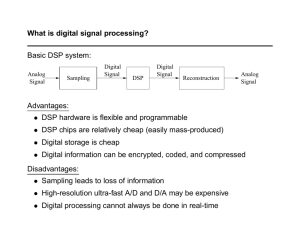

advertisement