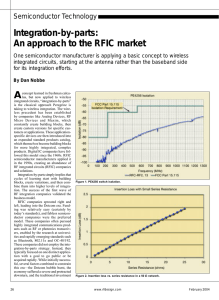

Lecture 13 – PROCESS INTEGRATION Chapters 15

advertisement

Lecture 13 – PROCESS INTEGRATION

Chapters 15 - 18 in Campbell

15 Device Isolation, Contacts, and Metallization

16 CMOS Technologies

17 Other Transistor Technologies (GaAs, Bipolar, …)

18 Optoelectronic Technologies

DEVICE ISOLATION

More than one component => Some device isolation needed

DEVICE ISOLATION

Isolation by reverse biased PN-junction:

-

Minimum distance between components?

(15.1)

-

Wd = { 2ksε0(Vbi + VCB) / qND } 1/2

(one-sided step junction)

Depletion layers should not meet at max operating voltage

DEVICE ISOLATION

Vt for parasitic surface channel

must be > max operating voltage

What happens at the

surface?

To improve isolation:

• Increase oxide

thickness

• Increase substrate

doping

Guard ring isolation

Effective but:

- Extra process steps

- Consumes area

LOCOS - Local Oxidation of Silicon

•

Selective growth of thick oxide between active components

TRENCH ISOLATION

Etch a trench to provide isolation

-

Deep or shallow depending on requirements

-

Add doping if needed to kill leakage

-

Fill trench with SiO2 and/or poly-Si

-

Planarize by etch-back or CMP (Chemical Mechanical Polishing)

CMP (CHEMICAL MECHANICAL POLISHING)

•

Chapter 11.2 in Campbell

•

CMP extensively used for planarization of multi-level interconnects

•

CMP also used to planarize after trench-fill for isolation

DEVICE ISOLATION

Isolation by using insulating substrate:

SOI - Silicon On Insulator

Thin Si layer (few um) on SiO2 on thick "handle" Si-wafer

GaAs:

Possible to make semi-insulating GaAs substrates

Active devices on mesas ("islands")

Use ion implantation (protons) to create damage

high resistance for device isolation

MESA ISOLATION

CONTACTS

Two types of contacts:

•

Schottky

Ideally "perfect" diode:

No leakage in reverse direction

Low resistance in forward direction

•

Ohmic

Ideally:

Linear I-V curve both directions

Low resistance

SCHOTTKY CONTACT

A low doped semiconductor + metal can form Schottky contact

Øm = Metal work function

Øs = Difference between Fermi level and vacuum level

N-type: Schottky if Øm > Øs

P-type: Schottky if Øm < Øs

Ideally: Barrier = | Øm - Øs |

Imperfections at interface => Effective barrier Øb

I = I0 {exp (qV/nkT) -1 }

I0 = RT2 A exp (- Øb/kT)

OHMIC CONTACTS

Highly doped semiconductor => Tunneling dominates

=> Ohmic contact (no diode)

•

Required doping approx 1018 - 1019 /cm3

•

Ion implantation or diffusion doping (Si)

•

Alloyed contacts (GaAs, other III-V)

METALLIZATION

(Interconnects)

Connect devices or bond pads

•

Low resistance

•

High packing density

Multi-level metallization

Planarization

Damascene process

ILD = Inter Level

Dielectric

32 nm technology, Intel, IEDM, Dec 2008

DEVICE TECHNOLOGIES

Chapters 16, 17, 18 in Campbell

CMOS and other silicon technologies

GaAs and opto devices

Moore's Law

CMOS future development

MOS = Metal Oxide Semiconducor

• NMOS = N-channel MOS, PMOS = P-channel MOS

CMOS = Complementary MOS

• CMOS process more complex but has lower power consumption =>

Now the dominant silicon technology (computers, mobiles, …)

• Current only flows during switching

Power ~ n x freq/2 x Cnode x V2swing

n = average number of gates switching

• MOS-transistor is a 4-terminal device

Source

Drain

Gate

Substrate

Basic 3 um CMOS process

Mask layers

1.

2.

3.

4.

5.

6.

7.

8.

9.

N-well

Active Area

P-minus (field implant)

Poly

P-plus

N-plus

Contact openings

Metal

Bond Pad openings

3 um CMOS process

3 um CMOS process

3 um CMOS process

3 um CMOS process

3 um CMOS process

CMOS – Device scaling

•

Constant field scaling

•

Constant voltage scaling

Main reasons for scaling:

•

Packing density

•

Speed

INTEL, 2014

Intel's 22nm technology

Vertical fins of tri-gate transistors passing through the gates

Silicon Bipolar Technologies

•

Simple Bipolars using ”CMOS-like” process

•

Reduce collector resistance by ”buried collector” (need epi-reactor)

•

Add poly-emitter to increase gain

•

BiCMOS process combines CMOS and Bipolar on same chip

Manufacturing of Ge-bipolar transistors (1961)

GaAs and other III – V technologies

•

No insulating oxide

•

MESFET => Schottky contact on gate

•

Can use semi-insulating high-resistivity substrate

•

High electron mobility => high speed devices

•

Direct bandgap => opto devices

VT= Vbi – qNdd2 / (2kGaAs ε0)

(17.1 & 17.2)