Charles Randall (Randy) Yates 600 Old Liverpool Drive Fuquay

advertisement

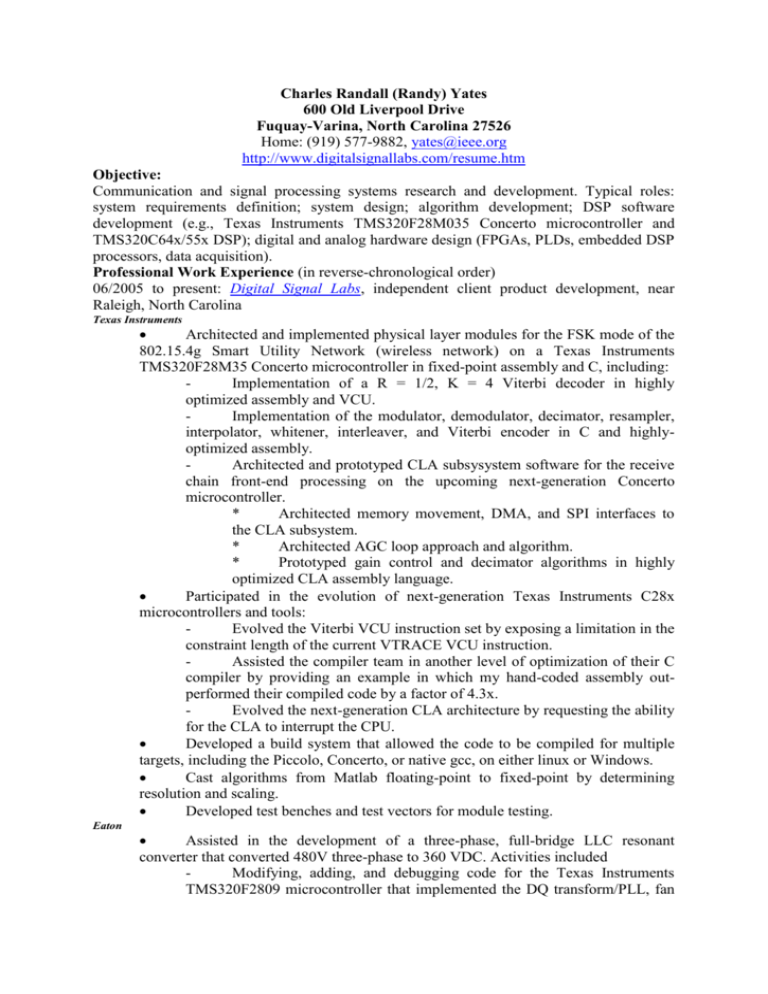

Charles Randall (Randy) Yates 600 Old Liverpool Drive Fuquay-Varina, North Carolina 27526 Home: (919) 577-9882, yates@ieee.org http://www.digitalsignallabs.com/resume.htm Objective: Communication and signal processing systems research and development. Typical roles: system requirements definition; system design; algorithm development; DSP software development (e.g., Texas Instruments TMS320F28M035 Concerto microcontroller and TMS320C64x/55x DSP); digital and analog hardware design (FPGAs, PLDs, embedded DSP processors, data acquisition). Professional Work Experience (in reverse-chronological order) 06/2005 to present: Digital Signal Labs, independent client product development, near Raleigh, North Carolina Texas Instruments Architected and implemented physical layer modules for the FSK mode of the 802.15.4g Smart Utility Network (wireless network) on a Texas Instruments TMS320F28M35 Concerto microcontroller in fixed-point assembly and C, including: Implementation of a R = 1/2, K = 4 Viterbi decoder in highly optimized assembly and VCU. Implementation of the modulator, demodulator, decimator, resampler, interpolator, whitener, interleaver, and Viterbi encoder in C and highlyoptimized assembly. Architected and prototyped CLA subsysystem software for the receive chain front-end processing on the upcoming next-generation Concerto microcontroller. * Architected memory movement, DMA, and SPI interfaces to the CLA subsystem. * Architected AGC loop approach and algorithm. * Prototyped gain control and decimator algorithms in highly optimized CLA assembly language. Participated in the evolution of next-generation Texas Instruments C28x microcontrollers and tools: Evolved the Viterbi VCU instruction set by exposing a limitation in the constraint length of the current VTRACE VCU instruction. Assisted the compiler team in another level of optimization of their C compiler by providing an example in which my hand-coded assembly outperformed their compiled code by a factor of 4.3x. Evolved the next-generation CLA architecture by requesting the ability for the CLA to interrupt the CPU. Developed a build system that allowed the code to be compiled for multiple targets, including the Piccolo, Concerto, or native gcc, on either linux or Windows. Cast algorithms from Matlab floating-point to fixed-point by determining resolution and scaling. Developed test benches and test vectors for module testing. Eaton Assisted in the development of a three-phase, full-bridge LLC resonant converter that converted 480V three-phase to 360 VDC. Activities included Modifying, adding, and debugging code for the Texas Instruments TMS320F2809 microcontroller that implemented the DQ transform/PLL, fan control, and a service interface. Mathematically analyzing the DQ transform and its use in the PLL for the system. Designing the controller using Matlab and loop analysis data and the frequency-domain least squares (FDLS) algorithm to model the plant, and scaling and implementing the controller coefficients in the DSP and FPGA. Updating schematics and generating BOMs using Altium Designer, and overseeing the CCA layout and fabrication. Hardware testing of the new boards designed in the previous item. Vadum, Inc. Created a DSP/BIOS framework consisting of dynamic tasks, semaphores, mailboxes, and a custom FAT16 device driver for the Texas Instruments TMS320C6418 digital signal processor to perform FMCW radar data acquisition and processing, including the implementation of Bayesian and neural network detection algorithms. Also aided in the test and debug of a Xilinx Spartan 3E 1600 FPGA using Xilinx’s ISE/Webpack that performed mixing, CIC decimation, and FIR filtering for the same system. Implemented a Bayesian detection algorithm under the TI TMS320C6418 and Cygwin/Windows XP (dual target build) in fixed-point C. Parrotworks (private) Created a speex-to-swf conversion library under linux/cygwin.s Developed a small wireless application prototype based on the TI MSP430 MCU, Chipcom CC25xx/CC11xx transceivers, and SimpliciTI network protocol. Digital Signal Labs Developed tutorial on basic coding theory, including the concepts of block codes, systematic codes, the generator and syndrome matrices, Hamming distance, and coding gain. (private) (private) (private) Developed algorithm to segment UPC-A barcodes in Matlab and C. Developed algorithms to estimate heart and breath rate from stethoscope audio. System engineered a wireless digital picture frame based on TI’s SimpliciTI and the MSP430FG4618 MCU, CC2500 RF Transceiver, the ARM 922T, and embedded linux. Analyzed potential modulation, bandwidth, and power for a three-dimensional location and tracking system. Digital Audio Corporation Ported a Voice Activity Detector from the x86 platform and Intel’s Integrated Performance Primitives to the SHARC 21369 and TigerSHARC TS201 DSPs and their DSP libraries using Analog Devices’ VisualDSP development environment. Tagent AWID Reviewed the system design of a UWB-based RFID system, including the demodulator design, method of error correction, and detection method. Developed receiver, transmitter, and analysis algorithms at the high level algorithm specification level for an RFID tag reader. The receiver algorithm included a carrier-locked loop, baud-locked loop (via a digital resampler), and matched filter detector. The high level algorithm specification level involved modeling the algorithm mathematically and proposing a fixed-point implementation architecture. Developed a C simulation of the modulation (ASK - Amplitude Shift Keyed) generated by RFID tags along with some common impairments. Modulus Video (now Motorola) Developed an all-digital, all-software BTSC audio decoder for broadcast television/satellite. The development included high-level algorithm design and software implementation in fixed-point C and, in a few cases, highly-optimized assembly using the Pentium SSE (SIMD Streaming Extensions) extensions. The decoder algorithm included a digitally-synthesized phase-locked loop (to acquire pilot lock), FM demodulator, DSB-SC demodulator, quadrature bandpass decimators, frequency-dependent dynamic range expansion, etc. Integrian Created a C++ API layer for the host interface to Ingenient’s video and audio codec framework. Modified video and audio port device drivers, performed system test and debug, ported to TI CCS Studio 3.1 tools, and developed a make environment for a video collection system based on the TI TMS320DM642 DSP and DSP/BIOS operating system and Ingenient’s MPEG4 and MPEG2 video and audio codec framework. 10/2001 to 6/2005: Sony Ericsson, Wireless Handset Development, Research Triangle Park, North Carolina Specified, simulated in C, implemented (in assembly language), and integrated a DC block filter on the Ceva-Teak DSP. Created a new bumblebee filter algorithm for the audio uplink in GSM using Matlab and C. Researched acoustic ranging algorithms based on MLS sequences. Conceived, designed, simulated, and implemented a software delta sigma D/A converter. Simulations were performed using Matlab and fixed-point C. Implementation was in highly optimized TI TMS320C54x assembly. Performed system specification and design of a MIDI subsystem (host interface, synthesis, gain control, equalization, D/A conversion, etc.) based on the TMS320C54x. Implemented various patches on a TMS320C54x to implement bug fixes and new functionality for assorted GSM audio functions. Developed algorithm to synchronize to MIDI events (patent pending). Created a test environment to verify bit-exactness of the GSM AMR vocoders. 5/2000 to 10/2001: Ericsson, Wireless Handset Development, Research Triangle Park, North Carolina 11/1998 to 5/2000: Aerotek (for Ericsson) Profiled and optimized CTM code in C for a GSM system. Researched FCH detection and frequency-offset estimation algorithms for a GSM system using Matlab; implemented the algorithm in fixed-point C on the TI TMS320C5510 DSP. Integrated hardware and software of embedded DSP and ARM7 processors for EDGE and GSM phones. Participated in the translation of existing embedded DSP code to the TI DSP/BIOS II real-time operating system (RTOS) on the TMS320C5510 for a GSM/EDGE cellular application. Researched convolutional coders and began design of a Viterbi decoder in C. Created a new algorithm for frequency offset estimation in very low SNR conditions within an analog mobile channel using Matlab and implemented it on a TMS320C54x in highly optimized assembler. Ported a Manchester-encoded, binary frequency-shift-keyed (FSK) demodulator from fixed-point assembly language on the Texas Instruments TMS320C54x digital signal processor to fixed-point C on the DSP Group OakDSP digital signal processor as part of an AMPS TIA/EIA 553 mobile communication system. Created Matlab M-files to simulate FSK data and test the FSK demodulator described above. Used Rational’s Rose to perform software modeling. Used Clearcase for configuration management. 01/1998 to 10/1998: Aerotek (for GEC-Marconi Hazeltine), Inertial Measurement Group, Wayne, New Jersey Implementation of fixed-point inertial measurement algorithms in highly optimized assembly language on the Texas Instruments TMS320C50 digital signal processor in real-time embedded systems. Scaling and overflow analysis of fixed-point algorithms. Analysis and optimization of inertial system algorithm performance using Matlab. Development of benchmark algorithms for the Texas Instruments TMS320C548 and TMS320C50 digital signal processors. 05/1997 to 12/1997: Florida Atlantic University, Sonar group, Department of Ocean Engineering, Boca Raton, Florida Analog hardware design of a 16-channel very low noise hydrophone transducer preamplifier. Analog hardware design of a low noise, gain-controlled front-end for a 16channel delta-sigma A/D. TMS320C32 DSP software development in C for an acoustic modem. Hardware development of an acoustic modem. 07/1994 to 06/2005: Yates Engineering Services Numerous database development projects. 05/1989 to 08/1991: Applied Signal Technology, Sunnyvale, California Windows 3.0 and C software development of user interface for high speed TDMA demodulator (modem). System engineering and algorithm development for high speed TDMA demodulator. FDDI token-ring network card hardware design. 06/1988 to 05/1989: Digital Sound Labs, San Jose, California Hardware design of 4 oversampling, 18-bit D/A converter for use with digital audio equipment. DOS/C software development of signal processing applications, e.g., FFT (Fast Fourier Transform), power spectral density estimator, Kalman filter, and random number generators. Audio signal processing research: inverse filtering of room/speaker responses; interaural crosstalk cancellation; loudspeaker binaural processing; delta-sigma data converters. 06/1979 to 06/1988: GTE Government Systems, Mountain View, California Digital hardware design of satellite tracking system components (numerous projects). Real-time, embedded microprocessor software (firmware) design (numerous projects). Complete design of a built-in test subsystem for a satellite tracking system. Satellite tracking system test, integration, and overseas installations (numerous projects). Education: Graduate coursework in digital communication, DSP, and math, 2003-2008, North Carolina State University BA Math, December 2001, University of South Florida, Tampa, Florida BSEE, May 1997, University of South Florida, Tampa, Florida BSEET, June 1979, DeVry Institute of Technology, Atlanta, Georgia and Phoenix, Arizona Skills: Digital Communications/DSP Analysis and Design Techniques: fixed-point scaling and overflow analyses, FIR/IIR filters, FFTs, Viterbi decoders, convolutional codes, block codes, Kalman filters, noise-shaping, adaptive equalization, TDMA/FDMA access techniques, BPSK/QPSK/8PSK, FSK/MSK/GMSK, and 16QAM/64-QAM/256-QAM modulation formats, CLL/BLL loops, I/Q signaling, quadrature downconversion, direct-digital synthesis (DDS). Programming Languages: C++, C, 80x86 assembler and SSE2 extensions, Texas Instruments C Compilers for TMS320DM642, TMS320C55x, TMS320C54x, TMS320C5x and TMS320C3x DSPs, a little TMS320DM642 assembly, TMS32055x assembly, TMS320C54x assembly, TMS320C50 assembly, TMS320C32 assembly, BASIC (assorted flavors), FORTRAN, Intel PL/M, 8748 assembler, 8085 assembler. Hardware Development Tools: Cadence, Mentor, OrCAD, Accel 13.0 EDA, Intel PLDShell. Hardware Design: 180 micron CMOS analog simulation, Xilinx FPGAs, PALASM/PLD design, multilayer circuit board design, in-ciruit emulators, logic analyzers, oscilloscopes, spectrum analyzers, RF/IF troubleshooting, wire-wrap, solder. Software Development and Simulation Tools: Analog Devices VisualDSP, TI Code Composer Studio (CCS) 3.1, MATLAB, MathCAD, Rational Rose, Clearcase, GNU toolchain (compiler, make, etc.), ddd debugger, yasm assembler, cygwin unixlike tools, TI code generation tools (assembler, compiler, linker) and JTAG emulator/simulator/debugger for TMS320C55x, TMS320C54x, TMS320C32, TMS320C5x, TMS320C2x, TMS320C64x, CEVA’s Teak and Oak code generation tools and JTAG emulator/simulator/debugger, Microsoft Access. Platforms/operating systems: TI DSP/BIOS, unix/linux (Solaris, Fedora, Ubuntu, cygwin), MS Windows, DEC VAX/VMS, Intel ISIS-II. Workshops, Conferences, Seminars: July 2004, First Annual comp.dsp Conference, Cannon Falls, Minnesota April 2000, DSPWorld, San Jose, California. November 1998, AES Convention, San Francisco, California. May 1998, Wavelet Workshop, Gil Strang and Truong Nguyen, Wellesley College, Massachussetts. Papers and Publications: Randy Yates, A Coding Theory Tutorial Randy Yates, Fixed-Point Arithmetic: An Introduction Randy Yates, Practical Considerations in Fixed-Point FIR Filter Implementations Randy Yates, Richard Lyons, DC Blocker Algorithms, IEEE Signal Processing Magazine “Tips and Tricks” column, March 2008 Richard Lyons, Randy Yates, Reducing ADC Quantization Noise, Microwaves and RF Magazine, June 2005 Charles R. Yates and Eric Sowers, Nordstrom-Robinson Error Correction Decoder, IEEE SECON 1996 (Tampa, FL). (A zipped postscript version, 273 kB, is available here.) Professional Associations: Audio Engineering Society IEEE Communications Society Information Theory Society Signal Processing Society Hobbies and Interests: Piano (Weber 5’7 baby grand)) Audio Signal Processing Last updated: 08–May–2012