Document

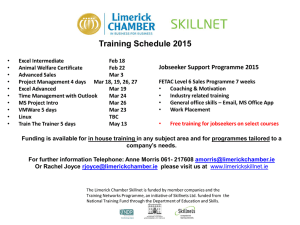

advertisement

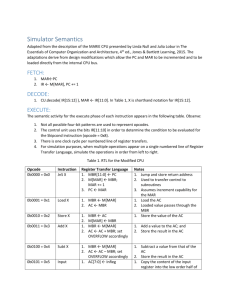

Assignment 2 Computer Organization and Software COEN 311 Some of the solutions are here. The rest are similar. Problem 1) a) Write an assembly program, for a GPR machine having 8 general purpose registers (R1,...,R7), to evaluate the following expression. Ignore the remainder part of the division process. ( (a + b) / (a + d) ) * (a * e) where a,b,d,e are variables with addresses A,B,D,E respectively, and each operation is defined as follows: + --------> ADD Ri, Rj ( Rj <- Ri + Rj) * --------> MULT Ri, Rj ( Rj <- Ri * Rj) / --------> DIV Ri, Rj ( Rj <- Rj / Ri) a = M[A] ------> content of memory location at address A. same for B, D, E. move A, D0 move B, D4 add D0, D4 move D, D1 add D0, D1 div D1,D4 move E, D2 mult D0, D2 mult D4, D2 ; D0 = a ; D4 = b ; D4 = a + b ; D1 = d ; D1 = a + d ; D4 = (a + b) / (a + d) ; D2 = e ; D2 = (a * e) ; D2 = ( (a + b) / (a + d) ) * (a * e) b) Evaluate the same expression on an Accumulator architecture. Conclude. 1/5 Problem 2) a) Provide micro-instructions in the form of detailed flowchart for the execution of the following instructions. b) Show the flow of the micro-instructions within the GPR architecture by highlighting the system buses and the registers used. i) ii) iii) iv) move X, D0 ; move contents of memory location X to register D0 move D0, X ; move contents of register D0 to memory location X movea 22(a3),25(a1) ; move contents from memory to memory bgt.w label ; branch if greater than to location “label” Answer 2) For each of the above, for part b), draw the CPU consisting of all the registers (for example MAR, MBR, PC, IR, Address and Data Registers, ALU) and Memory, and show each of the micro-instruction as in part a). i) move X, D0 Machine Instruction: 0011 0000 0011 1000 Address of X a) Micro-steps are: MAR <-- PC MBR <-- M[MAR] IR <-- MBR | decode | PC <-- PC + 2 MAR <-- PC MBR <-- M[MAR] MAR MBR MBR M[MAR] D0 MBR PC <-- PC + 2 ; fetch ; PC points to source address ; address of X in MBR ; move X to MAR ; read contents of location X ; ; PC points to next instruction ii) move D0, X Machine Instruction: 0011 1110 0000 0000 Address of X 2/5 a) Micro-steps are: MAR <-- PC MBR <-- M[MAR] IR <-- MBR | decode | PC <-- PC + 2 MAR <-- PC MBR M[MAR] MAR MBR MBR D0 M[MAR] MBR PC <-- PC + 2 ; fetch ; PC points to destination address ; read destination address X ; MAR has X now ; source data in MBR ; data in Effective address X (which is in MAR) ; PC points to next instruction iii) movea 22(a3),25(a1) Machine Instruction: 0011 0011 0110 1011 0000 0000 0001 0110 0000 0000 0001 1001 a) Source Effective address = contents of a3 + $16 temp <--- M[a3 + $16] Destination Effective address = contents of a1 + $19 M[a1 + $19] <- temp Micro-steps are: MAR <-- PC MBR <-- M[MAR] ; fetch IR <-- MBR | decode | PC <-- PC + 2 ; PC points to source displacement MAR <-- PC MBR <-- M[MAR] ; source displacement loaded MAR <-- [A3 + MBR] ; source effective address calculated MBR <- M[MAR] ; source data in MBR WR <- MBR ; saved temporarily since MBR is to be reused PC <-- PC + 2 ; PC points to destination displacement MAR <-- PC MBR <-- M[MAR] ; destination displacement loaded 3/5 MAR <-- [A1 + MBR] ; destination effective address calculated MBR <- WR ; source data back to MBR M[MAR] <-- MBR ; source data moved to destination PC <-- PC + 2 ; PC points to next instruction iv) bgt.w label Machine Instruction: 0110 1110 0000 0000 ---- displacement ---- a) MAR <-- PC MBR <-- M[MAR] IR <-- MBR | interpret | fetch decode TRUE | PC <-- PC + 2 MAR <-- PC MBR <-- M[MAR] ; get displacement PC <-- PC + MBR ; execute FALSE | PC <- PC + 4 Problem 3) Given the following assembly program P for GPR Processor: 1. Move X, R1 2. Move Y, R2 3. Add R1, R2 4. Move Z, R3 5. Mul R2, R3 6. Move X, R1 7. Add R1, R3 8. Move R3, L a) What is this program doing? b) Draw flowcharts showing the micro-step execution for each of the instructions 1, 3, 5 and 8. c) Calculate the execution times of instructions 1, 3, 5 and 8 assuming: Micro-step Register Transfer Number of clock cycles (cc) 1 4/5 Decoding Add Execution Multiply Execution Memory Access 2 2 5 10 Instruction 1 micro-instructions are same as in Problem 2 i). MAR <-- PC ; 1 cc MBR <-- M[MAR] ; 10 cc IR <-- MBR ; 1 cc | Decode ; 2 cc | PC <-- PC + 2 ; 2 cc MAR <-- PC ; 1 cc MBR <-- M[MAR] ; 10 cc D0 MBR ; 1 cc PC <-- PC + 2 ; 2 cc _______ Total Clock cycles: 30 cc d) Calculate the total execution time for the whole program P. e) Rewrite program P using Accumulator architecture. f) Calculate the total time needed for the new program P′ on the Accumulator architecture. g) Compare both P and P′, assuming they have the same clock speed. 5/5