SOLUTIONS: ECE 306 Midterm Exam

advertisement

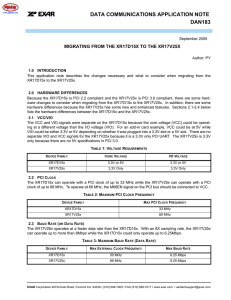

ECE306 Fall 2006 Test 2 Name ________________________________ IES Test 2 Solutions For questions 1 through 5 only, consider a faulty C start-up module (ncrt0) which does not initialize the stack pointer before calling main, instead leaving it at its default reset value of 0x0000. 1. Can code in main read and write global variables? c. Sometimes – It depends. a. Yes, always b. No, never 2. Can code in main read and write automatic local variables? a. Yes, always c. Sometimes – It depends. b. No, never 3. Can code in main read and write static local variables? c. Sometimes – It depends. a. Yes, always b. No, never 4. Can code in main successfully call and return from subroutines? a. Yes, always c. Sometimes – It depends. b. No, never 5. Can ISRs successfully be executed, letting main continue execution correctly? a. Yes, always c. Sometimes – It depends. b. No, never 6. Does the C start-up module need to initialize the static base pointer? b. No a. Yes 7. How does the C start-up module need to initialize the stack section? a. Fill with zeroes. c. Leave uninitialized. b. Fill with data from ROM. d. None of the above. 8. How does the C start-up module need to initialize the data section? a. Fill with zeroes. c. Leave uninitialized. d. None of the above. b. Fill with data from ROM. 9. How does the C start-up module need to initialize the bss section? c. Leave uninitialized. a. Fill with zeroes. b. Fill with data from ROM. d. None of the above. 10. Which of the following factors will not affect the delay between an interrupt request and the M30260 processor’s execution of the first instruction of the ISR? a. Whether another ISR is running. b. Whether a long (slow) instruction is executing when the interrupt is requested. c. Whether the I bit in the Flag register is set or not. d. Whether the interrupt vector points to _dummy_ISR or not. Page 1 of 4 ECE306 Fall 2006 Test 2 Name ________________________________ The following questions concern what the processor does wrong if an interrupt is requested but sect30_26askp.inc has not been changed. 11. The processor ignores the interrupt since it doesn’t know where to go. a. True b. False 12. The processor doesn’t save the data and address registers properly. a. True b. False 13. The processor doesn’t save the return address properly. a. True b. False 14. The processor doesn’t save the flag register properly. a. True b. False The following five questions concern what the processor does wrong if it tries to execute an interrupt service routine which hasn’t been identified with a #pragma INTERRUPT directive. 15. The processor ignores the interrupt since it doesn’t know the routine is supposed to be the ISR. a. True b. False 16. The processor returns to what it thinks is the return address but which really isn’t. b. False a. True 17. The processor calls the interrupt service routine but doesn’t save the data and address registers properly. b. False a. True 18. The processor doesn’t save the flag register properly. a. True b. False 19. The processor doesn’t save the return address properly. a. True b. False 20. Which of the following is not a potential clock source for an M16C timer peripheral? a. System clock c. Overflow output of another timer b. External pin d. Gate input 21. We wish to use an M16C timer peripheral to measure elapsed time. Which mode should we use? a. PWM d. One shot e. None of the above b. Timer c. Counter 22. With what period will a 16-bit timer overflow if the CPU clock is 13 MHz and it is prescaled by 32 before being used by the timer? a. 76.9 ns c. 5.04 ms d. 161.3 ms b. 2.46 s 23. How often will a 16-bit timer increment or decrement if the CPU clock is 13 MHz and it is prescaled by 32 before being used by the timer? a. every 76.9 ns c. every 5.04 ms d. every 161.3 ms b. every 2.46 s Page 2 of 4 ECE306 Fall 2004 Final Exam Name ________________________________ 24. Will a timer count if its overflow interrupt is not enabled? b. No a. Yes 25. Consider a 0 to 5 Volt PWM signal with a frequency of 1000 Hz. How long should the output be high to achieve a 33% duty cycle? a. 1 s d. 1000 s e. None of the above b. 33 s c. 330 s 26. Assume that an M30260 microcontroller (just like on your QSK) has a system clock runs at 20.06 MHz and we wish to run a serial communication link at 1031 baud. What is the proper value for the BRG (baud rate generator) in order to minimize the frequency error? Assume the selected clock source is f1SIO (system clock divided by 1). a. 1215 c. 1217 b. 1216 d. None of the above 27. Assume that an M30260 microcontroller (just like on your QSK) has a system clock runs at 20.06 MHz and we wish to run a serial communication link at 1031 baud. What is the proper value for the BRG (baud rate generator) in order to minimize the frequency error? Assume the selected clock source is f8SIO (system clock divided by 8). a. 150 c. 152 d. None of the above b. 151 28. Assume that an M30260 microcontroller’s system clock runs at 15 MHz and we wish to run a serial communication link at 60000 baud. What is the actual communication speed? a. 60000 baud d. 55147.06 baud b. 62500 baud e. none of the above c. 58593.75 baud 29. What should the parity bit value be for data byte 0x3f if we want even parity? b. 1 c. ½ a. 0 d. X 30. What voltage levels would you expect to see on an RS232 interface (e.g., a COM port from your PC)? a. 0 and 3.3 V d. -3 to -20 and 3 to 20 V b. 0 and 5 V e. 5 and 12 V c. 0 and 13.8 V 31. What voltage levels would you expect to see on the microcontroller’s TxD and RxD pins in your QSK26A? a. 0 and 3.3 V d. -3 to -20 and 3 to 20 V e. 5 and 12 V b. 0 and 5 V c. 0 and 13.8 V 3 Name ___________________________________________ 32. What data does the following serial waveform represent, assuming the M30260 MCU’s UART is configured for 38400 baud, even parity, eight data bits and two stop bits? Voltage 6 5 4 3 2 1 0 -6 0E 0. 40 - 6 0E 5. 37 - 6 0E 0. 35 - 6 0E 5. 32 - 6 0E 0. 30 - 6 0E 5. 27 - 6 0E 0. 25 - 6 0E 5. 22 - 6 0E 0. 20 - 6 0E 5. 17 - 6 0E 0. 15 - 6 0E 5. 12 - 6 0E 0. 10 6 E.0 75 6 E.0 50 6 E.0 25 +0 0E 0. 00 Time (seconds) a. 0xcd b. 0xce c. 0x77 d. 0xb9 e. None of the above 33. Consider the finite state machine from the lab 2 skeleton code (FSM demonstration). What is the processor doing during a transition from one state to another (e.g. during the interstate delay)? a. Executing TA0_ISR() d. Sitting in the HALT state e. Executing dummy_isr b. Executing main() c. Executing quick_delay() 34. Recall that Lab 2’s timer ISR uses an automatic state variable declared inside the ISR as static int cur_state = 0;. What would happen if we deleted the static keyword? a. No change. The code would work c. The code wouldn’t work fine. because it wouldn’t get out of b. The code would work fine, but state 0. run a little slower. d. None of the above. 35. Recall that Lab 2 uses an FSM and timer (with ISR) to eliminate the busy-waiting of quick_delay(). Is it possible to break up any states in Lab 2 to eliminate more busy-waiting? a. Yes – any state with more than 15 c. Yes – any state with digital input lines of code. or output. d. No b. Yes – any state with analog to digital conversion. Page 4 of 4