VLSI 2014 HW4

advertisement

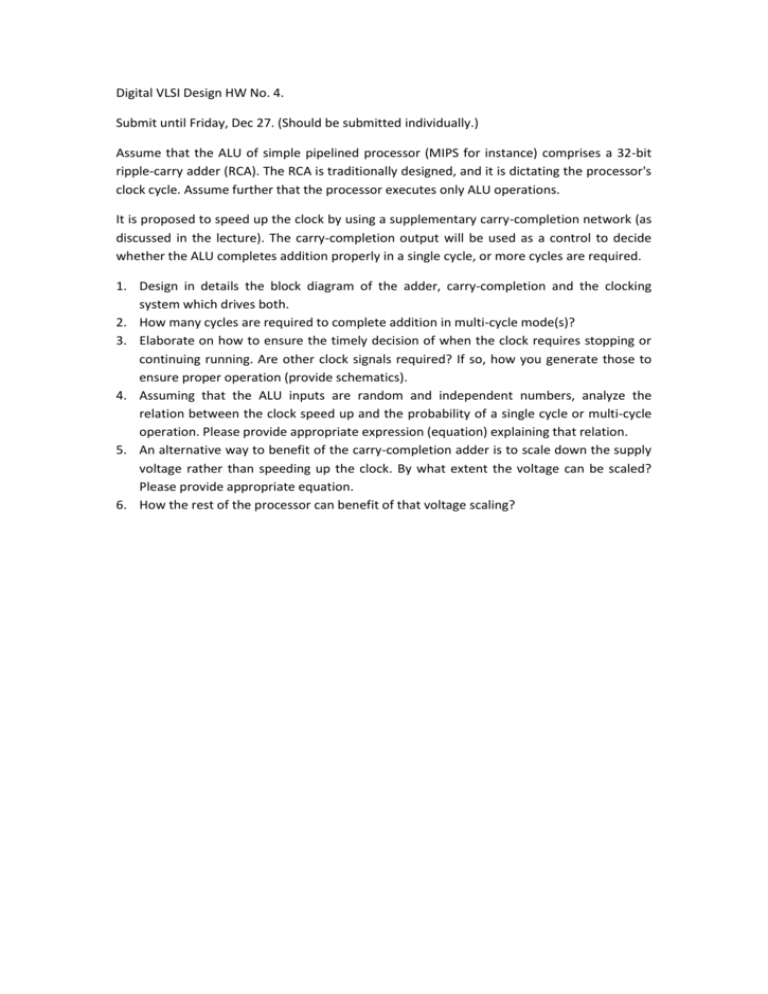

Digital VLSI Design HW No. 4. Submit until Friday, Dec 27. (Should be submitted individually.) Assume that the ALU of simple pipelined processor (MIPS for instance) comprises a 32-bit ripple-carry adder (RCA). The RCA is traditionally designed, and it is dictating the processor's clock cycle. Assume further that the processor executes only ALU operations. It is proposed to speed up the clock by using a supplementary carry-completion network (as discussed in the lecture). The carry-completion output will be used as a control to decide whether the ALU completes addition properly in a single cycle, or more cycles are required. 1. Design in details the block diagram of the adder, carry-completion and the clocking system which drives both. 2. How many cycles are required to complete addition in multi-cycle mode(s)? 3. Elaborate on how to ensure the timely decision of when the clock requires stopping or continuing running. Are other clock signals required? If so, how you generate those to ensure proper operation (provide schematics). 4. Assuming that the ALU inputs are random and independent numbers, analyze the relation between the clock speed up and the probability of a single cycle or multi-cycle operation. Please provide appropriate expression (equation) explaining that relation. 5. An alternative way to benefit of the carry-completion adder is to scale down the supply voltage rather than speeding up the clock. By what extent the voltage can be scaled? Please provide appropriate equation. 6. How the rest of the processor can benefit of that voltage scaling?