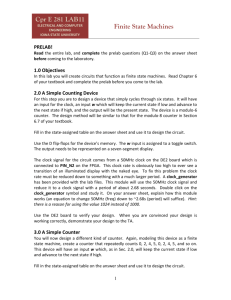

Modified Sequence Counter

advertisement

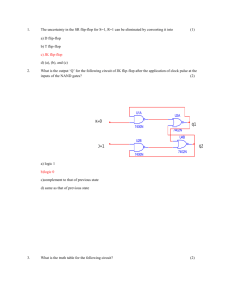

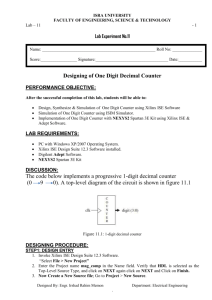

5 4 3 2 1 EGR 270 Fundamentals of Computer Engineering File: Modseq.opj Modified Sequence Counter D Purpose: A counter has been designed to count in the sequence 0, 2, 1, 3, 7, 5, 6, and repeat using JK flip-flops and the excitation table method. See the attached sheet for the details of the design. D A Digital Clock was used to generate a 1kHz input to clock the counter. Additionally, PSPICE requires that synchronous devices be initialized, so another Digital Clock is used to briefly provide a LOW pulse to initialize the counter to 3 (use ClearA, Preset B, and PresetC to preset to 011). The unused Preset and Clear lines must be tied HIGH. Analysis: A TRANSIENT analysis with a final time of 10ms is used to show ten output counts since the period of the clock is 1ms (1/1kHz). Note: The HI input is available by pressing the GND icon on the toolbar and then selecting $D_HI/SOURCE 1 3 U1A C 4 J 1 7476 CLK 2 7408 PRE 2 HI U4A K Q Q A 15 (MSB) 14 U7A B J 1 7476 CLK 1 3 U2A 4 16 2 K CLR HI PRE 2 3 16 CLR C Note: The results of the design by the excitation table method are as follows: JA = BC KA = C' KB = A + C' JB = 1 JC = A' + B KC = A + B' Q Q B 15 B 14 3 7432 HI 2 U6A 3 7408 U5A CLOCK 1 1 7476 CLK 16 3 2 7408 OFFTIME = 50ms DSTM2 ONTIME = 25ns CLK DELAY = 10ns STARTVAL = 1 OPPVAL = 0 J K 3 A OFFTIME = .5ms DSTM1 ONTIME = .5ms CLK DELAY = 0 STARTVAL = 0 OPPVAL = 1 HI U3A 4 CLR 2 PRE 1 Q Q C 15 14 A Title <Title> INIT Size A Date: 5 4 3 Document Number <Doc> Monday, April 03 2 Rev <RevCode> Sheet of 1 1 1 ** circuit file for profile: Transient Date/Time run: 04/03 22:32:27 Temperature: 27.0 (A) Modified Sequence Counter with the counting sequence 0,2,1,3,7,5,6 and repeat CLOCK A B C COUNT 3 0s 7 2ms 5 6 0 4ms 2 6ms 1 3 8ms 7 5 10ms Time Date: April 03 Page 1 Time: 22:34:45 ** circuit file for profile: Transient Date/Time run: 04/03 22:32:27 Temperature: 27.0 (A) Zooming in on the initialization pulse shows the counter being initialized to count 3 INIT CLOCK A B C COUNT X 0s Date: April 03 3 100ns 200ns 300ns Time Page 1 400ns 500ns 600ns Time: 22:38:41 Example: Design a modified sequence counter using the excitation table method that will count in the sequence 0,2,1,3,7,5,6, and repeat. Treat unused count 4 as a "don't care". Use JK flip-flops. Circuit Excitation Table A 0 0 0 0 1 1 1 1 Present State B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 A 0 0 0 1 X 1 0 1 Next State B C 1 0 1 1 0 1 1 1 X X 1 0 0 0 0 1 JA 0 0 0 1 X X X X KA X X X X X 0 1 0 Flip-flop Inputs JB KB 1 X 1 X X 1 X 0 X X 1 X X 1 X 1 JC 0 X 1 X X X 0 X KC X 0 X 0 X 1 X 0 JK Flip-flop Excitation Table Q(t) 0 0 1 1 Q(t+1) 0 1 0 1 J 0 1 X X K X X 1 0 Flip-flop Input Functions and Circuit Output Functions BC A 00 01 11 10 0 0 0 1 0 X 1 X X X BC A 00 01 11 10 0 1 1 X X 1 JA = BC BC A 00 01 11 10 0 X X X X 1 X 0 0 1 KA = C' X 1 X X BC A 00 01 11 10 0 0 X X 1 1 JB = 1 X X X X 0 JC = A'B BC A 00 01 11 10 0 X X 0 1 1 X 1 1 KB = A + C' BC A 00 01 11 10 0 X 0 0 X 1 X 1 0 KC = AB' X