Project 2

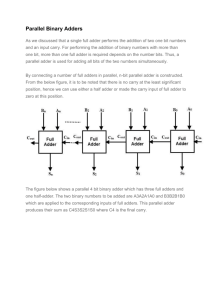

advertisement

Joshua R Smith – 46978 (Section 1) Kimberly J Anderson (Section 2) Project 2 1 April 2004 Purpose and Introduction: The purpose of this project is to simulate an eight-bit adder/subtractor (Figure 1) in ModelSim by writing in the VHSIC Hardware Description Language (VHDL). The adder/subtractor will have three inputs and two outputs. The inputs consist of two 8-bit numbers (A and B), and another 1-bit input (SUB) which will have a value of ‘0’ for the addition A+B, and a value ‘1’ for the subtraction A-B. One output (S) is the resulting 8-bit sum or difference of the inputs. The other output (C_OUT) contains one bit that can be used to spot an error, but that is not considered part of the final sum or difference. Figure 1 This 8-bit adder/subtractor is composed of a network of XOR gates and Full Adders. An XOR gate entity and a Full Adder entity will be composed in VHDL using the dataflow method. That is, these entities are described by using Boolean logic operators in the concurrent statements of the entity’s architecture. Both of these entities will be examined individually via testbenches and wave plots to ensure that they are modeled in VHDL correctly. By comparing a truth table that defines what an entity should do given specific inputs to a wave plot that represents the output for the same given inputs, the accuracy of the VHDL model can be assessed. After the XOR and Full Adder entities are created in dataflow and then tested, a 1-bit adder/subtractor will be constructed using the structural method of description using the tested component entities. A testbench will also be written for this entity and resulting simulation data will be compared to arithmetically predicted results. Finally, eight 1-bit adder/subtractor entities will be connected together through structural description to make the 8-bit adder/subtractor. This final circuit will be analyzed using a testbench to discover whether or not it meets the initial expectations. All of the entity and testbench source codes are attached at the end of this paper. The XOR Gate: The first fundamental entity that needs to be created is the XOR_GATE. The XOR_GATE entity (Figure 2) has two 1-bit inputs (A, B) and a 1-bit output (O). This entity is written in dataflow. Within this entity, the two inputs are joined by the “xor” operator and the result becomes the output. Thus the entity is effectively an XOR gate. The definition of an XOR gate can be seen in the function table below (Table 1). Case: 1 2 3 4 Figure 2 A 0 0 0 0 B 0 0 1 1 O 0 1 1 0 Table 1 The XOR_GATE entity was tested by writing a testbench with the assistance of an online VHDL testbench generator. Since the XOR_GATE has 2 inputs, there are 22 unique combinations of inputs for A and B that need to be tested. These four cases were summarized in Table 1, along with the expected output for each case. The wave plot output for the testbench is shown below in Figure 3. Figure 3 When a signal on the plot goes “high”, that corresponds to a logic value of ‘1’, and if the signal goes “low”, the signal’s value is ‘0’. For each of the cases in the wave plot, the output (w_o) corresponds to the expected output summarized in Table 1. This leads to the belief that the XOR_GATE entity is correctly represented in VHDL and can be used in the 1-bit adder/subtractor later. The Full Adder: The second fundamental entity that needs to be created is the Full Adder. The purpose of this entity is to find the sum and carry when two 1-bit numbers are added. Though a full adder can be constructed in more than one way, the AND-OR-Invert (AOI) form was used in this project (Figure 4). This entity has three 1-bit inputs and two 1-bit outputs: a and b (the numbers to be added), c_in (the carry in, also added), c_out (the carry out), and s (the sum of a+b+c_in). Figure 4 Before proceeding further the terms carry and sum should be clearly defined, which can be best done through an example. Consider the addition of the following decimal numbers: 5+6. When adding this decimal number, we cannot correctly represent the number “11” in the 1s place, so we carry a 1 to the 10s place, leaving a sum of 1 in the ones place. An equivalent process occurs for binary. When adding 1+1 in binary, you cannot represent “2” in the 1s place, so you carry a 1 to the 2s place, leaving a sum of 0. This is the case with the full adder. The sum (s) represents the remainder of the total sum a+b+c_in, after a carry (c_out) has been made, if necessary. The purpose of the full adder then is to find the sum of two 1-bit numbers and a 1-bit carry in. The AOI_FA entity was written using dataflow, joining inputs with Boolean operators such as “and”, “or” and “not.” There is more than one way to construct the AOI_FA using VHDL dataflow descriptions. This project described each gate individually, connecting the output of one gate to the input of another using a wire. Alternately the outputs c_out and s could have been described as a combination of operators in a longer concurrent statement, reducing the number of internal wires needed. This project chose to represent each gate individually to reduce possibility for error when writing a single long concurrent statement. The entity AOI_FA is shown in Figure 5. Figure 5 After constructing the AOI_FA shown in Figure 4 using VHDL, we must test its function. Since there are three inputs to the entity, there are 23 unique combinations of inputs to test. Table 2 summarizes the eight possible cases of inputs, and the expected outputs of the AOI_FA. Case: 1 2 3 4 5 6 7 8 a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 c_in 0 1 0 1 0 1 0 1 c_out 0 0 0 1 0 1 1 1 s 0 1 1 0 1 0 0 1 Table 2 Note: The outputs represented in Table 2 were determined by arithmetic logic (i.e. 1+1 gives you a sum of 0, and a carry of 1), instead of using Boolean logic to find the outputs of the AOI_FA. A testbench was written to simulate the eight possible input cases described in Table 2 of the AOI_FA. The wave plot is shown below in Figure 6. Figure 6 When a signal on the plot goes “high”, that corresponds to a logic value of ‘1’, and if the signal goes “low”, the signal’s value is ‘0’. For each of the cases on the wave plot in Figure 6, the outputs of the logic network (c_out and s) match the arithmetic logic shown in Table 2. This leads to the conclusion that the AOI_FA is functioning correctly and can be used as a component in the structural development of the 1-bit adder/subtractor. 1-Bit Adder/Subtractor: The 1-bit adder/subtractor (onebit_add_subtract) can be described as a structural combination of the XOR_GATE and AOI_FA entities (Figure 7). Structural description uses components that have already been constructed by creating instances of the component and then mapping (tying together) the ports of each individual instance to the external ports of the entity or to internal wires to carry the signal to other instances. Figure 7 As can be seen in Table 1, if one input of an XOR gate, such as A, has a value of ‘0’, then the gate acts like a buffer for the other input, causing the output to be equal to the value of B. If instead A has a value of ‘1’, the gate acts as an inverter, and the output is . When the XOR is tied to the second input of the full adder, the input sub can act as a control that specifies whether the circuit should add or subtract a and b. If sub is ‘0’, the output of the XOR and the input to AOI_FA is simply b, resulting in an adder. Binary subtraction of X-Y requires a way to represent negative numbers using binary. One way is using 2’s complement, which the 1-bit adder/subtractor implements. 2’s complement essentially converts a positive number system binary number to a negative number of equal magnitude so it can be added regularly. Instead of calculating X-Y then, the equivalent is instead calculated: X+(-Y) where -Y is the 2’s complement of Y. To find the 2’s complement, every digit of Y has to be inverted, which results in the 1’s complement, and then 1 is added to this new number. In the 1-bit adder/subtractor, the circuit behaves as a subtractor when sub is ‘1’. This causes the output of the XOR to be , which is the one’s complement of B. When the circuit is a subtractor, c_in has to have a value of one, so that the full adder sums +1 (two’s complement of B) +A. When the testbench for the 1-bit adder/subtractor was created, the SUB wire of the test bench was tied to both sub and c_in of the entity, so that c_in equals ‘0’ when it’s an adder and c_in equals ‘1’ when it’s a subtractor, just as it should. The expected function table for this entity and the simulated wave plot can be seen in Table 3 and Figure 8. Case: 1 2 3 4 5 6 7 8 sub (c_in) 0 0 0 0 1 1 1 1 a 0 0 1 1 0 0 1 1 b 0 1 0 1 0 1 0 1 c_out 0 0 0 1 1 0 1 1 s 0 1 1 0 0 1 1 0 Table 3 Note: The outputs represented in Table 3 were determined by arithmetic logic (i.e. 1+1 gives you a sum of 0, and a carry of 1), instead of using Boolean logic to find the outputs of the 1-bit adder/subtractor. Figure 8 When a signal on the plot goes “high”, that corresponds to a logic value of ‘1’, and if the signal goes “low”, the signal’s value is ‘0’. For each of the eight possible cases, the simulated outputs (s and c_out) match the expectations listed in the function table (Table 3). It can be concluded, then, that the 1-bit adder/subtractor is working as it should. It should be noted however that while each of the outputs was represented as expected, not all of these outputs are meaningful. In two cases, an “error” occurred, reducing the usefulness of the output. In Case 4, 1+1 is calculated, giving a carry of 1 and a sum of 0. Since the carry is not regarded as part of the solution, an overflow has occurred. In Case 6, 0-1 was calculated. However, the output sum cannot express negative numbers, so this output is not meaningful either. A more thorough discussion of the limitations of the adder/subtractor design used in this project is discussed in the next section for the 8-bit version. The 8-bit version does not change any functionality of the 1-bit version, but only makes it able to handle larger numbers. 8-bit Adder/Subtractor: The 8-bit adder/subtractor (eightbit_add_subtract) is made by tying together eight 1-bit adder/subtractor entities (Figure 9). The c_out of the first unit is connected to the c_in of the next unit via a wire, and so on. The 1-bit adder/subtractor was used repeatedly to make the 8-bit adder/subtractor, but only the first of these should have c_in tied to SUB. The very first c_in is tied to SUB within the entity instead of through the testbench because the 8-bit adder/subtractor is the final circuit. c_out of the 8th 1-bit adder/subtractor instantiation is tied to C_OUT of the entire adder/subtractor. The 8-bit A and B buses connect to the a and b inputs of the 1-bit adder/subtractors, and the s outputs make up the 8-bit S bus. SUB is tied to the sub input of each adder/subtractor. Figure 9 This adder/subtractor has some limitations. For example, an 8-bit binary number in the positive number system can represent the decimal numbers between 0 and 28-1, or 255. Thus the inputs A and B will be within this range. The output S is also 8-bits, however, so if the circuit is in addition mode, the inputs A and B must not sum to be greater than 255. If they are, a buffer overflow occurs which is indicated by a C_OUT value of 1. This is because the sum of the 8th bits of A and B add up to a number greater than one, and thus a one must be carried up to the next place value. Because the sum has an 8-bit limitation, the value of the final carry becomes the C_OUT value. This circuit also has a limitation when it is used in the subtraction mode. Because the output S only represents numbers using the positive number system, negative differences cannot be expressed, and therefore input A must be greater than B for A-B to have a positive result. If the B is greater than A, however, C_OUT will have the value of ‘0’ and thus indicating this error. To summarize limitations for an n-bit adder/subtractor of this design: 1. The sum of its inputs A and B cannot exceed the decimal value of 2n-1, and 2. A must be greater than B for subtraction, and 3. As a check, C_OUT should always be equal to SUB. Case: 1 2 3 4 5 6 7 8 9 10 SUB 0 0 0 0 0 1 1 1 1 1 A 00000000 11111111 01100000 00101101 01001111 11111111 00111000 10011010 00000000 10101010 B 11111111 11111111 10100001 10011100 01000000 00111011 01001110 10000010 11111111 01010101 C_OUT 0 1 1 0 0 1 0 1 0 1 S 11111111 11111110 00000001 11001001 10001111 11000100 11101010 00011000 00000001 01010101 Table 4 Note: The outputs represented in Table 4 were determined by arithmetic instead of using Boolean logic to find the outputs of the 8-bit adder/subtractor. Table 4 offers a sampling of cases from the 217 possible input combinations to the 8-bit adder/subtractor. Inputs were chosen to demonstrate cases where the design produces the correct answer, and cases where the design fails (for example, an overflow). We chose a sampling of 5 “addition problems” shown in Cases 1-5, and 5 “subtraction problems” Cases 6-10. For each of these we chose two cases where the design violates one of its limitations and three where it would correctly represent the result. For example, Case 2 has a C_OUT of ‘1’ where SUB is ‘0’, representing an overflow. In Case 9, B is greater than A, which our design cannot account for and the C_OUT value is ‘0’ where SUB is ‘1.’ A testbench was made for this final circuit, and a wave plot (Figure 10) of the cases shown in Table 4 was generated. Figure 10 This wave plot is interpreted slightly differently than previous wave plots. Because A, B and S are buses, the signal does not display as “high” or “low” to represent a single-bit ‘1’ or ‘0’. Instead, 8-bit words are displayed on the wave plot for each case. The cases of the wave plot matched the function table completely. This leads to the belief that the 8-bit adder/subtractor, when used within its known limitations, accurately calculates the sum A and B when SUB is ‘0’ or the difference when SUB is ‘1’. Conclusion: In this project we used ModelSim to create an 8-bit adder/subtractor with VHDL. The lowest level entities, XOR_GATE and AOI_FA, were described using the dataflow method. These entities were combined together using the structural description method to make a 1-bit adder/subtractor, which was repeated and ultimately created the 8-bit adder/subtractor. Each entity was tested individually with a testbench and compared with their expected function tables. The final entity was then tested by choosing cases which would show what the 8-bit adder/subtractor can successfully add/subtract, and for what values it produces results which are not meaningful. These limitations imposed by the design were outlined. By comparing the output timing diagrams in ModelSim against an arithmetically constructed truth table, we verified the accuracy of our VHDL code in correctly representing the 8-bit adder/subtractor network.