labExample

advertisement

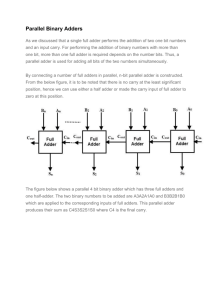

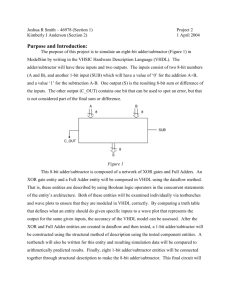

Laboratory #5 Adder/Subtractor Implementation Prepared by: Course: Section: Prepared: Instructor: Sarah Sparkie, Kyle Compy CMPEN 275 007 November 3, 2020 Dr. Coulston Evaluation: Purpose Procedure Results Conclusions PreLab Percentage 10 20 50 10 10 Score In each section the evaluated based on: Correctness – the results and methods are correct. Grammar – the writing uses proper English. Technical writing - the writing conform to accepted technical writing standards. Logic – the exposition is presented in a logical coherent order. Completeness – the exposition covers all the necessary points. Concise – does not introduce unnecessary topics into discussion. Thoroughness – the writing explores and explains the details of the assignment. Purpose: The purpose of this lab is to create an adder subtractor (Add/Sub) component in VHDL capable of both adding and subtracting 4-bit binary and 2’s complement numbers. The adder subtractor will be simulated and then combined with a Hex-To-Seven-Segment Decoder, synthesized and downloaded onto the PLDT-3 board. Procedure: 1) Read and understand the word statement describing the intended behavior of the circuit. 2) Create a truth table to describe a one-bit Full Adder (FA), which has three one-bit inputs (a, b, c) and two one-bit outputs (sum, carry). 3) Determine the SOPmin expression for both the outputs “sum” and “carry.” 4) Draw the schematic for the FA using the SOPmin expressions from Step 3. 5) Using the schematic diagram from Step 4, write the VHDL code for the FA. 6) Simulate the VHDL code for the FA using the test bench file provided. 7) Verify the output of the simulation in the timing diagram using the truth table for the FA created in Step 2. 8) Draw the schematic for an Add/Sub using the FA as a component and XOR gates. 9) Using the schematic diagram from Step 8, write the VHDL code for an Add/Sub. 10) Simulate the VHDL code for the Add/Sub using the test bench file provided. 11) Verify the outputs of the simulation by performing the addition and subtraction executed in the simulation by hand. 12) Draw a schematic for the adder display unit. 13) Write the VHDL code for a device called AddDisp. 14) Write the Implementation Constraints File for the AddDisp to assign each input and output to a pin location of the PLDT-3 board. 15) Synthesize the VHDL code and download to the PLDT-3 board. 16) Verify the circuit operates as intended by the word statement. Results: From the word statement, the intent of the circuit is to perform addition and subtraction of two four-bit binary numbers. The truth table for the FA is given by Table 1 where ‘a’ and ‘b’ are the bits being added, ‘c’ is the carry-in bit, ‘sum’ is the addition of ‘a’, ‘b’, and ‘c’, and ‘carry’ is the carry-out bit. a 0 0 0 0 1 1 1 1 b 0 0 1 1 0 0 1 1 c 0 1 0 1 0 1 0 1 sum carry 0 0 1 0 1 0 0 1 1 0 0 1 0 1 1 1 Table 1: The truth table for the Full Adder. The entries in Table 1 were derived by adding together the inputs and representing the sum as a 2-bit binary number. For example, in the fourth row (a,b,c)=(0,1,1) two of the inputs are equal 1, so the sum of the inputs is two. Thus, the output (carry,sum) is (1,0). Equations 1 and 2 are the SOPmin expression for the outputs ‘sum’ and ‘carry’. These were derived by placing the Table 1 entries into two kmaps and then solving the kmaps. sum(a,b,c) = ab’c’ + a’b’c + abc + a’bc’ (1) carry(a,b,c) = ac + ab + bc (2) Each of the SOPmin equations was then transformed into a schematic as shown in Figure 1. Figure 1: The schematic of the Full Adder. The ‘sum’ and ‘carry’ circuits shown in Figure 1 are transformed into the VHDL shown in Listing 1 by representing each gate with its name. For example the upper AND gate in Figure 1 has input ‘a’, ‘not b’ and ‘not c’. This translates into the VHDL statement “(a and (not b) and (not c)) in Listing 1. sum <= carry <= (a and (not b) and (not c)) ((not a) and (not b) and c) (a and b and c) ((not a) and b and (not c)); (a and c) or (a and b) or (b and or or or c); Listing 1: The VHDL code describing the full adder shown in Figure 1. A simulation of the FA was run using the test bench provided yielding the timing diagram shown in Figure 2. At a time of 25000 ps in the timing diagram, the inputs (a,b,c) are (0,1,0) resulting in sum=1 and carry=0. This is, and all the remaining seven cases, agrees with the desired behavior in Table 1. <missing the timing diagram for full adder simulation> Figure 2: The timing diagram of the full adder with all 8-input combinations being applied. The full adder was developed in order to be incorporated into a larger unit, a 4-bit adder subtractor. This component, shown in Figure 3, takes in as input, two 4-bit 2 numbers (represented in either binary or 2’s complement) and either adds or subtracts them based on the ‘f’ input. Figure 3: The architecture of the 4-bit adder subtractor. The adder subtractor operates using uses four FA’s to perform the addition and four xor gates to either complement or pass the ‘B’ operand through to the adder. The status of the computation is given by the sig_ov and unsig_ov. If the inputs are interpreted as binary numbers the unsig_ov output indicates if overflowed has occurred, the result requires more than four bits to represent. If the inputs are interpreted as 2’s complement numbers then the sig_ov output indicates if overflowed has occurred. The schematic diagram in Figure 3 is translated into the VHDL code shown in Listing 2. fa3: fa2: fa1: fa0: FA FA FA FA xb(3) xb(2) xb(1) xb(0) port port port port <= <= <= <= map(a(3), map(a(2), map(a(1), map(a(0), b(3) b(2) b(1) b(0) xor xor xor xor xb(3), xb(2), xb(1), xb(0), c(2), c(1), c(0), func, sum(3), sum(2), sum(1), sum(0), c(3)); c(2)); c(1)); c(0)); func; func; func; func; sig_ov <= (c(2) xor c(3)); unsig_ov <= c(3); Listing 2: VHDL code describing the architecture of adder subtractor. As seen in Listing 2, each FA is one bit-slice of the Add/Sub; therefore, each FA is assigned one bit of the input and outputs one bit of the sum of the Add/Sub. The carryout of each FA is the carry-in of the next bit of higher significance; in the figure, the leftmost bit is least significant and rightmost bit is most significant. The Add/Sub was simulated using the test bench provided resulting in the timing diagrams shown Figure 4a, where the inputs and outputs of the circuit as binary values. Figure 4b shows the inputs and outputs interpreted as unsigned integers, and figure 4c shows the inputs and outputs interpreted as signed integers. At 65,000 ps in the unsigned integer timing diagram for the Add/Sub, A = 10, B = 7, and func = 1; the outputs at this time are sum = 3, sig_ov = 1, and unsig_ov = 1. This output is logical because func = 1 means that B should be subtracted from A, making the sum equal to 3. When subtracting binary numbers, the 2’s complement of B is added to A, and because 1010 = 10102 and 710 = 01112, 10 – 7 = 3 gives 1010 + 1001 = 10011, which exceeds the word size of the output and causes unsigned overflow. At the same time in the signed integer timing diagram, A = -6, B = 7, and func = 1. (-6) – 7 = -13 but -13 cannot be represented as a four-bit 2’s complement number, causing signed overflow. Signed overflow occurs when the carry-in and carry-out bits of the most significant bit are different. The outputs of the simulation all agree with hand calculations of the operations. <missing figures here> Figure 4a, b,c: Timing diagrams for the 4-bit adder subtractor. Once the operation of the 4-bit adder subtractor was verified it was incorporated into a larger component, the add display component. The purpose of this component was to verify the operation of the 4-bit adder subtractor in the XC9500 CPLD. Consequently, the 4-bit output from the adder subtractor is sent to a 7-segment display so that the user can easily verify the output. <missing figure of the add display component here> Figure 5: The architecture of the add display component. The VHDL code for AddDisp component in Figure 5 is given in Listing 3. The AddDisp component uses one Add/Sub and one Hex2Seven as components. The inputs of the AddDisp correspond with the inputs of the Add/Sub component. The sum output of the Add/Sub is a four-bit signal used as input for the Hex2Seven whose outputs match those of the AddDisp. These outputs drive a seven-segment display to show the user the sum of the two four-bit binary numbers used as input. AS: AddSub port map (a, b, func, sum, sig_ov, unsig_ov); H27: Hex2Seven port map (sum(3), sum(2), sum(1), sum(0), seg(6), seg(5), seg(4), seg(3), seg(2), seg(1), seg(0)); Listing 3: The VHDL code describing the adder display unit in Figure 5. The Implementation Constraint File for the AddDisp was written so that each of the 4-bit inputs is assigned a switch on the PLDT-3 board, func assigned to a button, the outputs are routed to a seven-segment display, and the overflows are indicated by LEDs. The circuit was successfully implemented on the PLDT-3 board. It functions as intended by the word statement. Conclusion: In this lab, it was discovered that a more complicated circuit could be designed by implementing several less complicated circuits together. Specifically, by first creating a Full Adder that was only capable of adding one bit, a more complicated 4-bit Adder/Subtractor could be created using the capabilities of the Full Adder. Then, using the Hexadecimal-to-Seven-Segment Decoder an even more complex circuit could be implemented using all three of the smaller circuit designs, the Full Adder, the Adder/Subtractor, and the Hexadecimal-to-Seven-Segment Decoder. This idea could be very useful in any type of project when the overall task may seem very difficult, but may be accomplished more easily if broken down into smaller, more manageable pieces.