SECX4045 – Digital System Lab

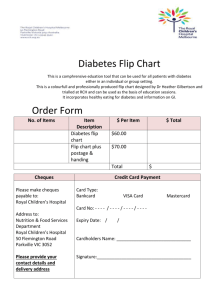

advertisement

CONTENT LIST OF EXPRIMENTS 1. VERIFICATION OF LOGIC GATE 2. DESIGN OF HALF ADDERS AND FULL ADDERS 3. CODE CONVERTER 4. DESIGN OF ENCODER AND DECODER 5. DESIGN OF MULTIPLEXER AND DEMULTIPLEXER 6. DESIGN OF COMPARATOR 7. VERIFICATION OF STATE TRANSISION OF FLIP-FLOP 8. DESIGN OF ASYNCHRONOUS COUNTER EXP: 1 VERIFICATION OF GATES AIM:To study and verify the truth table of logic gates. APPRATUS REQUIRED:Digital Trainer Kit, IC 7404,IC 7408, IC 7432, IC 7400, IC7402, IC 7486. THEORY:A logic gate is an elementary building blocks of a digital circuit. It performs a logical operation on one or more logical inputs and produces a single output. At any given moment, every terminal is in one of the two binary conditions low (0) or high (1).The different types of logic gates are AND Gate: It is a gate which consist of two input (A and B) and one output (Y). Here, the output is true when both the inputs are true. Otherwise the output is false. OR Gate: It consists of two input and one output. The output is true if either or both of the input true. If both inputs are false then the output is false. EX-OR Gate: It also consists of two inputs and one output. The output is true if either, but not both, of the inputs are true. The outputs is false if both inputs are false or if both inputs are true. NOT Gate: A logical inverter which consists of only one input and one output. It reverses the logic state. NAND Gate: The NAND gate operates as an AND gate followed by a NOT gate. Here, the output is false if both the inputs are true. Otherwise, the output are true . NOR Gate: The NOR gate is a combination of OR gate followed by an inverter. Here, the output is true if both inputs are false. Otherwise, the output is false. PROCEDUR:1. Place the IC on IC Trainer kit 2. Connect Vcc and ground to respective pins of IC Trainer kit. 3. Connect the input to the switches provided in the IC Trainer kit. 4. Connect the outputs to the switches of O/P LEDs. 5. Apply various combinations of inputs according to the truth table and observe condition of LEDs. 6. Disconnect output from the LEDs and not down the corresponding multimeter voltage readings for various combinations of inputs. RESULT:- EXP:2 DESIGN OF HALF ADDER AND FULL ADDER AIM:To realize half adder and full adder circuit using EX-OR Gate and basic gates. APPRATUS REQUIRED: Digital Trainer kit, IC 7486, IC 7432, IC 7408, IC 7400,etc. THEROY: Adder is a digital circuit that performs addition of binary numbers. Adder are designed by using different logic gates. There are two type of Adder they are: HALF ADDER: A half adder is a circuit which accept two binary digits on its inputs and produces and two binary digits on its outputs, a sum bit and a carry bit. A half adder circuit can easily be synthesized by using one EX-OR GATE one AND gate. It is used for addition of two bits. FULL ADDER: Full Adder is the adder which accepts two input bits and an input carry and generates a sum output and an output carry. It is used for addition of three bits. Full adder can be designed by using two EX-OR gates, two AND gates two OR gates. Half Adder using basic gates:- Full Adder using basic gates:- PROCEDUR: 1. Verify the gates. 2. Make the connections as per the circuit diagram. 3. Switches on Vcc and apply various combinations of input according to the Truth Table 4. Note down the output reading for Hal /Full adder bit for different combinations of inputs. RESULT:- EXP:3 CODE CONVERTER AIM:To convert given binary numbers to gray codes . APPRATUS REQUIED:Digital Trainer kit, IC 7400, IC 7486 THEORY: Binary to Gray and Gray to Binary conversion. EX-OR Gate can be used for these conversion (programmable Logic Devices).PLDs can also be programmed for these codes conversion. PROCEDUR: 1. The circuit connections are made as circuit diagram. 2. Pin (14) is connected to +Vcc and Pin (7) to ground. 3. In the case of binary to Gray conversion, the inputs,B0, B1, B2, and B3 are given at respective pins and outputs G0, G1, G2, and G3 are taken for all the 16 combinations of the input. 4. In the cause of gray to binary conversion the inputs G0,G1, G2, and G3 are taken for all the 16 combinations of inputs. 5. The value of the outputs are tabulated. Binary to Gray Gray to Binary Truth Table RESULT: EXP:4 ENCODER AND DECODER AIM:To convert a given octal to the binary output APPRATUS REQUIRED:Digital Trainer Kit . THEORY: An encoder is a combinational logic circuit that essentially performs a reverse decoding function. An encoder accepts an active level on one its input representing a digit such as a decimal or octal digit and convert it to a coded output, such as BCD or binary. Encoder can also be devised to encode various symbols and alphabetic characters. The process of converting form familiar symbols or numbers to a coded format is called encoding. PROCEDURE:1. Connections are made as per circuit diagram. 2. The octal inputs are given at the corresponding pins. 3. The outputs are verified at the corresponding output pins. DECODER: The basic function of a detect the presence of a specified combination of bits on its input and to indicate the presence of that code has N input lines to handle N bits and 2n output line to indicate the presence of one more N bits combinations . PROCEDURE:- (decoder) 1. Connections are made as per the circuit diagram . 2. Give different combination of the inputs and observe the decimal numbers displayed on the board . ENCODER: Four to two line encoder DECODER: Two to four line decoder: Truth table PIN DETAILS: TEUTH TABLE: RESULT:- EXP:-5 DESIGN OF MUTIPLEXER AND DEMULTIPLEXER AIM:To design a 2:1 Multiplexer and 1:2 Demultiplexer and to verify Truth Table of multiplexer using IC 74153 and Demultiplexer using IC 74139 APPRATUS REQUIRED:Digital Trainer Kit, IC 74153, IC74139. THEORY: MULTIPLEXER: Multiplexer is a combinational circuit that selects one of several analog or digital inputs signals and forwards the selected input into a signal line. A multiplexer of 2n inputs has N select line which are used to select each output line to send the inputs. Multiplexer are mainly used to increase the amount of data that can be sent over the networks within a certain amount of time and bandwith . A multiplexer is also called as data selector . PROCEDURE: 1. The pin (16) connected to + Vcc. 2. Pin (8) is connected to ground. 3. The inputs are applied either to A input or B input. 2:1 MULTIPLEXER: 1:2 DE MULTIPLEXER: PIN DIAGRAM OF MUX: PIN DIAGRAM OF DEMEX: truth table DEMULTIPLEXER: Demultiplexer (demux) is a combinational circuit which has single input signals and selecting one of many data output line, which is connected to the single input. Procedure:-(IC 74139) 1. The input are applied to either ‘a’ input or input 2. The demux is activated by making Ea low and Eb low 3. The truth table is verified. RESULT:- EXP:6 DESIGN OF COMPARETORS AIM: To verify the Truth Table of one bit and four bit comparators using logic gate. APPRATUS REQUIRED:Digital Trainer Kit, IC 7404, IC 7408, IC 7486, IC7485, THEORY: Comparator: A comparator is a device that compares two input and switches its output to indicate which is larger. A comparator is designed to produce well limited output that easily interface with logic gates. Comparators are made up of standard AND, NOR and NOT gates that digital signals present at their terminals and produce an output depending up on the conditions of those input Procedure:1. 2. 3. 4. 5. 6. Verify the gates. Make the connections as per the circuit diagram. Switch on Vcc. Applying i/p and check for the outputs. The voltmeter readings of output are taken and tabulated in tabular column. The o/p are verified. One bit comparator: Truth table Four bit comparator: RESULT: EXP:7 VERIFICATION OF STATE TRANSITION OF FLIP FLOP AIM: Truth Table verification of Flip Flop: 1. JK flip flop 2. D flip flop 3. T flip flop 4. SR flip flop APPRATUS REQUIRED: IC 74OO, IC 7404, IC 7410, IC7411,etc. PRCEDURE:1. Connections are made as per circuit diagram. 2. The truth table is verified combinations of inputs. THEORY: Flip Flop: A Flip Flop is a circuit that has two stable states and can be used to store states information. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two output. It is basic storage element in sequential logic . Flip Flop are the fundamental building block of digital electronic systems used in computer, communications and many other types of systems Flip Flop can latches and the clocked one is called Flip Flop. Different type of Flip Flop are: JK Flip Flop: JK Flip Flop consists of two SR Flip Flops connected in series with each other , so that the outputs of the first Flip Flop act as inputs to the second. The output of second Flip Flop say Q and Q’, are feed back to the first flip flop along with the original inputs S and R by using two AND gates. JK FLIP-FLOP Truth table Truth table D FLIP-FLOP OUTPUT Q 0 0 1 1 INPUT D 0 1 0 1 0 1 0 1 T FLIP –FLOP Truth table OUTPUT Q 0 0 1 1 INPUT T 0 1 0 1 0 1 1 0 Truth table SR FLIP-FLOP Q OUTPUT INPUT S R Q 0 0 0 1 1 1 0 1 0 1 1 0 NA D- Flip Flop: D- Flip Flop is also know as a data or delay Flip Flop. The D- Flip Flop captures the values of the D input at a definite portion of clock cycle. The capture value become the Q output . At other times, the output doesn’t change. The D flip flop consists of logic gates. T-Flip Flop: On other flip flop, when the both inputs are high, invalid condition takes place. So Toggle flip flop is used. In this flip flop, if the T input is high, the T flip flop changes state whenever the clock input is scrubbed . If the T input is low, the flip flop holds the previous value. RESULT: EXP:8 DESIGN OF ASYNCHRONOUS COUNTERS AIM:To design a three bit asynchronous counter using JK Flip Flop. APPRATUS REQUIRED:Digital Trainer Kit, Three IC 7476. THEORY: Flip Flop can be connected together to perform counting operations. Such group Flip Flop is counter. Counter are classified into two broad categories. They are: 1. Asynchronous counter 2. Synchronous counter Asynchronous counter In asynchronous counter, commonly called ripple pulse and the clock pulse is given to the first flip flop and each successive flip flop is clocked by the output of the preceding flip flop. Synchronous counter In synchronous counter, the clock input is connected to all the flip flops so that they are clocked simultaneously. PROCEDURE: 1. Connection are made as per circuit diagram. 2. Clock pluses are applied one by one at the clock i/p and o/p is observed at QA, QB & QC for IC 7486. 3. Trust table is verified. 3 Bit Asynchronous up counter: 3 Bit Asynchronous Down counter clock Q2 Q1 Q0 0 1 1 1 1 1 1 0 2 1 0 1 3 1 0 0 4 0 1 1 5 0 1 0 6 0 0 1 7 0 0 0 8 1 1 1 9 1 1 0 RESULT: