Heirarchical_layout_..

advertisement

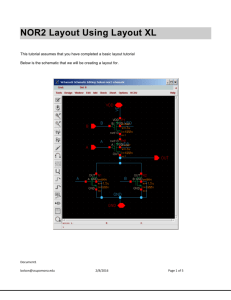

Heirarchical Layout using Layout XL This tutorial assumes that you have completed a basic layout tutorial Below is the schematic that we will be creating a layout for. Document1 bolson@csupomona.edu 2/6/2016 Page 1 of 4 1) 2) 3) 4) 5) 6) 7) 8) 9) 10) 11) 12) 13) 14) In the top toolbar select: Tools->Design Synthesis->Layout XL In the new window select create new Select OK to close the window Select OK to close the new window You will see a Virtuoso layout window In the top toolbar of the new Virtuoso layout window select Design-> Gen from Source Select all the pins and change their widths to be .9um and the layer to be metal 1 Select update to change the properties of the pin Under Pin label options select roman as the font (it is easier to read) Select OK at the top to close the window In top toolbar of the layout Virtuoso window select Options->Display Change the Display levels to stop at 10 Select OK to close the window In the Virtuoso Layout window you will see NOR2 gates that you created and the pins. Put them in the PrBound box 15) To save area make sure to merge the n-wells 16) Place the ins appropriately on the layout 17) the transistors and pins. They all must go in the PrBound Box (the purple box) pins 18) Move the transistors (bindkey m) into the Pr Bound box as shown below. You will have to merge sources and drains by overlapping transistors. As you do this notice that lines appear indicating the connectivity of the gate, source and drain of the transistors to the corresponding pins Document1 bolson@csupomona.edu 2/6/2016 Page 2 of 4 19) Move the pins to correspond with the layout (as shown below). When you move the pins you are moving text and a box (The box not visible until selected). Make sure that you select both. o You may remember that the pins were originally assigned layers ex) A was assigned to ploy and Y to metal 1. When the pins are placed on the layout they should be placed on those layers. If not, change the pin layer by selecting the box that the pin is affiliated with and selecting bindkey q to change the properties so that the layers agree 20) If you look at the virtuoso schematic window you will notice that when a transistor or pin is selected on the layout then it is highlighted on the schematic. Document1 bolson@csupomona.edu 2/6/2016 Page 3 of 4 21) Complete the layout of the nor2 as shown Document1 bolson@csupomona.edu 2/6/2016 Page 4 of 4