22446_S11_Serial_Interface

advertisement

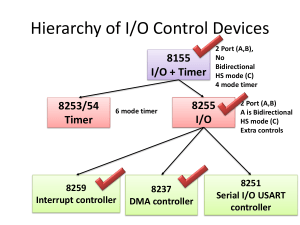

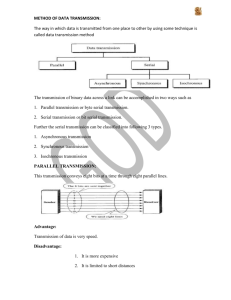

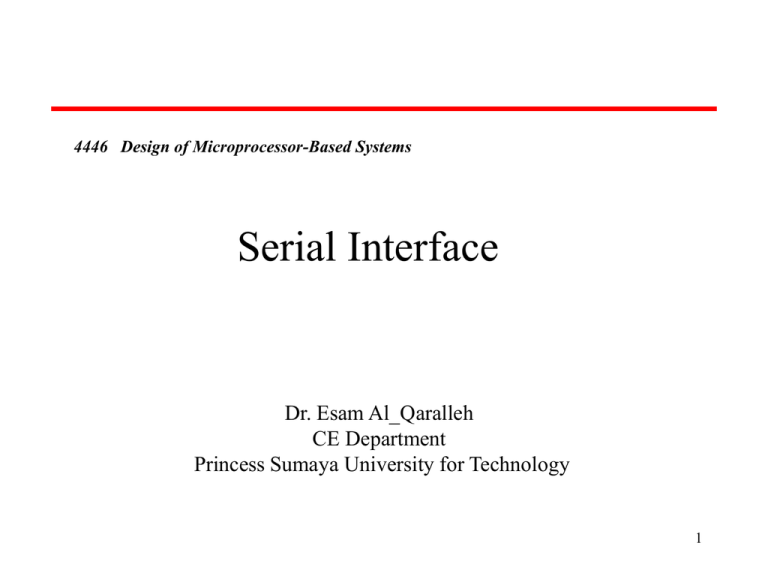

4446 Design of Microprocessor-Based Systems Serial Interface Dr. Esam Al_Qaralleh CE Department Princess Sumaya University for Technology 1 External Interface • Two ways of interfacing I/O devices – Serial • Cheaper • Slower – Parallel • Faster • Data skew • Limited to small distances 11-2 External Interface (cont’d) Two basic modes of data transmission 11-3 External Interface (cont’d) • Serial transmission – Asynchronous • Each byte is encoded for transmission – Start and stop bits • No need for sender and receiver synchronization – Synchronous • Sender and receiver must synchronize – Done in hardware using phase locked loops (PLLs) • Block of data can be sent • More efficient – Less overhead than asynchronous transmission • Expensive 11-4 External Interface (cont’d) 11-5 External Interface (cont’d) Asynchronous transmission 11-6 External Interface (cont’d) • EIA-232 serial interface – Low-speed serial transmission – Adopted by Electronics Industry Association (EIA) • Popularly known by its predecessor RS-232 – It uses a 9-pin connector DB-9 • Uses 8 signals – Typically used to connect a modem to a computer 11-7 External Interface (cont’d) • Transmission protocol uses three phases – Connection setup • Computer A asserts DTE (Data Terminal Equipment) Ready – Transmits phone# via Transmit Data line (pin 2) • Modem B alerts its computer via Ring Indicator (pin 9) – Computer B asserts DTE Ready (pin 4) – Modem B generates carrier and turns its DCE (Data Communication Equipment) Ready • Modem A detects the carrier signal from modem B – Modem A alters its computer via Carrier Detect (pin 1) – Turns its DCE Ready – Data transmission • Done by handshaking using – request-to-send (RTS) and clear-to-send (CTS) signals – Connection termination • Done by deactivating RTS 11-8 Serial Data Transfer Asynchronous v.s. Synchronous — Asynchronous transfer does not require clock signal. However, it transfers extra bits (start bits and stop bits) during data communication — Synchronous transfer does not transfer extra bits. However, it requires clock signal Frame Asynchronous Data transfer Synchronous Data transfer data Start bit B0 B1 B2 B3 B4 B5 B6 Stop bits Parity clk data B0 B1 B2 B3 B4 B5 Baud (Baud is # of bits transmitted/sec, including start, stop, data and parity). 11-9 8251 USART Interface 8251 D[7:0] RS232 TxD RD RD WR A0 WR C/D CLK CLK RxD TxC RxC A7 A6 A5 A4 A3 A2 A1 IO/M 11-10 11-11 Programming 8251 8251 mode register 7 6 Number of Stop bits 00: 01: 10: 11: invalid 1 bit 1.5 bits 2 bits 5 4 3 2 0 Mode register Baud Rate Parity enable 0: disable 1: enable Character length Parity 0: odd 1: even 1 00: 01: 10: 11: Syn. Mode x1 clock x16 clock x64 clock 00: 5 bits 01: 6 bits 10: 7 bits 11: 8 bits 11-12 Programming 8251 8251 command register EH IR RTS ER SBRK RxE DTR TxE command register TxE: transmit enable DTR: data terminal ready, DTR pin will be low RxE: receiver enable SBPRK: send break character, TxD pin will be low ER: error reset RTS: request to send, CTS pin will be low IR: internal reset EH: enter hunt mode 11-13 Programming 8251 8251 status register DSR SYNDET FE TxRDY: RxRDY: TxEMPTY: PE: OE: FE: SYNDET: DSR: OE PE TxEMPTY RxRDY TxRDY status register transmit ready receiver ready transmitter empty parity error overrun error framing error sync. character detected data set ready 11-14 Simple Serial I/O Procedures Read Write start start Check RxRDY Check TxRDY No No Is it logic 1? Is it logic 1? Yes Yes Read data register* end * This clears RxRDY Write data register* end * This clears TxRDY 11-15 Errors – Parity error: Received data has wrong error -transmission bit flip due to noise. – Framing error: Start and stop bits not in their proper places. • This usually results if the receiver is receiving data at the incorrect baud rate. – Overrun error: Data has overrun the internal receiver FIFO buffer. • Software is failing to read the data from the FIFO. 11-16