PathFinding Methodology for Interposer and 3D Die Stacking

advertisement

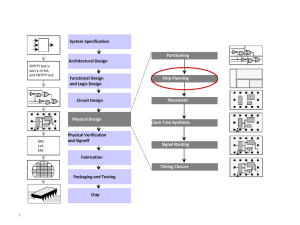

PathFinding Methodology for Interposer and 3D Die Stacking Sherry Xiaoxia Wu*, Ravi Varadarajan†, Navneet Mohindru†, Durodami Lisk*, Riko Radojcic* *Qualcomm Inc. †Atrenta Inc. Outline Motivation of PathFinding Methodology PathFinding Methodology Flow Demonstrations using an Example Conclusion 2 Typical 3D Design Options 2.5D Side by side die stacked on a passive interposer that includes TSVs Multiple DRAM die 3D Memory stacked standalone or on an active interposer 3D Memory on Logic 3D Logic on Logic 3D + Interposer One or More DRAM die stacked directly on logic die (M-o-L) Multiple logic die stacked on top of each other (L-o-L) Mix of side by side and stacked schemes with a passive/active interposer Courtesy: Si2 3 Motivation of PathFinding Methodology Concept Architecture Concept Technology Navigating many choices …. Cost, power, performance… Co-optimize process & design Partitioning Partitioning Partitioning Choices Choices Choices Orientation Orientation Orientation Choices Choices Choices u-Arch u-Arch u-Arch Choices Choices Choices TSV TSV TSV Choices Choices Choices PD PD Tech Choices Choices Choices Fill Fill Fill Choices Choices Choices Package Package Package Choices Choices Choices Assembly Assembly Assembly Choices Choices Choices Need a structured design exploration methodology ??? Past experience not applicable to disruptive technologies Not tie to legacy design Quick and flexible High fidelity/low accuracy Form Factor, Yield, Power, Performance Need methodology to make the selections PathFinding 4 PathFinding Methodology Design Architecture RTL, Blackbox, Netlist, Top level SDC/DEF/IO Constr, Interfaces, Tier/die config. Many more challenges in 3D: - IP/tier assignment - Intra/inter die floorplan - Power & thermal - Timing across dies Early Design Planning Physical Units Handoff 1 Tier/ Die 1 … - TSV/bump alignment Physical Units Handoff N Logical, Physical, Timing Logical, Physical, Timing Backend Implementation 1 - TSV & stack configuration … Tier/ Die N Backend Implementation N 5 PathFinding Methodology 3D stack XML file Create logical partitions for each die Modify partitions Are interconnectivity and TSV reports for all dies acceptable? N Y Commit logical partitions in to 3D physical partitions Physical prototyping on each die partition Modify TSV cluster/locations Are all dies physically feasible? N Y Backside RDL/ Interposer routing Modify number of RDL layers/bump locations Is Backside RDL routing/Interposer feasible? N Y 1. Handoff 3D stack XML file with partitions 2. Handoff DEF file for every partition 6 3D Format - XML XML: Ongoing Standardization Two Dies on a Passive Interposer Interposer and 3D die stacking Two Stacked Dies 7 Logic Partition Bottom die Bottom die Dummy Top die Block in Bottom die frontside backside bottom die front-side TSV backside net net ubump net ubump Top die frontside net Block in top die 8 Floorplan Constraints and An Example TSV/ubmp size, XML Create/mark TSV/ubump clusters Assign TSVs/ubump to clusters Set cluster utilization/aspect ratio FP constraints: guide/region Floorplan constraints Blackbox locations Die utilization: block area/die area Number of TSV clusters: 2, 4, 8 TSV size/pitch/location ubump size/pitch/location 9 Floorplan Options for a LoL Case 2 TSV clusters 4 TSV clusters TSV cluster guide 8 TSV clusters TSV aspect ratio Number of TSV clusters TSV cluster guide T S V TSV cluster aspect ratio TSV pitch 10 Frontside Routing Analysis Vary bottom and top routing layer Vary macro routing layer Vary routing porosity in a window for PDN/DFT consideration 11 Backside Routing Analysis Explore BRDL options when TSV and ubumps are not aligned Vary number of BRDL layers and pitch Foundry OSAT Above 2 BRDL layers, more complicated ubump and expensive process group 2 12 2.5D Interposer Interposer Floorplan, Interposer Routing and Congestion 2 interposer routing layers, pitch = 5um 2 interposer routing layers, pitch = 2um 2 interposer routing layers, pitch = 1um 13 Conclusion A physical PathFinding methodology for interposer and 3D die stacking is presented The results show that with this methodology, users are able to explore different process and design options for early estimation of their designs to reduce expensive backend iterations This methodology is a general flow, it also works for mixed interposer and 3D die stacking 14