Mid Semester Presentation

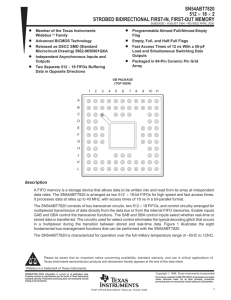

advertisement

GENERAL PURPOSE FIFO ON VIRTEX-6 FPGA ML605 BOARD MIDTERM PRESENTATION STUDENTS: OLEG KORENEV EUGENE REZNIK SUPERVISOR: ROLF HILGENDORF 1 Semester: spring 2012 CONTENT 1. Project overview 2. Goals 3. Specifications 4. HW Block Diagram 5. MEMORY on ml605 6. AXI4 7. Design Block Diagram 8. Accomplished so far 9. Workflow 2 10. Timeline PROJECT OVERVIEW Design and implementation of General Purpose FIFO IP core which allows usage of external memory (DDR3) as FIFO storage on Xilinx FPGA device • Design and implement generic IP core of FIFO • Design and implement GUI generator of IP core on PC 3 • Create sample design with implemented IP core OUR GOALS •Gain experience in hardware development (VHDL environment) •Explore and expertise FPGA work environment •Create design with configurable • word size • FIFO depth •Achieve best performance •Minimize usage of FPGA resources 4 •Make our world a better place SPECIFICATIONS Hardware • Xilinx Virtex-6 ML605 FPGA Evaluation Kit • DDR III memory • Ethernet interface • PCIe interface • PC with Ethernet interface Software 5 • ISE Design Suite Logic Edition Version 13.2 • Modelsim HW BLOCK DIAGRAM ML605 BOARD VIRTEX6 USER DESIGN FIFO CORE DDR3 MEMORY ETHERNET/PCIe 6 PC MEMORY ON ML605 DDR3 memory • Capacity: 512MB • Max theoretical bandwidth: 800MT/s*64bit = 6.4GB/sec Xilinx provides us with DDR3 controller which has AXI Memory Mapped interface • AXI bus data width up to 1024 bit 7 • 256 bit for max memory performance, assuming bus works with 200Mhz AXI4 Xilinx provides us with AXI4 Memory Mapped bus, which is a standard bus used in modern ARM SoC. Features 8 • Separate Address/Control and Data Phases • burst-based transactions with only start address issued • separate read and write data channels DESIGN BLOCK DIAGRAM HOST STORAGE DDR3 LOGIC STORAGE USER STORAGE MEMORY CONTROLLER AXI4 BUS (INTERCONNECT) ARBITER / CONTROLLER FIFO TO MEMORY MEMORY TO FIFO FIFO TO MEMORY MEMORY TO FIFO F I F O F I F O F I F O F I F O LOGIC Ethernet Interface User Interface HOST 9 ETHERNET DESIGN BLOCK DIAGRAM HOST STORAGE DDR3 LOGIC STORAGE USER STORAGE MEMORY CONTROLLER AXI4 BUS ARBITER / CONTROLLER FIFO TO MEMORY MEMORY TO FIFO FIFO TO MEMORY MEMORY TO FIFO F I F O F I F O F I F O F I F O LOGIC EMULATOR User Interface 10 User Interface ACCOMPLISHED SO FAR External interface • • • • Defined basic FIFO interface Defined word size limitation as 32 up to 1024 bit Studied features and integrated AXI4 memory mapped bus Connected DDR3 to AXI bus Internal architecture 11 • Implemented memory arbiter with basic functionality, connected to AXI bus as master • Implemented internal FIFO-To-Memory controller • Implemented internal Memory-To-FIFO controller • Implemented basic emulator of user logic for testing PROBLEMS Placement in FPGA • We did not succeeded to place synthesized memory controller on chip. Design 12 • In which policy should memory arbiter work • Ethernet or PCIe? WORKFLOW Add AXI Interconnect for enabling User Logic to use memory Improve AXI arbiter for best performance Studying usage of Ethernet for communication with PC • Integrating Ethernet controller with AXI stream interface into design Verification of design in hardware Implementing GUI for generating FIFO IP core Testing 13 Implementing sample design TIMELINE Duration Integrate AXI interconnect into design 1 week Complete AXI arbiter functionality 2 weeks Studying and integrating Ethernet controller into design 2 weeks Verification design in hardware including communication with PC 3 weeks Part A Presentation 1 week 17/6 24/6 exams 29/7 5/8 12/8 19/8 26/8 2/9 14 Task