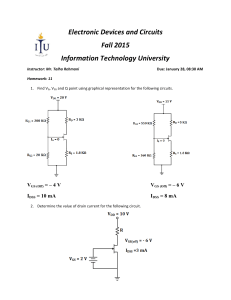

KENYATTA UNIVERSITY SCHOOL OF ENGINEERING AND TECHNOLOGY DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING BIOMEDICAL ENGINEERING ANALOGUE ELECTRONICS LA B REPORT NAME: EHAB AREF REG NO: J23F/19003/2020 JULY, 2023 FIELD EFFECT TRANSISTORS a) BASIC DIODE TEST The JFET Diode Test PROCEDURE The positive and negative probes of the voltmeter were placed at different terminals as follows: RESULTS V V V V V V + D S G S G D S D S G D G V(mv) 382 391 1021 1989 1029 1986 DISCUSSION The high resistance across VGS shows that it is an N Channel. The similarities in VDS and VSD are because it is the same material. The MOSFET Diode Test V V V V V V + D S G S G D S D S G D G V(mv) 1023 1024 778 I 776 I DISCUSSION 778 mV across VGS= shows that it us an N type MOSFET I shows that the resistance is infinite. The JFET Resistance Test R R R R R R + - D S G S G D S D S G D G K Ohms 0.395 0.398 22 21.5 21.9 21.4 DISCUSSION The small resistance across RDS shows that there is a conduction path due to the N channel. The MOSFET Resistance Test R R R R R R + - D S G S G D S D S G D G M Ohms 0.250 0.250 18.42 I 18.42 I JFET OBJECTIVES To understand the structure and operating principle of JFET To measure the characteristics of JFET THEORY The DC Junction field effect transistor is a 3-pin unipolar solid state semiconductor device which controls the secondary output circuit by the application of an electric field in the primary circuit which is also the input circuit. APPARATUS 1. KL-22001 Basic Electrical/Electronic Circuit Lab 2. KL-25005 FET Circuit Experiment Module 3. Multimeter MEASURING IDSS 1. The KL-25005 Module on the KL-22001 Basic Electrical/Electronic Circuit was set and block b located. 2. The connections were made by referring to the diagrams shown below. 3. The ammeter was connected to measure lDSS. 4. V+ was adjusted from 3 to 18V, then lDSS measured and recorded. RESULTS VDD(v) 3 IDSS(µA) 0.2 VGS(V) 4 0.3 5 0.4 7 0.6 9 0.8 0 12 1.1 15 1.4 18 1.6 MEASURING VP PROCEDURE 1. The connections were connected by referring to the circuit below and the wiring diagram. 2. The ammeter was connected to measure ID. 3. VR4 was adjusted (1MQ) so that lD = 0. 4. The voltmeter was used to measure Vgs= VP RESULTS While ID=0, VGS = -3.56 DISCUSSION Drain Characteristics Output Characteristics OUTPUT CHARACTERISTICS 6 5 ID 4 3 2 1 0 0 5 10 15 20 VDS The procedures conducted prove that at VGS=0, ID increases until it reaches a constant current value called IDSS. It also shows that for an n-channel JFET, VP is usually a negative value. CONCLUSION Vp = VGSO. VGSO is the negative applied at input circuit and shuts the channel completey to result to a current = 0; ID = 0. Vp is the positive potential at output circuit that sets a constant channel width and the ID does not grow linearly. VGS is the shut off voltage. DEPLETION N TYPE MOSFET APPARATUS 1. KL-22001 Basic Electrical/Electronic Circuit Lab. 2. KL-25005 FET Circuit Experiment Module. 3. Multimeter. PROCEDURE a) Measuring IDSS 1. The KL-25005 Module on the KL-22001 Basic Electrical/Electronic Circuit Lab, was set and block b located. 2. The connections were made by referring to the circuit shown below: V+ from Adjust Power on Kl-22001 Lab was connected to V+ on KL-25005 and the voltage control knob turned to min. 3. The ammeter was connected to measure IDSS 4. V+ was adjusted from 3 to 18V and the IDSS value recorded in the following table. RESULTS VDD(v) 0.25 IDSS(mA) 2.38 VGS(V) 3 4.79 4 4.84 When VDD= 0.25V, IDSS = 2.38 mA When VGS=0V, IDSS = 2.37 mA When ID= 0, VGS = -1.44 = VT DISCUSSION Output Characteristics 5 4.87 7 4.91 9 4.95 0 12 4.98 15 5.00 18 5.00 OUTPUT CHARACTERISTICS OF DEPLETION N TYPE MOSFET 6 5 VDD 4 3 2 1 0 0 5 10 15 20 IDSS Drain Characteristics CONCLUSIONS If VGS = 0, ID will increase with VDS until it maintains at a constant value called IDS. The pinch off voltage of a JFET Vp is the VGS value when ID=0 b) Measuring Vp PROCEDURE 1. The connection was completed by following the diagram shown. -12v, +12v and V+ were applied. 2. V+ was set to 12V. 3. The ammeter was used to measure ID. 4. VR4, a variable resistor, was varied to obtain ID=0. 5. While ID=0, VGS= VP=-11.10V was measured. 6. VR4 was adjusted to VGS=0. At this value, ID=2.3mA. DISCUSSION For an n-channel MOSFET, ID rises to a constant maximum value (IDss) when VGS=0. ID will decrease when negative VGS is increased. When ID=0, the VGS value at that point is called the pinch-off voltage denoted by VP. DATA FROM GROUP 2 The following values were collected from the other group: JFET BASIC DIODE TEST V V V V V V + D S G S G D S D S G D G V(mv) 195 204 725 OL 729 OL MOSFET BASIC DIODE TEST V V V V V V + D S G S G D S D S G D G V(mv) 460 OL OL OL OL OL JFET RESISTANCE TEST R R R R R R + - D S G S G D S D S G D G K Ohms 0.379 0.386 7.99 8.05 7.83 7.87 MOSFET RESISTANCE TEST R R R R + - D S G S S D S G K Ohms OL 225 OL OL R R G D D G OL OL JFET CHARACTERISTIC CURVES DATA VGS(v) 0 -0.5 -1 -1.5 -2 -2.5 -3 -3.5 VR3(mA) 12.93 12.42 11.98 11.60 11.22 10.79 OL OL ID(Ma) 12.93 12.42 11.98 11.60 11.22 10.79 VGS(v) VR3(mA) ID(Ma) -4 OL -4.5 OL 0 -0.5 -1 -1.5 -2 -2.5 -3 -3.5 -4 -4.5 13.14 13.35 13.43 13.54 13.62 13.76 14.00 14.36 14.4 OL 13.14 13.35 13.43 13.54 13.62 13.76 14.00 14.36 14.4 -5 OL -5.5 OL -5 -5.5 OL OL -6 OL -6 OL 16 14 12 10 Id(mA) 8 Characteristic curve 6 4 2 0 -4 -2 -2 0 2 4 6 VGS(V) VDS(v) 0 1 2 3 4 5 6 7 8 9 10 11 12 VR3(mA) 0.41 0.476 0.544 0.608 0.668 0.738 0.803 0.865 0.926 0.996 1.063 1.136 1.227 ID(Ma) 0.41 0.476 0.544 0.608 0.668 0.738 0.803 0.865 0.926 0.996 1.063 1.136 1.227 VDS(v) 0 1 2 3 VR3(mA) 0.654 1.148 1.535 1.8666 ID(Ma) 0.41 0.476 0.544 0.608 4 2.19 0.66 8 5 2.50 0.73 8 6 2.88 0.80 3 7 OL 0.86 5 8 9 10 11 12 OL OL OL OL OL 0.926 0.996 1.063 1.136 1.227 3 2,5 Id(mA) 2 1,5 VGS=-1.5 1 VGS=-0.5 0,5 0 0 5 10 15 VDS (V) Discussion When drain to source voltage is applied across the drain and the source, electrons flow from the source to the drain through the narrow channel existing between the depletion regions. This constitutes the drain current. The value of the drain current is maximum when no voltage is applied between the gate and the source. This maximum current is designated as 𝐼𝐷𝑆𝑆. When 𝑉𝐺𝑆, is applied, and increased above zero, the reverse bias voltage across the gate source junction is increased which widens the depletion regions. This reduces the effective width of the channel and therefore controls the flow of the drain current through the channel. If the gate to source voltage is increased further, a stage is reached at which the two depletion regions touch each other. At this gate to source voltage, the channel is completely blocked and drain current is reduced to zero. The gate to source voltage at which the drain current is zero is called pinch off voltage. MOSFET CHARACTERISTIC CURVES DATA VGS(v) 0 VR4(mA) 0 0ID(Ma) 1 0 2 0 2.2 0 2.4 0 2.6 0 2.8 0 3 0 3.5 0 5 0 5.5 0 6 0 VGS(v) 0 VR4(mA) 0 1 0 2 0 2.2 3.7 2.4 18.5 2.6 90 2.8 0.41 9 3 1.67 3 3.5 5 5.5 6 15.58 15.69 15.69 15.72 ID(Ma) The curves after plotting the data 18 16 14 Название оси 12 10 8 Transfer x-tic 6 4 2 0 -10 -5 0 -2 Название оси 5 10 Discussion When positive voltage is applied at the gate, negative charge is induced in the P-type substrate adjacent to the silicon dioxide layer. The negative charges are obtained by attracting electrons from the source. If the gate is made positive enough, it attracts many electrons and forms a thin layer of electrons stretching from source to drain. This layer is called N-type inversion layer. Minimum gate to source voltage at which inversion layer is produced is known as threshold voltage ((𝑡ℎ)). When gate to source voltage is greater than this threshold value significant value of current flows. RECOMMENDATIONS 1. The lab was so interesting. I would recommend that more time is allocated to the lab sessions so that we can learn more. 2. More topics could be explored practically for better understanding.