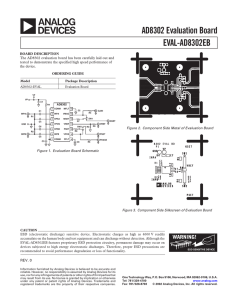

AD8304 Evaluation Board

EVAL-AD8304EB

BOARD DESCRIPTION

ORDERING GUIDE

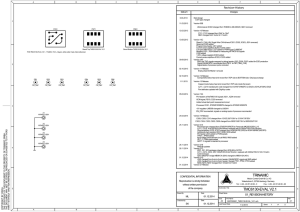

The AD8304 evaluation board has been carefully laid out and

tested to demonstrate the specified high speed performance of the

device. The schematic for the AD8304 evaluation board is shown

in Figure 1, and the two board sides are shown in Figures 2 and 3.

It can be configured for a wide variety of experiments. The board

is factory set for Photoconductive Mode with a buffer gain of

unity, providing a slope of 10 mV/dB and an intercept of 100 pA.

By substituting resistor and capacitor values, all of the application

circuits presented in this data sheet can be evaluated. Table I

describes the various configuration options.

+VS

R10

10k⍀

SW1

LK2 OPEN

INPUT

LK1

INSTALLED

R15

750⍀

C11

1nF

BIASER

GND

Model

Package Description

AD8304-EVAL

Evaluation Board

–VS

AD8304

C1

0.1nF

R7

OPEN

C2

1nF

R5

OPEN

R7

OPEN

R9

0.1F

R6

OPEN

1 VNEG

ACOM 14

2 PWDN

BFNG 13

3 VSUM

VPS1 12

4 INPT

VOUT 11

5 VSUM

VPS2 10

6 VPDB

C10

0.1F

C9

10nF

7 VREF

BFIN 9

VLOG 8

R1

OPEN

R2

0⍀

C3

1nF

C4

0.1F

C7

OPEN

R11

0⍀

R13

0⍀

R12

OPEN

C8

OPEN

LOG

OUT

R14

0⍀

C6

OPEN

BUFFER

OUT

C5

OPEN

R4

OPEN

R3

OPEN

Figure 1. Evaluation Board Schematic

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

EVAL-AD8304EB features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© 2002 Analog Devices, Inc. All rights reserved.

C03288–0–11/02(0)

EVAL-AD8304EB

Figure 2. Component Side Layout

Figure 3. Component Side Silkscreen

Component

Function

Default Condition

VP, VN, AGND

Positive and Negative Supply and Ground Pins

Not Applicable

SW1, R10

Device Enable. When SW1 is in the “0” position, the PWDN pin is

connected to ground and the AD8304 is in its normal operating mode.

SW1 = Installed

R10 = 10 kW (Size 0603)

R1, R2

Buffer Amplifier Gain/Slope Adjustment. The logarithmic slope

of the AD8304 can be altered using the buffer’s gain-setting resistors,

R1 and R2.

R1 = Open (Size 0603)

R2 = 0 W (Size 0603)

R3, R4

Intercept Adjustment. A dc offset can be applied to the input terminals of the buffer amplifier to adjust the effective logarithmic intercept.

R3 = Open (Size 0603)

R4 = Open (Size 0603)

R5, R6, R7, R8, R9

Bias Adjustment. The voltage on the VSUM and INPT pins can be

altered using appropriate resistor values. R9 is populated with a decoupling capacitor to reduce noise pickup. The decoupling capacitor can be

removed when a fixed bias is applied to VSUM.

R5 = R6 = Open (Size 0603)

R7 = R8 = Open (Size 0603)

R9 = 0.1 mF (Size 0603)

C1, C2, C3, C4, C9

Supply Decoupling Capacitors

C1 = C4 = 0.1 mF (Size 0603)

C2 = C3 = 1 nF (Size 0603)

C9 = 10 nF (Size 0603)

C10

Photodiode Biaser Decoupling. Provides high frequency decoupling

of the adaptive bias output at Pin VPDB.

C10 = 0.1 mF (Size 0603)

C5, C6, C7, C8, R11, Output Filtering. Allows implementation of a variety of filter configR12, R13, R14

urations, from simple RC low-pass filters to three-pole Sallen and Key.

R11 = R13 = 0 W (Size 0603)

R12 = Open (Size 0603)

R14 = 0 W (Size 0603)

C5 = C6 = Open (Size 0603)

C7 = C8 = Open (Size 0603)

R15, C11

Input Filtering. Provides essential HF compensation at the input

Pin INPT.

R15 = 750 W (Size 0603)

C11 = 1 nF (Size 0603)

LK1, LK2

Guard/Shield Options. The shells of the SMA connectors used

for the input and the photodiode bias can be set to the voltage on the

VSUM pin or connected to ground.

LK1 = Installed

LK2 = Open

–2–

REV. 0

PRINTED IN U.S.A.

Table I. Evaluation Board Configuration Options