MOS Transistor Theory

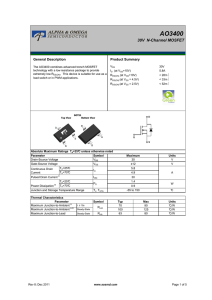

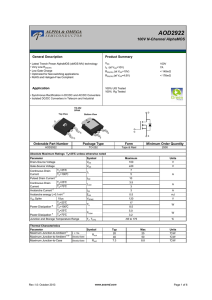

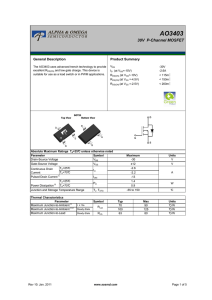

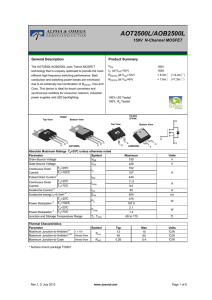

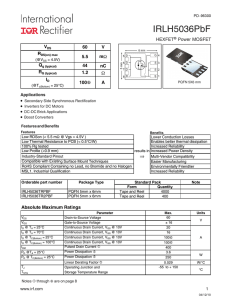

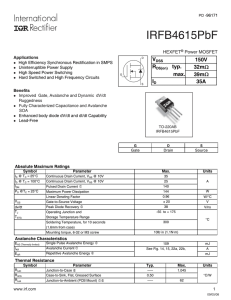

advertisement

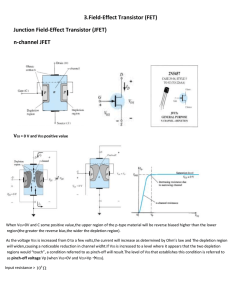

MOS Transistor Theory • nMOS Transistor Two types of transistors • nMOS pMOS • If the gate is “high”, the switch is on If the gate is “low”, the switch is off Drain • Digital integrated circuits use these transistors essentially as a voltage controlled switch Gate g=0 Source g=1 3 March 2009 1 nMOS Transistor 3 March 2009 2 nMOS Transistor MOS: Metal Oxide Semiconductor Cross Section Polysilicon Gate Source n+ Gate oxide Drain n+ L Silicon Dioxide SiO2 Field-Oxide (SiO2) p substrate Bulk (Body) Gate Drain Source Cross-section of an n-type transistor B 3 March 2009 3 3 March 2009 4 nMOS Transistor nMOS Transistor Top View • Polysilicon Gate Source n+ L Drain n+ • W p substrate n areas have been doped with donor ions of concentration ND - electrons are the majority carriers p areas have been doped with acceptor ions of concentration NA - holes are the majority carriers Bulk (Body) 3 March 2009 5 3 March 2009 6 1 nMOS Transistor nMOS Transistor Source Polysilicon Gate Drain VGS ≤ 0 Source - + + - - + + - + + + + + + + + + + + + + + + + + + + + + + + + - - Drain - - + _ Gate oxide Polysilicon Gate Accumulation Mode 3 March 2009 7 nMOS Transistor 8 nMOS Transistor Polysilicon Gate Depletion Region Drain - Polysilicon Gate VGS ≤ VT Source - 3 March 2009 - - + _ Inversion Region VGS > VT Source - - Drain - - - - + + + + + + + + + + + + + + + + + + + + + + + + Depletion Mode + _ Inversion Mode 3 March 2009 9 nMOS Transistor 3 March 2009 10 nMOS Transistor Depletion Region Polysilicon Gate Inversion Region VGS > VT Source - Drain - - - + + + + + + + + + + + + + _ n-channel enhancement MOS Inversion Mode 3 March 2009 11 3 March 2009 12 2 Threshold Voltage Threshold Voltage VT = VT 0 + γ ( − 2Φ F + VSB − 2Φ F ) • Dependent on • Gate conductor material Gate insulator material Channel Doping Voltage difference between source and body • γ is the body-effect coefficient and controls the impact of the source to bulk voltage Φ F is the Fermi potential and is dependent on doping levels • Fermi potential: potential difference between Fermi level and intrinsic Fermi level in the bulk of semiconductor. ΦF = kT N A ln q ni k: Boltzmann constant, T: temperature, q: unit (electron) charge 3 March 2009 13 pMOS Transistor 3 March 2009 14 pMOS Transistor Gate oxide Polysilicon Gate Source Drain + + - - + + - - - - - - - - - - - - Accumulation Mode 3 March 2009 15 Source vs. Drain 16 nMOS Transistor Source Drain Gate 3 March 2009 Drain Ids Source Gate Gate Ids VGS > VT Drain + _ + _ VDS < VGS - VT VDS < VGS – VT VGS – VDS > VT VGD > VT Source nMOS: node with a higher voltage is drain, VD > VS 3 March 2009 pMOS: node with a higher voltage is source, VS > VD 17 Linear mode 3 March 2009 18 3 nMOS Transistor MOS Transistor Characteristics Linear Mode: • VGS>VT and VGD>VT • Assume that VT is constant Drain Gate VGS > VT + _ + _ VDS > VGS - VT V2 I DS = kn (VGS − VT )VDS − DS 2 VDS > VGS – VT VGS – VDS < VT VGD < VT Saturation mode 3 March 2009 • • • • kn’ • 19 3 March 2009 20 MOS Transistor Characteristics Example • = ( µ nCox ) is called the process transconductance parameter Gain factor of nMOS: kn = kn’ W/L • Source Saturation Mode: • VGS>VT and VGD<VT • Assume that VT is constant µn= 600 cm2 / V s Cox = 7 x 10-8 F / cm2 W = 20 µm L = 2 µm Kn = µn Cox W/L = 0.42 mA / V2 3 March 2009 I DS = kn 21 3 March 2009 22 I-V Characteristics In Summary 6 • x 10 -4 VGS= 2.5 V Cutoff region (VGS<VT) 5 I DS = 0 I DS • Saturation Linear Linear region (VGS>VT, VDS<VGS-VT or VGD>VT ) 4 VGS= 2.0 V IDS (A) • (VGS − VT )2 2 V2 = k n (VGS − VT )VDS − DS 2 3 VDS = VGS - VT 2 VGS= 1.5 V Saturated region (VGS>VT, VDS>VGS-VT or VGD<VT ) 1 I DS = k n (VGS − VT ) 2 2 0 VGS= 1.0 V 0 0.5 1 1.5 2 2.5 VDS (V) Long channel transistor (L = 10µm) 3 March 2009 23 3 March 2009 24 4 MOS Transistor Secondary Effects Cutoff region (VGS<VT) • Body effect Channel-length modulation Drain punch-through Short channel effect Velocity saturation • D S • Linear region (VGS>VT, VDS<VGS-VT) • • • D S • Saturated region (VGS>VT, VDS>VGS-VT) • D S 3 March 2009 25 Body Effect • • • 3 March 2009 Channel-Length Modulation We previously assumed a constant L In reality, when VDS > (VGS-VT), the channel is pinched off and the effective channel length is reduced. Net effect is that IDS is not constant in the saturated region. • We assumed that VSB=0 - i.e. the source potential equals the substrate potential In certain situations, this assumption is not true Has the effect of raising the threshold voltage • 26 • • A negative bias on the well or substrate causes the threshold to increase Source VDS > (VGS-VT) 3 March 2009 27 + + + + + + + + + + + x 10 -4 VGS= 2.5 V 2 Linear region (VGS>VT, VDS<VGS-VT) VGS= 2.0 V I DS (A) 1.5 V2 I DS = kn (VGS − VT )VDS − DS 2 0.5 (V − V ) 2 = k n GS T (1 + λVDS ) 2 0 Linear Relationship VGS= 1.5 V 1 Saturated region (VGS>VT, VDS>VGS-VT) I DS - 28 Cutoff region (VGS<VT) I DS = 0 • + 3 March 2009 2.5 • - Channel-Length Modulation MOS Transistor • Drain - - VGS= 1.0 V 0 0.5 1 1.5 2 2.5 VDS (V) Short channel transistor (L = 0.25µm) 3 March 2009 29 3 March 2009 30 5 MOS Transistor • Short Channel Effect Cutoff region (VGS<VT) • D S • Linear region (VGS>VT, VDS<VGS-VT) • D S • • Saturated region (VGS>VT, VDS>VGS-VT) D S 3 March 2009 31 • 3 March 2009 32 MOS Transistor Velocity Saturation • At small gate lengths, electric field becomes more pronounced Electrons get excited with enough energy to cause a substrate current This causes change of transistor parameters threshold voltage, current flow, etc. Assumption was that carrier velocity is proportional to electric field When channel is small, and the voltage is large, the velocity can saturate • Cutoff region (VGS<VT) • Linear region (VGS>VT, VDS<VGS-VT) I DS = 0 V2 I DS = k n (VGS − VT )VDS − DS 2 µ nξ ξ < ξc µ nξ c ξ > ξ c υ = • Saturated region (VGS>VT, VDS>VGS-VT) V2 I DS = kn (VGS − VT )VDSAT − DSAT 2 ξc is value of electric field at which velocity saturates 3 March 2009 33 Velocity Saturation 3 March 2009 34 MOS Gain Characteristics ID Long-channel device • Transconductance VGS = VDD Cutoff region Linear region Saturated region gm = dI DS dVGS gm = 0 Short-channel device g m = knVDS V DSAT 3 March 2009 VGS - V T g m = k n (VGS − VT ) VDS 35 3 March 2009 36 6 pMOS I-V nMOS Transistor 0 • -0.2 VGS = -1.5V Linear region (VGSn>VTn, VDSn<VGSn-VTn) IDS (A) -0.4 V2 I DSn = k n (VGSn − VTn )VDSn − DSn 2 • -0.6 Saturated region (VGSn>VTn, VDSn>VGSn-VTn) I DSn -4 VGS = -1.0V I DSn = 0 • x 10 Cutoff region (VGSn<VTn) -0.8 (V − V ) 2 = k n GSn Tn (1 + λVDSn ) 2 3 March 2009 -1 -2.5 VGS = -2.0V Assume all variables negative! VGS = -2.5V -2 -1.5 -1 -0.5 0 VDS (V) 37 3 March 2009 38 pMOS Transistor • Cutoff region (VGSp>VTp) • Linear region (VGSp<VTp, VDSp>VGSp-VTp) I DSp = 0 V2 I DSp = − k p (VGSp − VTp )VDSp − DSp 2 • Saturated region (VGSp<VTp, VDSp<VGSp-VTp) I DSp = − k p 3 March 2009 (VGSp − VTp ) 2 2 (1 + λ VDSp ) 39 7