3.Field-Effect Transistor (FET) Junction Field-Effect Transistor (JFET) n-channel JFET V

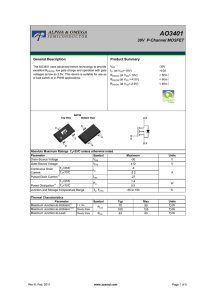

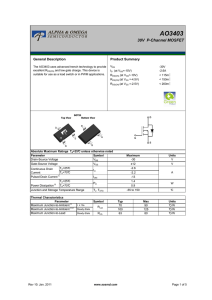

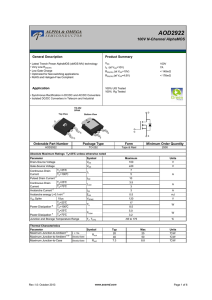

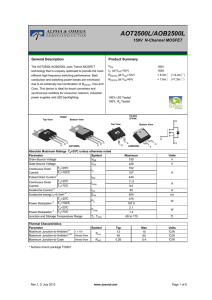

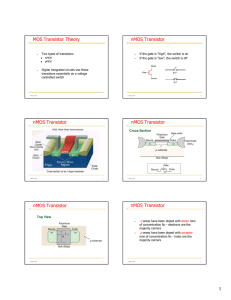

advertisement

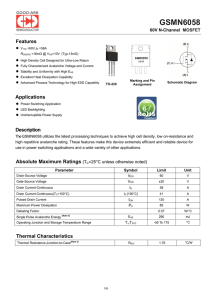

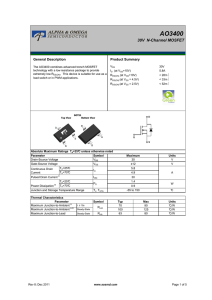

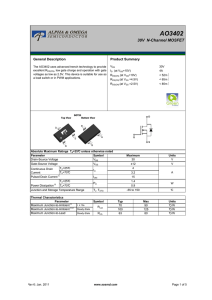

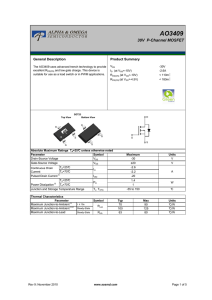

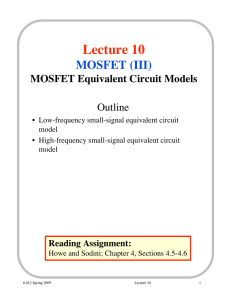

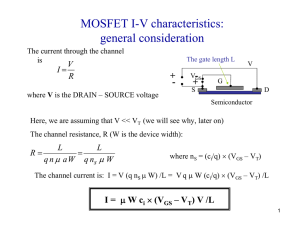

3.Field-Effect Transistor (FET) Junction Field-Effect Transistor (JFET) n-channel JFET VGS = 0 V and VDS positive value When VGS=0V and C some positive value,the upper region of the p-type material will be reverse biased higher than the lower region(the greater the reverse bias,the wider the depletion region). As the voltage VDS is increased from 0 to a few volts,the current will increase as determined by Ohm’s law and The depletion region will widen,causing a noticeable reduction in channel widht.If VDS is increased to a level where it appears that the two depletion regions would “touch”, a condition referred to as pinch-off will result.The level of VDS that establishes this condition is referred to as pinch-off voltage Vp (when VGS=0V and VDS>Vp IDSS). Input resistance > 10 8 VGS < 0V Shockley’s Equation: Voltage-Controlled Resistor: where ro is the resistance with VGS _ 0 V and rd the resistance at a particular level of VGS. Power dissipation: p-channel JFET PD = |VD|ID Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) Or Insulated-Gate FET (IGFET) Depletio-Type MOSFET (D-MOSFET) n-channel D-MOSFET When VGS=0V,the drain current is IDSS. The negative potential at the gate will tend to pressure electrons toward the p-type substrate and attract holes from the p-type substrate.The drain current is therefore reduce with increasing negative bias for VGS. The positive potential at the gate will draw additional electrons (free carrier) from the p-type substrate due to the reverse leakage current,reveals that the drain current will increase. 10 Input resistance > 10 p-channel D-MOSFET Enhachement-Type MOSFET (E-MOSFET) n-channel E-MOSFET If VGS = 0V,the absence of an n-channel will result in a current of effectively zero amperes. VD(ON) VT VGS(ON) p-channel E-MOSFET VGS Complementary MOSFET (CMOS) A very effective logic circuit can be established by contructing a p-channel and an n-channel MOSFET on the same substrate. FET Biasing For de analysis,the coupling capacitors are open cicuits. Fixed-Bias Configuration Graphical Approach: Self-Bias Configuration Graphical Approach: =-ID (1K ) Voltage-Divinder Biasing Graphical Approach: Depletion-Type MOSFET Graphical Approach: Enhancement-Type MOSFET Graphical Approach: VGS VDS VDD I D RD 12V I D (2 K) I D 0 VGS 12V VGS 0 I D 6mA I DQ 2.75mA VGS VDSQ 6.4V p-channel FET Graphical Approach: VGS VG I D RS 4.55V I D (1.8K) I D 0 VGS 4.55V VGS 0 I D 2.53mA FET Small-Signal Model V I D I DSS 1 GS VP g m y fs 2 2I DI D | VDS const DSS DVGS | VP | At VGS Q 0.5V g m VGS 1 VP V g mo 1 GS VP DI D 2 mA 3.3mS DVGS 0.6V DI D 1.8mA 2 .4 mS DVGS 0 .75V DI D 1.5mA 2.5V g m 1.4 mS DVGS 1.1V At VGS Q 1.5V g m AtVGS Q D ID ID VGS FET ac equivalent model: Output resistance: rd Input Impedance of the FET: Z i (FET ) (the typical values: JFET 109 , MOSFET 1012 1015 ) Output impedance of the FET: Z o ( FET ) rd 1 yos DVDs 7V 14k DI D 0.5mA FET Small-Signal Analysis Common-Source Circuit +VDD FET ac equivalent model: Output resistance: +VDD Vi = 0 Zo = RD ||rd RD C2 R1 C1 R2 Rs Cs Z i R1 || R2 Vo ( g mVgs )( RD || rd ) ( g mVi )( RD || rd ) Av Vo g m ( RD || rd ) Vi +VDD RD rd Vgs Vi g mVgs Rs Vi Vgs (1 g m Rs ) RG Rs Vo ( g mVgs ) RD Av Vo g R m D Vi 1 g m Rs rd Vgs Vi I o Rs D I o g mVgs Vi Vo Vs I R I R g mVgs o D o s rd rd g m (Vi I o Rs ) Vo Io Vo Vs rd Io g mVi ( R Rs ) 1 g m Rs D rd Vo I o RD Av I o RD I o Rs rd g m RDVi ( R Rs ) 1 g m Rs D rd Vo g m RD ( R Rs ) Vi 1 g m Rs D rd Common-Drain (Source-Follower) Circuit Vo g mVgs ( RS || rd ) g m (Vi Vo )( RS || rd ) Av G Vo g m ( RS || rd ) Vi 2 g m ( RS || rd ) S Z i RG Vi 0 Z o RS || rd || Common-Gate Circuit Vo ( g mVgs ) RD g m (Vi ) RD AV Z i RS || 1 gm Vi 0 Z o RD || rd Vo g m RD Vi 1 gm Enhancemen MOSFET Amplifier k I D (ON ) (VGS ( ON ) VTh ) 2 Vo ( I1 g mVgs )( RD || rd ) ( 2 (typically 0.3 mA/V ) Vi Vo g mVi )( RD || rd ) RG Vo (1 g m RG )( RD || rd ) AV Vi RG RD || rd (for g m RG 1) (for RG RD or rd g m RG ( RD || rd ) g m ( RG || RD || rd ) RG RD || rd g m ( RD || rd ) Ii Vi Vo RG Vi (1 RG Vo ) Vi Zi Vi 0 RD || rd || RG RD || rd Vi RG RG RG I i 1 AV 1 ( g m ( RD || rd )) 1 g m ( RD || rd )) System Approach-Effects of RS and RL Bypassed Source Resistance AV Unbypassed Source Resistance Source Follower Vo g m ( R L || R D ) Vi Common Gate AV Vo gm(RL || RD) Vi