2010_6_june_jain_DRC_slides.ppt

advertisement

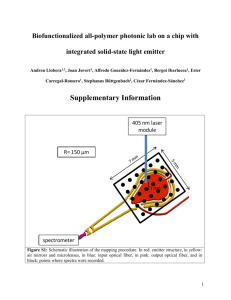

High performance 110 nm InGaAs/InP DHBTs in dry-etched in-situ refractory emitter contact technology Vibhor Jain, Evan Lobisser, Ashish Baraskar, Brian J Thibeault, Mark Rodwell ECE Department, University of California, Santa Barbara, CA 93106-9560 Zach Griffith, Miguel Urteaga Teledyne Scientific & Imaging, Thousand Oaks, CA 91360 Sebastian T Bartsch Nanoelectronics Device Laboratory, EPFL, Switzerland D Loubychev, A Snyder, Y Wu, J M Fastenau, W K Liu IQE Inc., 119 Technology Drive, Bethlehem, PA 18015 vibhor@ece.ucsb.edu, 805-893-3273 Outline • HBT Scaling Laws • Fabrication – Challenges – Process Development • DHBT Epitaxial Design • Results – DC & RF Measurements • Summary 2 Bipolar transistor scaling laws 1 tr RC 2f f max f 8Rbb,eff Ccb ,eff We Tb Wbc Tc To double cutoff frequencies of a mesa HBT, must: Keep constant all resistances and currents Reduce all capacitances and transit delays by 2 b Tb2 2 Dn Tb vexit c Tc 2v sat Ccb Ac /Tc (emitter length Le) Epitaxial scaling I c,max veff Ae (Vcb bi ) / T Rex contact /Ae 2 c We Wbc contact Rbb sheet 12 Le 6 Le Acontacts Lateral scaling Ohmic contacts 3 InP Bipolar transistor scaling roadmap 256 128 64 32 Width (nm) 8 4 2 1 Access ρ (Ω·µm2) 175 120 60 30 Contact width (nm) 10 5 2.5 1.25 Contact ρ (Ω·µm2) 75 53 37.5 Thickness (nm) Current density 9 18 36 72 mA/µm2 Breakdown voltage 4 3.3 2.75 2-2.5 V 730 1000 1400 GHz 1300 2000 2800 GHz Design Emitter Base Performance Collector 106 fτ 520 fmax 850 Evan Lobisser et al, IPRM 2009 4 Sub-200 nm HBT node: Fabrication Challenges - I Emitter yield drops during base contact, subsequent lift-off steps Fallen emitters High stress in emitter metal stack Poor metal adhesion to InGaAs Need for low stress, high yield emitters 5 Sub-200 nm HBT node: Fabrication Challenges - II Undercut in emitter semiconductor Helps in Self Aligned Base Liftoff InP Wet Etch Slow etch plane Fast etch plane Narrow emitters need controlled semiconductor undercut Thin semiconductor To prevent short, base metal needs to be thinned Higher base metal resistance Solution: Undercut in the emitter metal to act as a shadow mask 6 Composite Emitter Metal Stack W emitter TiW W Erik Lind TiW emitter Evan Lobisser • W/Ti0.1W0.9 metal stack • Low stress • Refractory metal emitters • Vertical dry etch profile 7 Junction Width via SEM, TEM M1 BCB TiW 100 nm 110 nm 200 nm SiNx W BC 100 nm emitter metal-semiconductor junction 110 nm emitter-base junction 8 In-situ Emitter Contact 35 Resistance (W) 30 25 20 15 In-situ Mo contacts* 10 c ~ 1.1 W.mm2 5 0 0 5 10 15 20 Gap spacing (mm) 25 30 • Highly doped n-InGaAs regrown on IQE InGaAs and in-situ Mo deposited • Active carriers ~ 5×1019 cm-3 • In-situ Mo deposition on n-InGaAs - c ~ 1.1 W.mm2 * • In-situ deposition repeatable contact resistivity * A. Baraskar et al., J. Vac. Sci. Tech. B, 27, 4, 2009 9 Process flow SiO2/Cr Mo SiN (SW) n+ InGaAs TiW W Mo emitter cap n InP emitter base N- collector sub collector InP substrate Regrown InGaAs emitter cap In-situ Mo dep emitter cap emitter base emitter base W/TiW/SiO2/Cr dep SiO2/Cr removal SF6/Ar etch InGaAs Wet Etch SiNx Sidewall base Second SiNx Sidewall base Base Contact Lift-off InP Wet Etch W/TiW interface acts as shadow mask for base lift off Base and collector formed via lift off and wet etch BCB used to passivate and planarize devices Self-aligned process flow for 110 nm DHBT 10 Epitaxial Design Material Doping (cm-3) Description 10 In0.53Ga0.47As 51019 : Si Regrown Cap 10 In0.53Ga0.47As 51019 : Si Emitter Cap 10 1.5 1 0.5 Energy (eV) T(nm) 0 InP 41019 : Si Emitter InP 11018 : Si Emitter InP 81017 : Si Emitter In0.53Ga0.47As 7-41019 In0.53Ga0.47 As 91016 : Si Setback 15 InGaAs / InAlAs 91016 : Si B-C Grade 3 InP 5 1018 : Si Pulse doping 74.5 InP 91016 : Si Collector 7.5 InP 11019 : Si Sub Collector 7.5 In0.53Ga0.47 As 21019 : Si Sub Collector Thin emitter semiconductor 300 InP 21019 : Si Sub Collector Enables wet etching Substrate SI : InP 10 30 25 7.5 :C Base -0.5 -1 Emitter -1.5 Base -2 Collector -2.5 0 50 100 150 200 Distance (nm) Vbe = 1 V, Vcb = 0.7 V, Je = 0, 30 mA/mm2 High collector doping High Kirk threshold 11 Results - DC Measurements 60 40 mW/mm2 50 mW/mm 50 A = 0.11mm x 3.5mm @Peak ft,fmax je 40 I b,step = 0.2 mA 30 Je = 23.1 mA/mm2 Peak ft,fmax P = 41 mW/mm2 20 V cb 10 I = 0.01 mA 10 b 1 2 V ce Solid Line: V 3 (V) 10 BVceo = 2.5 V @ Je = 1 kA/cm2 β = 18 Base ρsheet = 730 Ω/□, ρc < 4 Ω·µm2 Collector ρsheet = 12 Ω/□, ρc = 9 Ω·µm2 -4 cb Dashed Line: V cb =0V = 0.7 V Ic I c 0 -2 10 b -6 n = 3.04 b 0 =0V I , I (A) e 2 J (mA/um ) Common emitter I-V 2 b 10 10 n = 1.41 -8 c -10 0 0.2 Gummel plot 0.4 V be 0.6 (V) 0.8 1 12 Results - RF Measurements using Off-Wafer LRRM * Koolen et al., IEEE BCTM 1991 DUT Short G Open S G Standard Off Wafer LRRM Open & Short Pad Cap Extraction Ytrans ((YDUT Yopen )1 (Yshort Yopen )1 )1 13 1-67 GHz RF Data and Extrapolated Cutoff Frequencies 40 Ic = 8.9 mA MAG/MSG Gain (dB) 30 20 10 Vce = 1.74 V U H Je = 23.1 mA/mm2 Vcb = 0.7 V 21 A = 0.11mm x 3.5mm je f max = 660 GHz f = 400 GHz 0 9 10 t 10 10 10 freq (Hz) 11 10 12 Single-pole fit to obtain cut-off frequencies 14 Parameter Extraction 500 V cb 8 = 0.7 V V 400 V cb C cb t 300 200 100 0 (GHz) 5 10 15 20 25 30 35 2 J (mA/mm ) e V 5 V cb = 0.4 V 600 cb V 450 V 3 0 cb 5 = 0.7 V 10 15 20 2 J (mA/mm ) 25 30 e = 0.7 V cb max f 6 4 750 =0V Jkirk = 32 mA/mm2 (@Vcb = 0.7V) Ccb/Ic = 0.43 psec/V 300 150 =0V =0V (fF) f (GHz) 7 cb 0 5 10 15 20 25 30 35 2 J (mA/mm ) e 15 Equivalent Circuit Ccb,x = 2.97 fF Rex ≈ 3.6 Wmm2 Rcb = 31 kW Rbb = 40 W Ccb,i = 0.99 fF Rc = 2.2 W Base Col Rbe = 126 W Ccg = 3 fF S21/5 S12x5 Cje + Cdiff = 8.5 + 43.5 fF Rex = 9.4 W gme-j 0.169e(-j0.15ps) S(1,1) Emitter --- : Measured x : Simulated S11 S22 Hybrid- equivalent circuit from measured RF data 16 Microstrip Style TRL Calibration Ref Plane for TRL Ref Plane for TRL A Ref Plane set at device edge No further de-embedding required A’ t ~ 1 mm w ~ 1.7 mm Metal 1 BCB Collector Metal A – A’ h ~ 1 mm 17 140-180GHz RF data 15 Ic = 9.1 mA Gain (dB) U Vce = 1.75 V A = 0.11mm x 3.5mm je 10 H Je = 23.6 mA/mm2 Vcb = 0.7 V 21 5 f = 465 GHz f max = 660 GHz t 0 11 10 freq (Hz) 10 12 -20dB/decade fit to obtain cut-off frequencies 18 Conclusion • Demonstrated smallest junction width for a III-V DHBT (110 nm) • Peak ft/fmax = 465/660 GHz – Je = 23.6 mA/mm2 – Power Density (P) = 41 mW/mm2 • High current and power density operation (P > 50 mW/mm2) 19 Thank You Questions? This work was supported by the DARPA THETA program under HR0011-09-C-0060 and DARPA TFAST under N66001-02-C-8080. A portion of this work was done in the UCSB nanofabrication facility, part of NSF funded NNIN network and MRL Central Facilities supported by the MRSEC Program of the NSF under award No. MR05-20415