EE282 Lab 10 Objective: Sequence Detector. Write two VHDL

advertisement

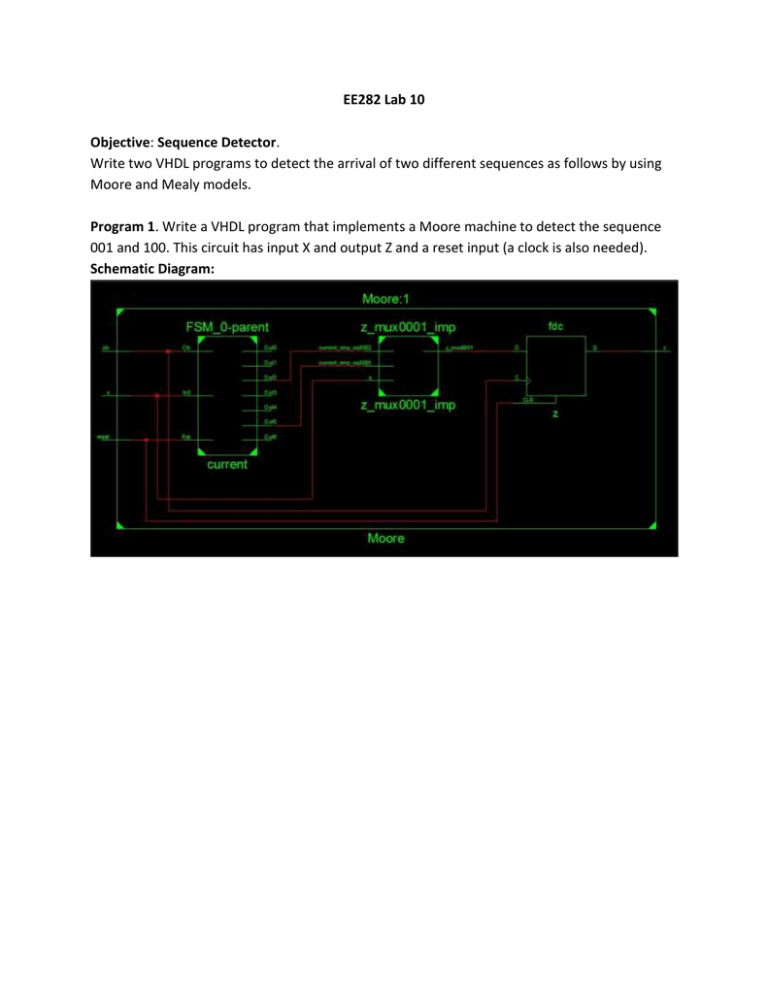

EE282 Lab 10 Objective: Sequence Detector. Write two VHDL programs to detect the arrival of two different sequences as follows by using Moore and Mealy models. Program 1. Write a VHDL program that implements a Moore machine to detect the sequence 001 and 100. This circuit has input X and output Z and a reset input (a clock is also needed). Schematic Diagram: Code: library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity Moore is Port ( clk : in STD_LOGIC; x : in STD_LOGIC; reset : in STD_LOGIC; z : out STD_LOGIC); end Moore; architecture Behavioral of Moore is type state is (ideal,s0,s00,s001,s1,s10,s100); signal current :state; begin process(clk,reset,x,current) begin if(reset='1')then current <=ideal; z <='0'; else if(rising_edge(clk))then case current is when ideal => if (x='1')then current <= s1; z <='0'; else current <= s0; z <='0'; end if; when s0=> if (x='1')then current <= s1; z <='0'; else current <= s00; z <='0'; end if; when s00=> if (x='1')then current <= s001; --whenever next state is s001 or s100 the output is HIGH z <= '1'; else current <= s00; z <='0'; end if; when s001=> if (x='1')then current <= s1; z <='0'; else current <= s0; z <='0'; end if; when s1=> if (x='1')then current <= s1; z <='0'; else current <= s10; z <='0'; end if; when s10=> if (x='1')then current <= s1; z <='0'; else current <= s100; output is HIGH z <= '1'; end if; when s100=> if (x='1')then current <= s1; z <='0'; else current <= s00; z <='0'; end if; end case; end if; end if; end process; end Behavioral; --whenever next state is s001 or s100 the Program 2. Write a VHDL program that implements a Mealy machine to detect the sequence 01110. This circuit has input X and output Z and a reset (a clock is also needed). Whenever the last five X inputs are 01110, Z goes to 1. Use a push button as the clock input, an LED as Z output, and two switches for X and reset inputs. Schematic Diagram: Code: library IEEE; use IEEE.STD_LOGIC_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity Mealy is Port ( clk : in STD_LOGIC; x : in STD_LOGIC; reset : in STD_LOGIC; z : out STD_LOGIC); end Mealy; architecture Behavioral of Mealy is type state is (ideal,zero,zero_one,zero_one_one,zero_one_one_one); signal current :state; begin process(clk,reset,x,current) begin if(reset='1')then current <=ideal; z <='0'; else if(rising_edge(clk))then case current is when ideal => z <='0'; if (x='1')then current <= ideal; else current <= zero; end if; when zero => z <='0'; if (x='1')then current <= zero_one; else current <= zero; end if; when zero_one => z <='0'; if (x='1')then current <= zero_one_one; else current <= zero; end if; when zero_one_one => z <='0'; if (x='1')then current <= zero_one_one_one; else current <= zero; end if; when zero_one_one_one => if (x='1')then current <= ideal; z <= '0'; else current <= zero; z <= '1'; --the output goes HIGH here end if; end case; end if; end if; end process; end Behavioral; -- ---------------- comments: -- ----------------ideal: sequence has not even started i.e. only 1’s are coming --zero: first zero is detected --zero_one: ‘01’ detected --zero_one_one : ‘011’ detected --zero_one_one_one : ‘0111’ detected